# MAINTENANCE MANUAL

# AUDIO SYSTEM BOARD P29/7720037000 (350A1371P20)

# **TABLE OF CONTENTS**

Page

| RCUIT ANALYSIS                                            |  |

|-----------------------------------------------------------|--|

| SWITCHING VOLTAGE REGULATOR CIRCUITS                      |  |

| +5-Volt Switching Regulator                               |  |

| -5-Volt Switching Regulator                               |  |

| MICROCONTROLLER CIRCUITS                                  |  |

| Microcontroller U56                                       |  |

| Address Latch U59                                         |  |

| Boot ROM U85 (if installed)                               |  |

| PROM U84                                                  |  |

| RAM U77                                                   |  |

| Counter U74                                               |  |

| Microcontroller Reset/Watchdog Timer U55                  |  |

| Serial EEPROM U57                                         |  |

| LOGIC INTERFACE CIRCUITS                                  |  |

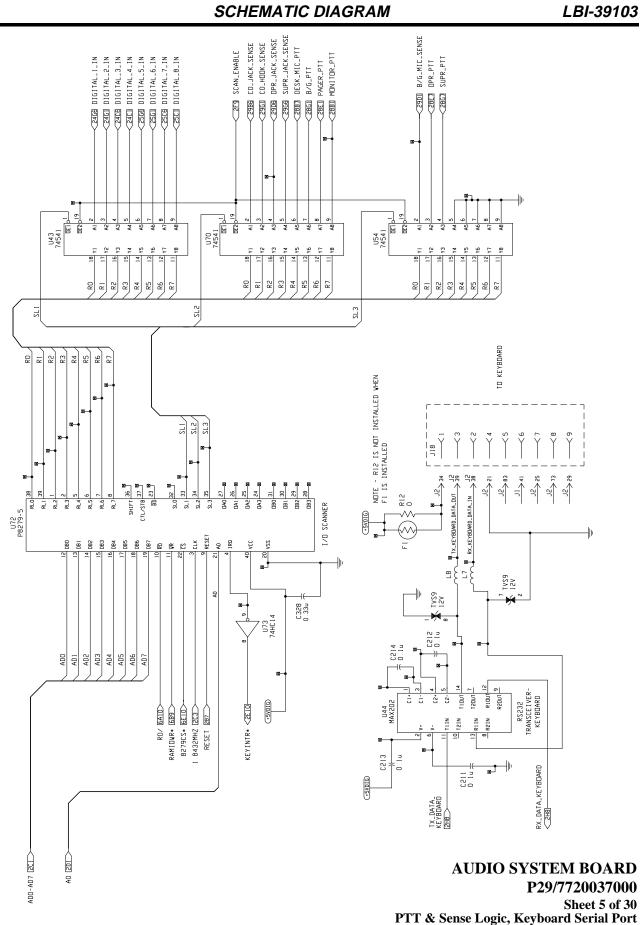

| PTT And Sense Inputs                                      |  |

| Input Scanning                                            |  |

| RS-232 Dispatch Keyboard Serial Port                      |  |

| Serial Communications Controller U71                      |  |

| AUDIO INPUT CIRCUITS                                      |  |

| Supervisor Headset Mic                                    |  |

| Operator Headset Mic                                      |  |

| Desk Mic                                                  |  |

| Boom/Gooseneck Mic                                        |  |

| Non-Supervisory Mic Audio Selection And Post-Conditioning |  |

| Line Inputs                                               |  |

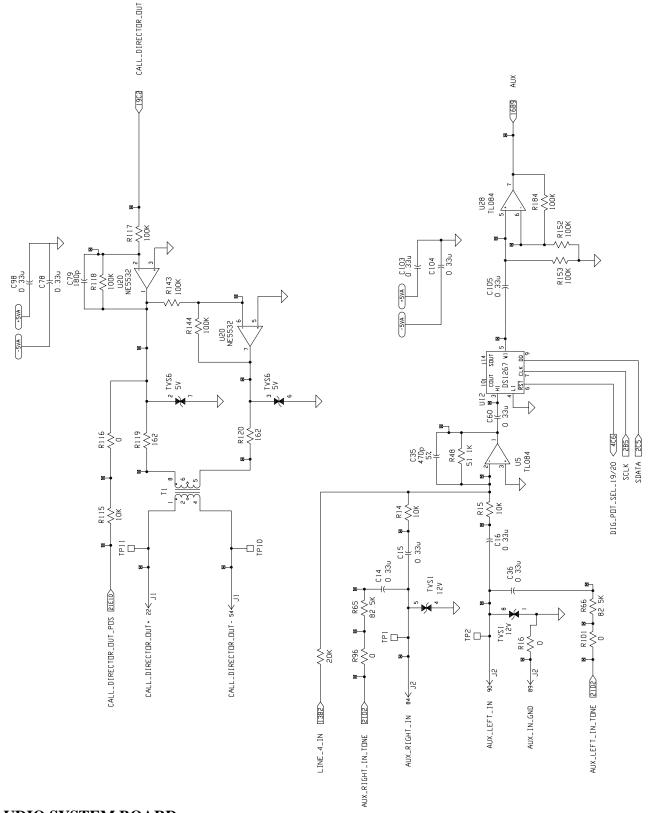

| Call Director                                             |  |

| Pager                                                     |  |

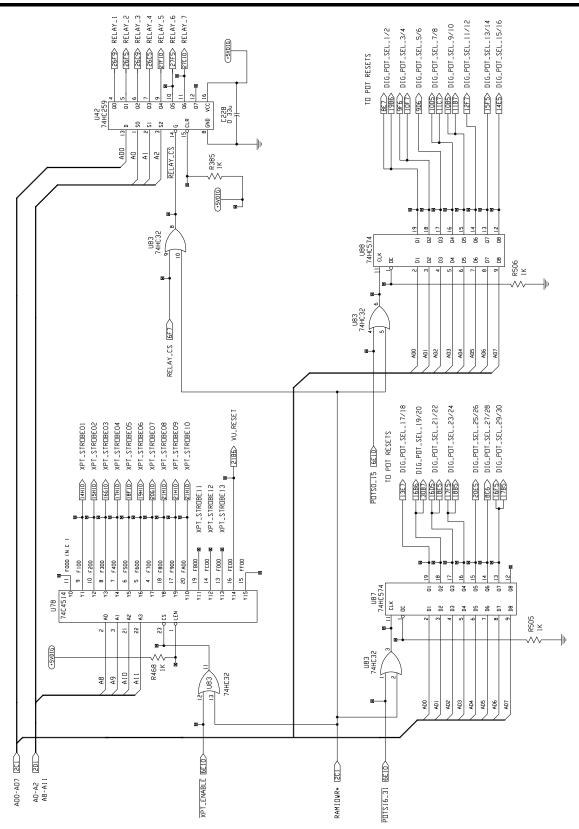

| DIGITAL POT CIRCUITS                                      |  |

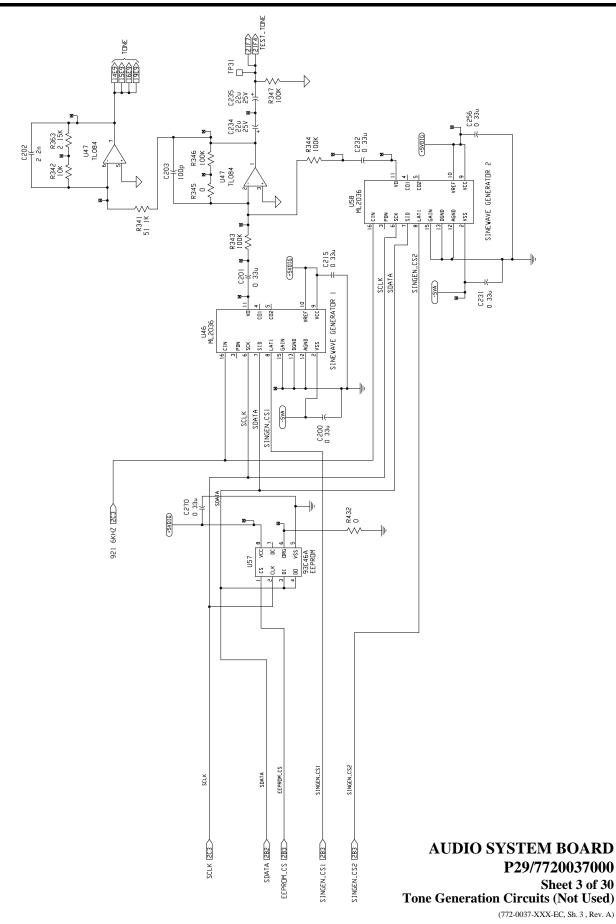

| TONE GENERATION CIRCUITS                                  |  |

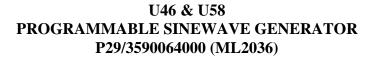

| Sinewave Generators U46 And U58                           |  |

| Summer/Buffer Op-Amp Stage                                |  |

| AUDIO MATRIX CONTROL CIRCUITS                             |  |

| Power-Up Initialization                                   |  |

| Control Logic Lines                                       |  |

| AUDIO OUTPUT CIRCUITS                                     |  |

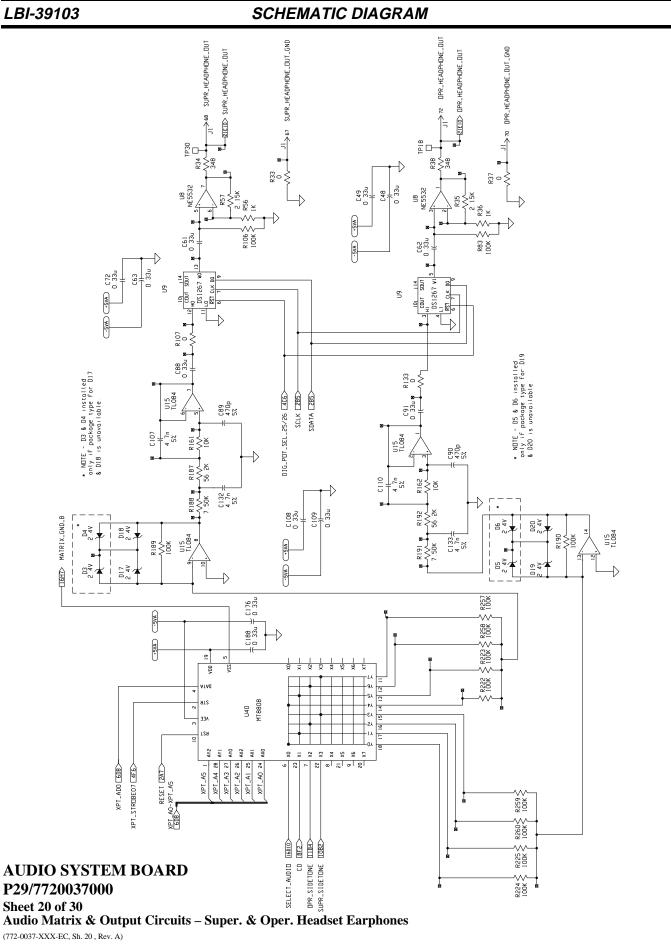

| Supervisor Headset Earphone                               |  |

| Operator Headset Earphone                                 |  |

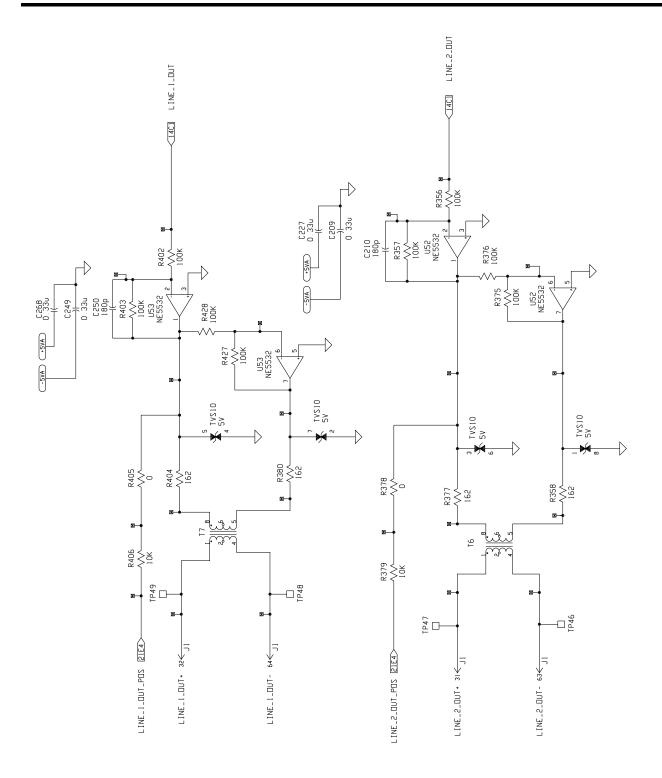

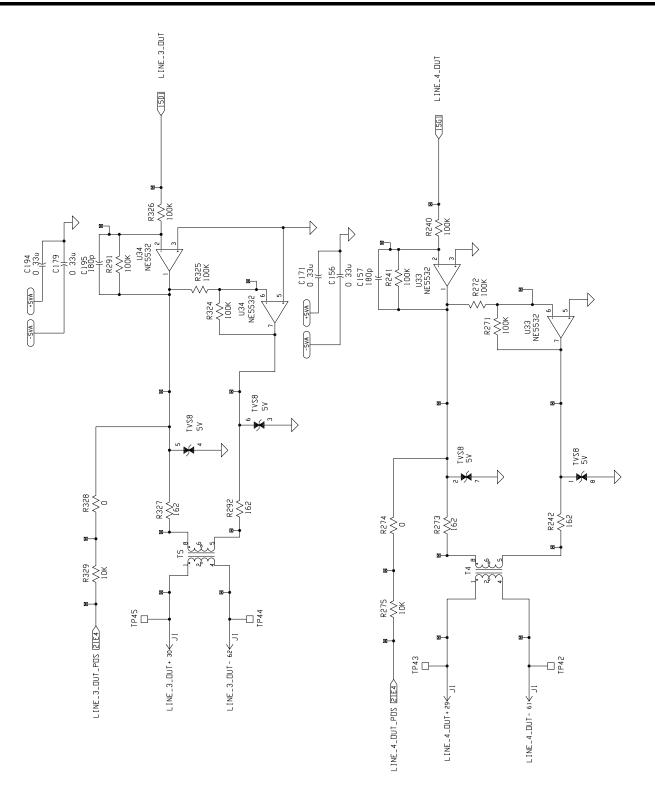

| Line Outputs                                              |  |

| Select Audio                                              |  |

| Speakers                                                  |  |

| Recorder Outputs                                          |  |

| Call Director                                             |  |

# **TABLE OF CONTENTS**

| Pa | ge  |

|----|-----|

| ıа | gu. |

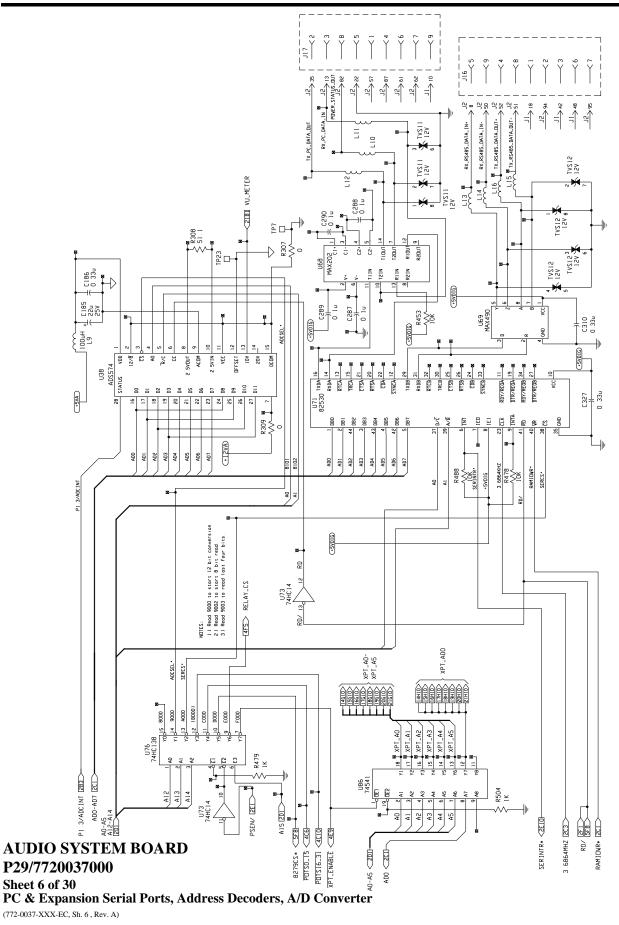

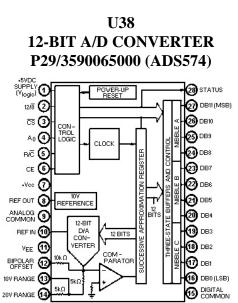

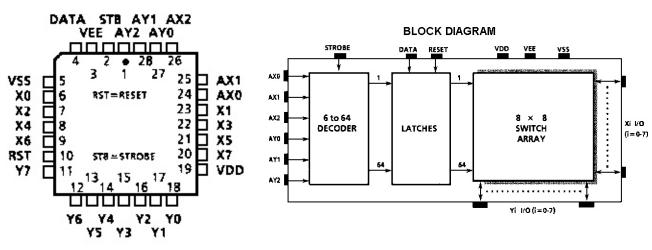

| A/D CONVERTER CIRCUIT<br>Detector                   |       |

|-----------------------------------------------------|-------|

| A/D Converter                                       |       |

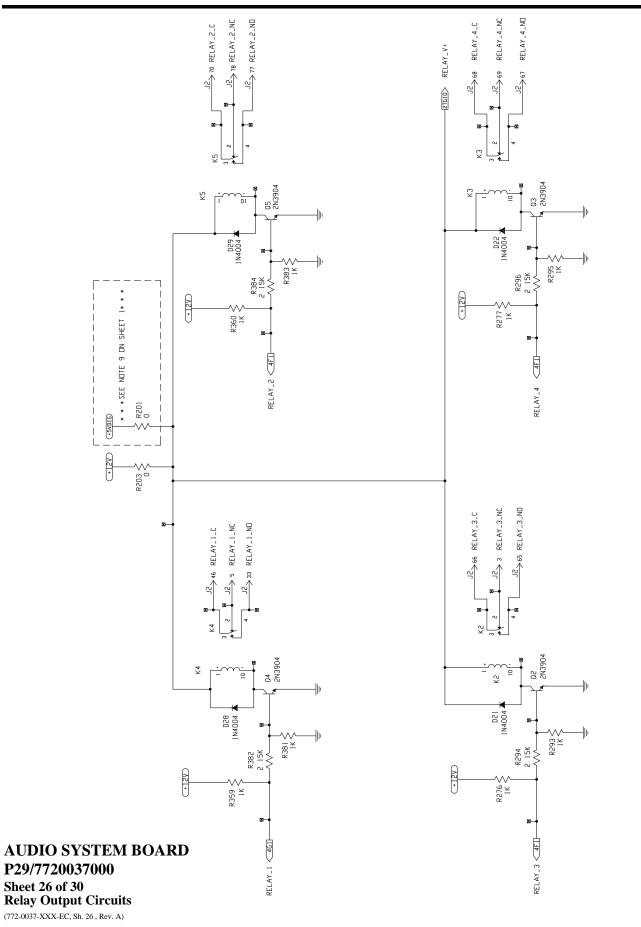

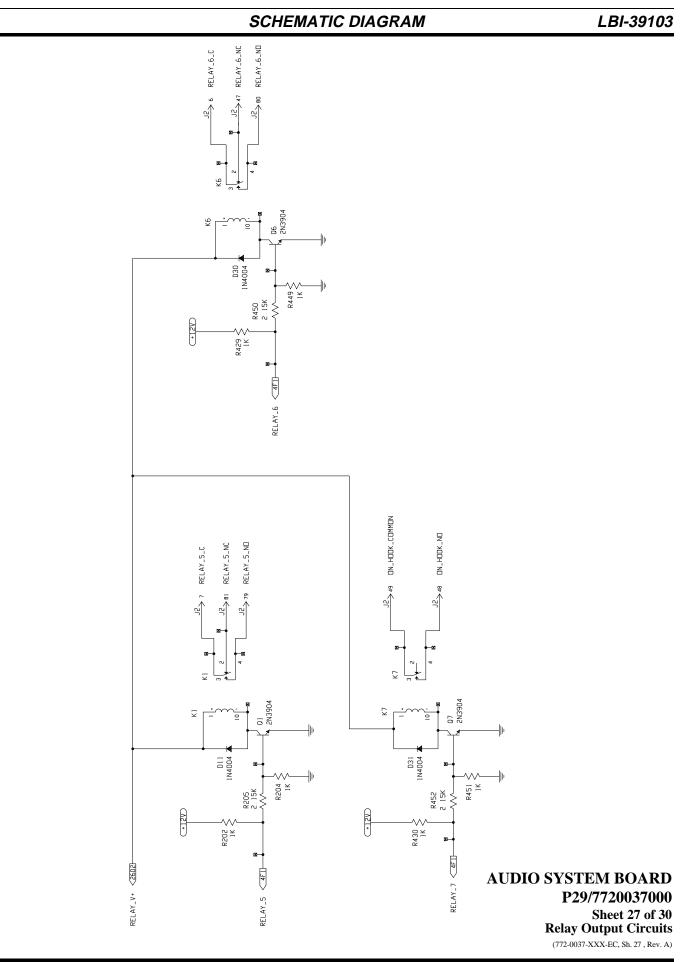

| RELAY OUTPUT CIRCUITS                               |       |

| Contacts                                            |       |

| Control                                             |       |

|                                                     | ••••• |

| STING                                               | ••••• |

| RECOMMENDED TEST EQUIPMENT                          | ••••• |

| INITIAL SET-UP                                      |       |

| Cable Disconnections & Disassembly                  | ••••• |

| Power Supply Tests                                  |       |

| Establish Serial Link With PC And Dispatch Keyboard |       |

| AUDIO INPUT CIRCUITS                                | ••••• |

| Supervisor Headset Mic Input                        |       |

| Operator Headset Mic Input                          |       |

| Desk Mic Input                                      |       |

| Boom/Gooseneck Mic Input                            |       |

| Line Inputs                                         |       |

| Call Director Input                                 |       |

| Pager Input                                         |       |

| AUDIO OUTPUT CIRCUITS                               | ••••• |

| Supervisor Headset Earphone Output                  |       |

| Operator Headset Earphone Output                    |       |

| Select Speaker Output                               |       |

| Unselect Speaker Outputs                            |       |

| Line Outputs                                        |       |

| Recorder Outputs                                    |       |

| Call Director Output                                |       |

| TLINE DIAGRAM                                       |       |

|                                                     |       |

| HEMATIC DIAGRAM                                     | ••••• |

| RTS LIST                                            | ••••• |

| DATA                                                | ••••• |

| BLES                                                |       |

| Table 1 – 80C32 Microcontroller U56 Port Usage      |       |

| Table 2 - PTT And Sense Inputs*                     |       |

| Table 3 – Digital Potentiometers                    |       |

| Table 4 – Cross-Point Switch Chips' Chip Selects    |       |

| Table 5 – Speaker Audio Sources                     |       |

| Table 6 – Relay Outputs                             |       |

Copyright© March 1995, Ericsson Inc.

# **CIRCUIT ANALYSIS**

The Audio System Board is the heart of the Enhanced Audio Enclosure. It accommodates all audio and logical processing circuitry for the Enhanced Audio Enclosure. Primary circuits include:

- Audio Input Circuits These circuits provide amplification, filtering and level-adjustment for all audio signals applied to the Enhanced Audio Enclosure's audio inputs. Input signals include mic audio signals, balanced-line audio signals from the CEC/IMC, balanced-line audio signals from Call Director patch equipment, and audio signals from a pager (or similar device).

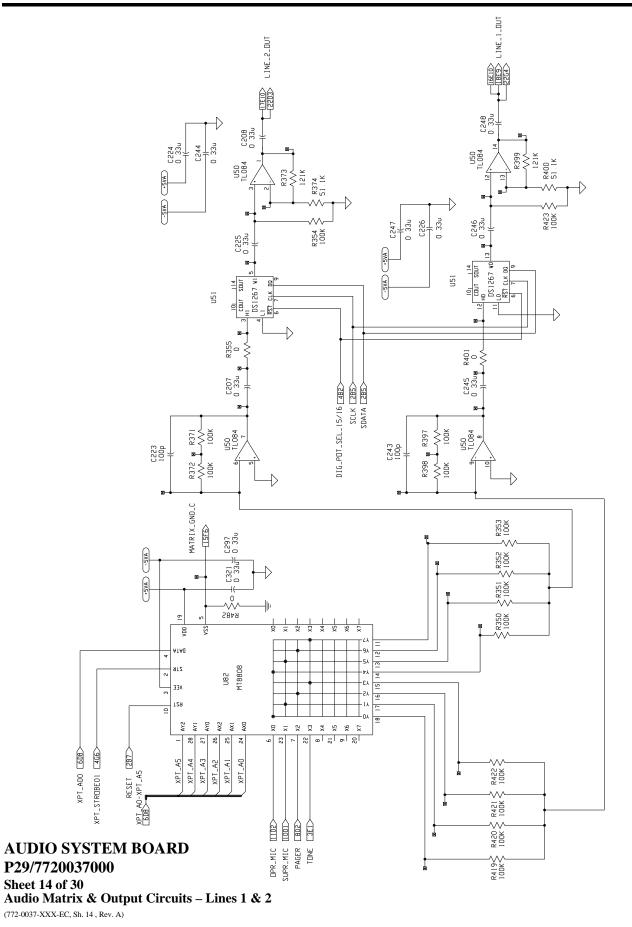

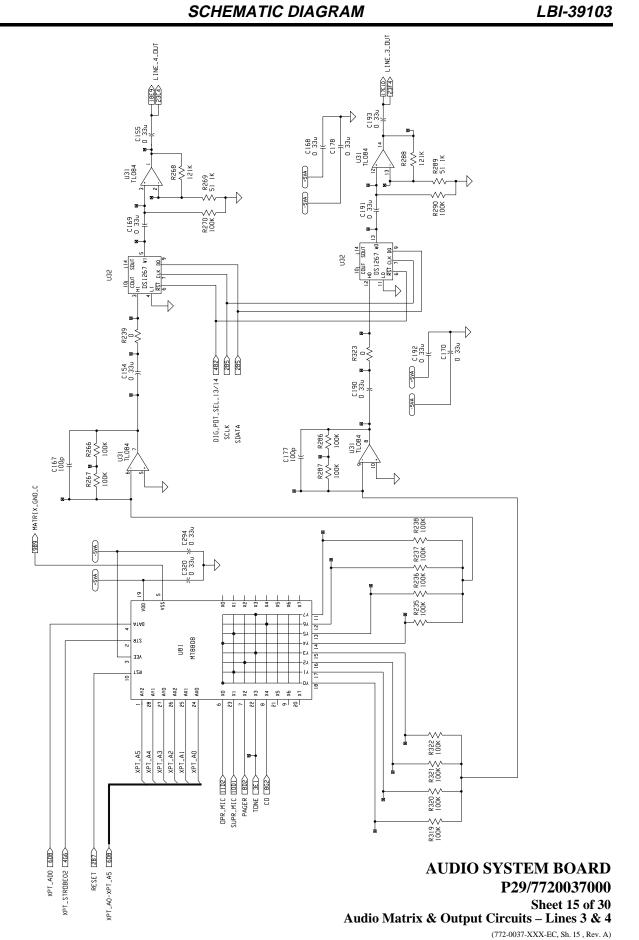

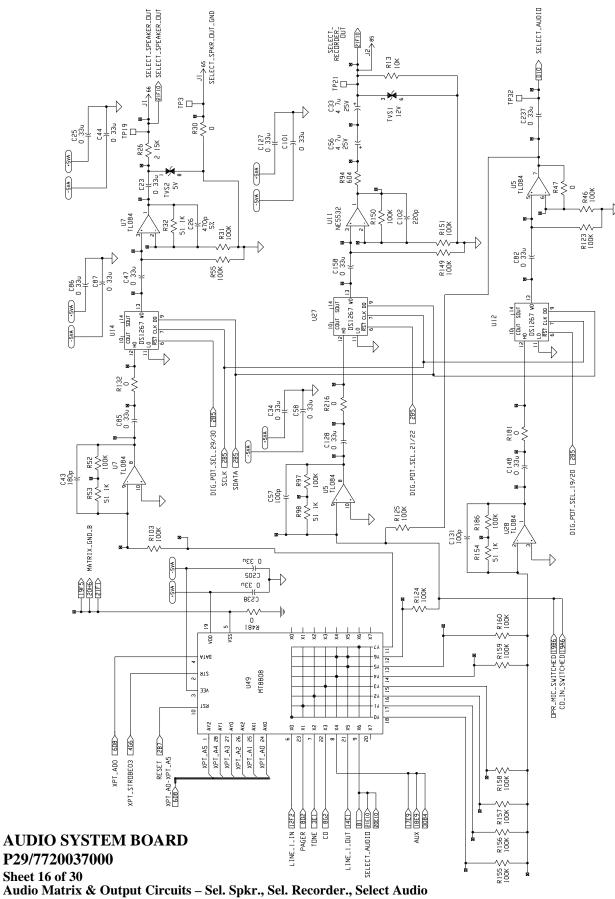

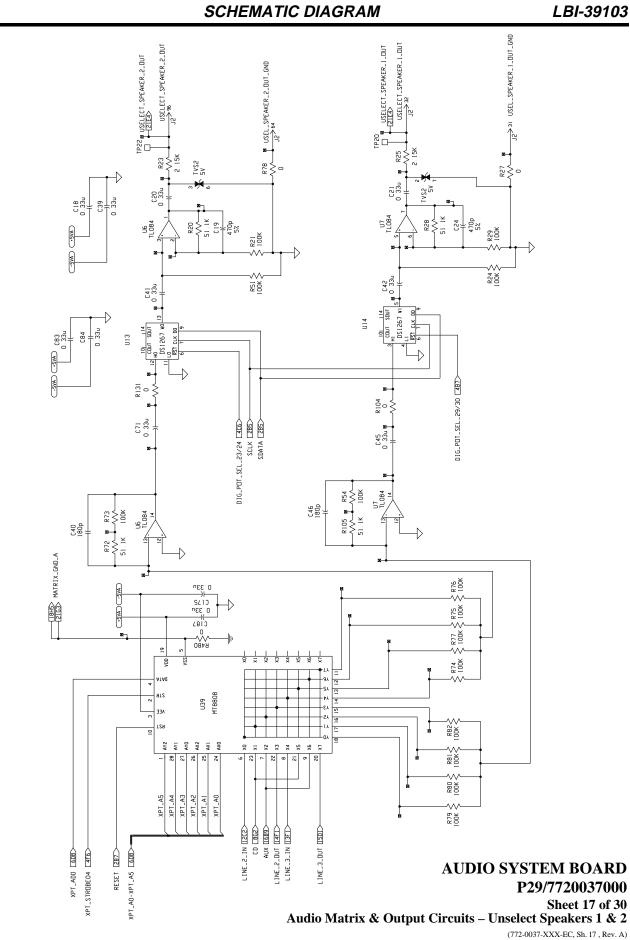

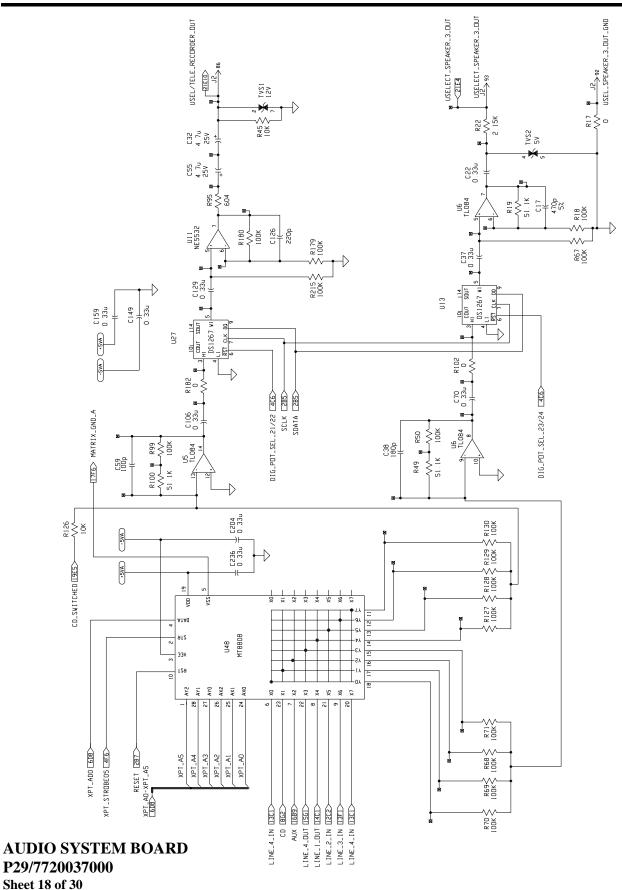

- Audio Switching Matrix Circuits The audio switching matrix routes or switches conditioned (amplified, filtered, level-adjusted) input audio signals to the appropriate audio output circuits. This matrix consists of ten (10) "cross-point switch" integrated circuits or "chips" which each have an 8 x 8 switch matrix. All console audio signals are routed through the matrix chips. Input audio signals are applied to the "x" side of the matrix and output signals are sent out from the "y" side. Audio matrix and all other logical circuitry on this board is controlled by the on-board microcontroller circuits.

- Audio Output Circuits Prior to application to the appropriate Enhanced Audio Enclosure output, each audio signal on the output side of the audio matrix (a switched-in signal) is applied to an audio output circuit. Each audio output circuit provides amplification/attenuation, impedance matching and/or level-adjustment in the output path. Output paths include headset earphone audio, low-power speaker audio ("select" and "unselect" audio), balanced-line audio signals to the CEC/IMC, balanced-line audio signals to Call Director patch equipment, and single-ended audio signals to callcheck recorders.

- **Digital Potentiometer Circuits** Digital pots are incorporated throughout the audio input and audio output circuits on the Audio System Board. There are no mechanical pots. All audio levels are 100% adjustable from Personal Computer via the serial data link and the microcontroller circuits on the Audio System Board.

- Microcontroller Circuits Intel 80C32-based microcontroller circuits on the Audio System Board control and process all logical data signals to and from the Audio System Board's I/O logic

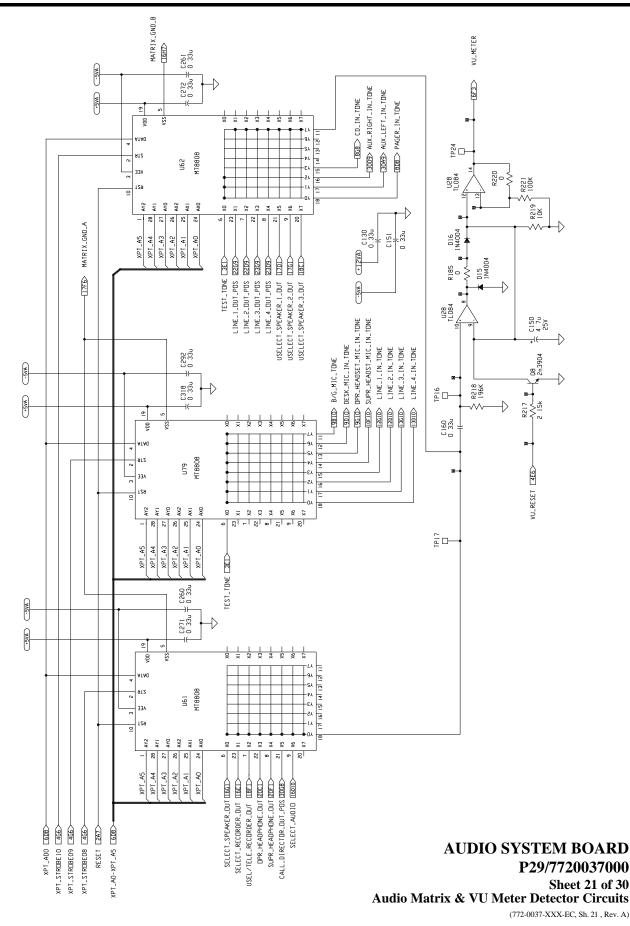

circuits. These circuits include (non-inclusive listing) the audio switching matrix, several serial ports, digital pots, bi-state logical inputs, and bistate logical outputs. The microcontroller circuits also read the on-board analog-to-digital converter circuits to provide VU meter data to the PC.

- **PC Serial Port Circuit** An RS-232 port for control data communication with the Personal Computer (PC).

- **Dispatch Keyboard Serial Port Circuit** This serial port receives keystroke data from the Dispatch Keyboard. Operating dc power is also delivered to the Dispatch Keyboard via this serial port.

- **Expansion Serial Port Circuit** An RS-422 serial port which permits control data interfacing to serially-interfaced external equipment. (Reserved for future use.)

- Bi-State Logic Input Circuits These circuits interface bi-state logical sense lines from external equipment connected to the Enhanced Audio Enclosure to the Audio System Board's microcontroller circuits. Examples include mic PTT sense lines, mic connected/not connected sense lines, Call Director off hook, and Call Director jack sense lines. Each circuit includes a pull-up resistor for the external device and lowpass filtering.

- **Bi-State Logic Output Circuits** These circuits interface the microcontroller circuits to bi-state logical outputs devices such as relay contacts. The Audio System Board has a total of seven (7) on-board relays.

- Analog-to-Digital Converter Circuit The analog-to-digital (A/D) converter circuit's primary function is to provide VU (Volume Unit) data on various Enhanced Audio Enclosure audio output signal levels. The microcontroller reads the A/D converter. It sends the read data to the PC via the serial control data link. VU indications are displayed within communication modules on the PC's monitor. The A/D converter circuit is also utilized during automated test and alignment procedures.

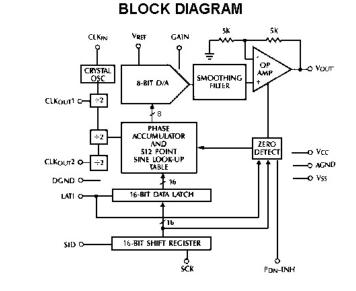

- **Tone Generator Circuits** Programmable sinewave generator chips on the Audio System Board give it the ability to generate single-tone and DTMF (Dual-Tone Multi-Frequency) tone signals. Currently, these circuits are not used and they are not supported by firmware.

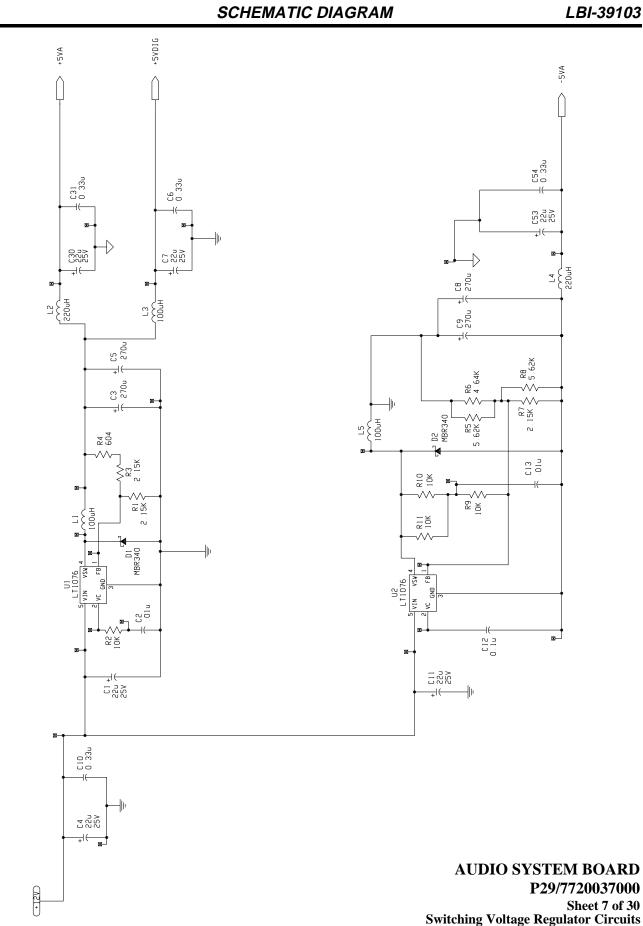

• Switching Regulator Power Supply Circuits – Switching regulator circuits on the Audio System Board convert +12 Vdc power from the Enhanced Audio Enclosure's power supply to regulated ±5 Vdc power. This bipolar power supply feeds all analog and digital circuits on the Audio System Board.

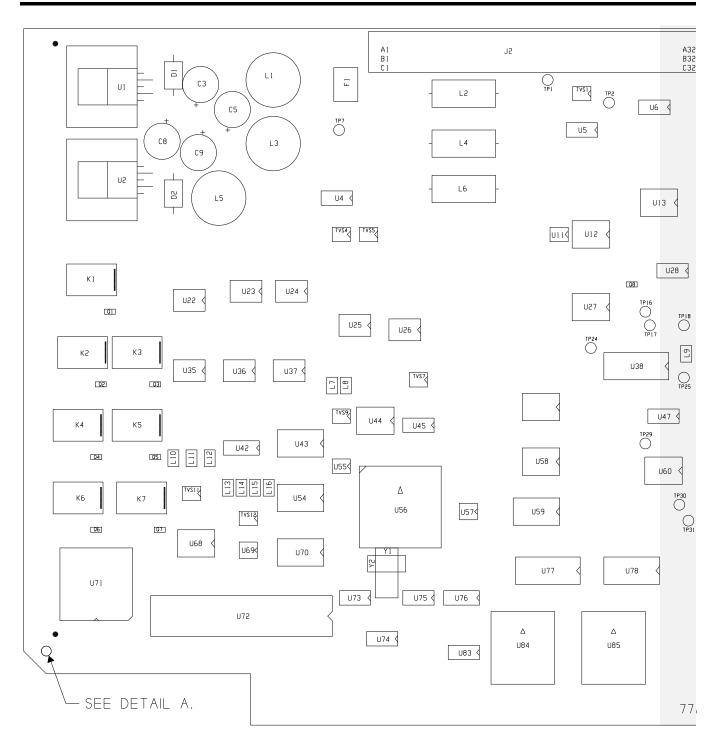

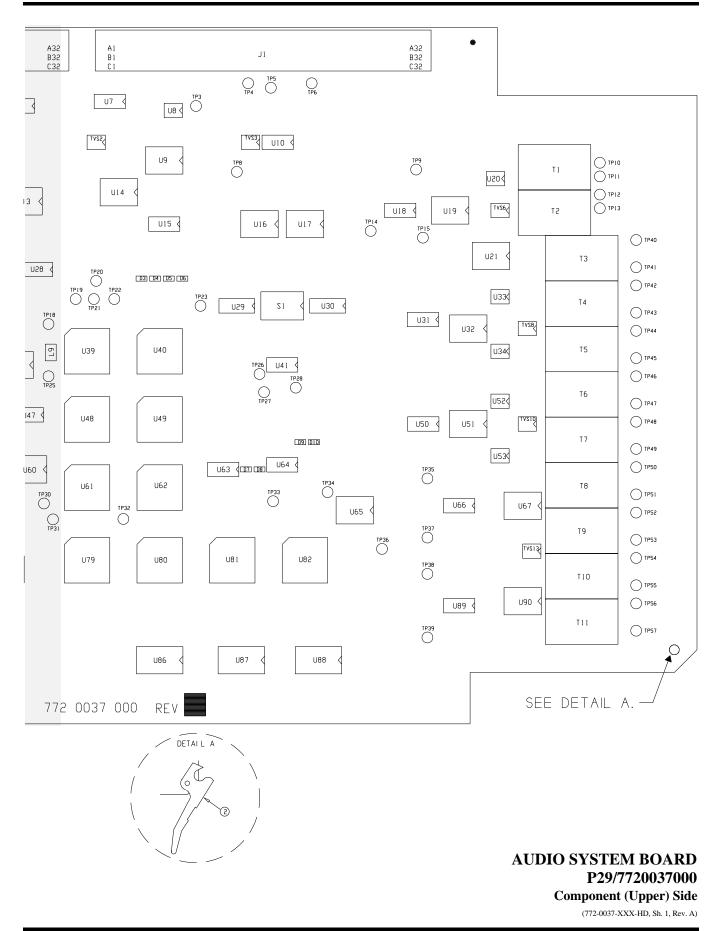

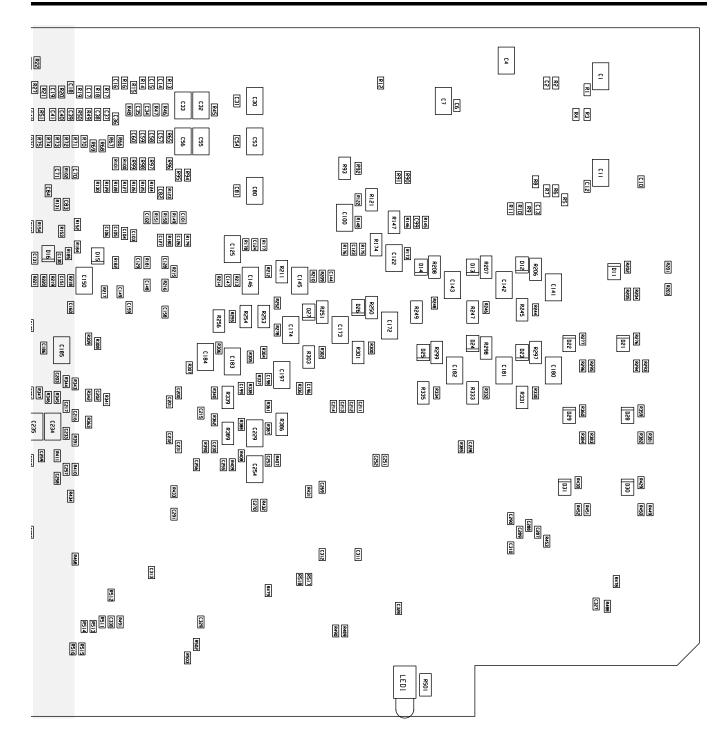

With the Enhanced Audio Enclosure's top cover removed, the Audio System Board slides into and out of the case between two (2) plastic printed circuit board guides attached to the left and right inner sides of the case. Two plastic hinge-type locking tabs located near the front corners of the board hold it in place. These tabs also provide quick board insertion and removal during maintenance procedures. The board's approximate dimensions are 14¼ x 8 inches (36.2 x 20.3 cm).

When fully-inserted, two (2) rectangular 96-pin DIN-type connectors on the Audio System Board mate with 96-pin DIN connectors on the I/O Backplane Board. Specifically, DIN connector J22 on the I/O Backplane Board mates with connector J1 on the Audio System Board and DIN connector J21 on the I/O Backplane Board mates with J2 on the Audio System Board.

# SWITCHING VOLTAGE REGULATOR CIRCUITS

Twelve-volt dc power from the power supply unit in the Enhanced Audio Enclosure is applied to the Audio System Board at J2 pins 1 and 23. From these pins, the power (+12V) is applied to the inputs of the two (2) switching voltage regulator circuits on the Audio System Board via an L-C low-pass filter network. [Audio System Board schematic diagram sheets 1 and 7.]

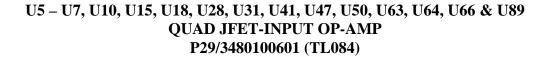

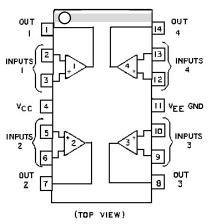

The low-pass filter network is formed by inductor L6 and capacitors C80 & C81. This network feeds filtered dc power to the regulator circuits via the +12VA line. LED1 which is visible through the Enhanced Audio Enclosure's front panel, lights when +12V power is present. As indicated in the POWER TABLE on sheet 1 of the Audio System Board schematic diagram, the filter network also feeds quad op-amp IC U28 at pin 4. [Audio System Board schematic diagram sheets 1, 16 and 21.]

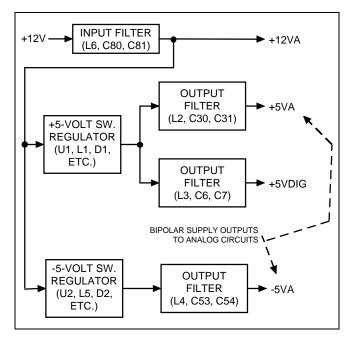

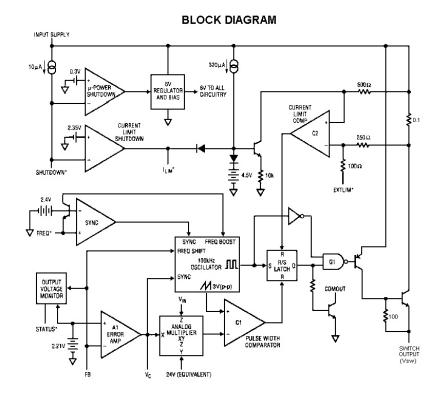

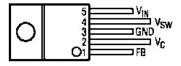

Both voltage regulators on the Audio System Board are switching regulators which are used to generate a dualpolarity or bipolar (positive and negative)  $\pm 5$  Vdc power supply from the single-polarity  $\pm 12$  Vdc input power ( $\pm 12$ V). All op-amps and the sinewave generator ICs are powered by this bipolar supply. In addition, the digital logic circuits are powered from the  $\pm 5$ V side. As shown in Figure 1, two output filter circuits are employed at the  $\pm 5$  Vdc regulator's output to provide isolation between the  $\pm 5$  Vdc analog and digital power supply lines. Each regulator circuit employs a Linear Technology LT1076 switching regulator IC (or equivalent) packaged in a 5-lead TO-220 case. These regulators feature a 2-amp maximum output capability, current limiting, and low external support component count. [Audio System Board schematic diagram sheet 7.]

Figure 1 – Audio System Board Power Supplies

### +5-Volt Switching Regulator

Integrated circuit U1 and associated components form the +5-volt switching regulator circuit. The +12 Vdc input is located at U1 pin 5. This IC operates in a positive buck converter mode with L1 being the driven inductor and Schottky diode D1 providing a clamp function when U1 turns off. Divider resistors R1, R3 and R4 produce a 2.2 Vdc feedback voltage at U1's feedback input, pin 1. C1, C3 and C5 provide filtering and decoupling functions. [Audio System Board schematic diagram sheet 7.]

The +5 Vdc regulated output from U1 is applied to two separate L-C output filter circuits. L2, C30 and C31 output +5 Vdc filtered supply power for the board's analog circuits (+5VA). This is the positive side of the bipolar power supply. L3, C6 and C7 output +5 Vdc filtered power for the digital circuits (+5VDIG). Digital and analog grounds are isolated starting at these filters. See the POWER TABLE on sheet 1 of the schematic diagram for +5VA and +5VDIG power supply distributions to the integrated circuits.

### -5-Volt Switching Regulator

The -5-volt switching regulator is formed by U2 and associated components. This regulator stage converts the positive 12 Vdc input power to -5 Vdc power for use by the op-amps and other analog circuits on the board. As with the +5-volt regulator, 12 Vdc from the power supply (+12V) is applied to pin 5. L5 is the driven inductor and Schottky diode D2 provides clamping when the switching regulator turns off. Divider resistors R5 thru R8 produce a 2.2 Vdc feedback voltage at U2's feedback input. R9 thru R11 and C13 provide frequency compensation. C8 and C9 provide filtering and decoupling at the output and C11 provides decoupling at the regulator's input. [Audio System Board schematic diagram sheet 7.]

The -5 Vdc regulated output power from U2 is applied to an L-C filter network comprised of L4, C53 and C54. This filter circuit outputs the -5 Vdc analog power supply line which is identified as -5VA. This supply line is the negative side of the bipolar power supply. See the POWER TABLE on sheet 1 of the Audio System Board's schematic diagram for -5VA distribution details.

# MICROCONTROLLER CIRCUITS

Microcontroller circuits on the Audio System Board perform the following principal functions for the Enhanced Audio Enclosure:

- interfacing to the Personal Computer (PC) via a serial port

- interfacing to the Dispatch Keyboard via a serial port

- microphone PTT sensing for all microphones

- microphone connected/not connected sensing

- cross-point matrix chip switching for the ten (10) on-board cross-point switch chips per PTTs from currently connected microphone(s), messages received from PC, etc.

- frequency control of the two (2) tone generator circuits (currently not used and supported by firmware)

- digital potentiometer setting control

- analog-to-digital (A/D) converter circuit reading

- interfacing to Call Director patch equipment

- output control of the relay outputs

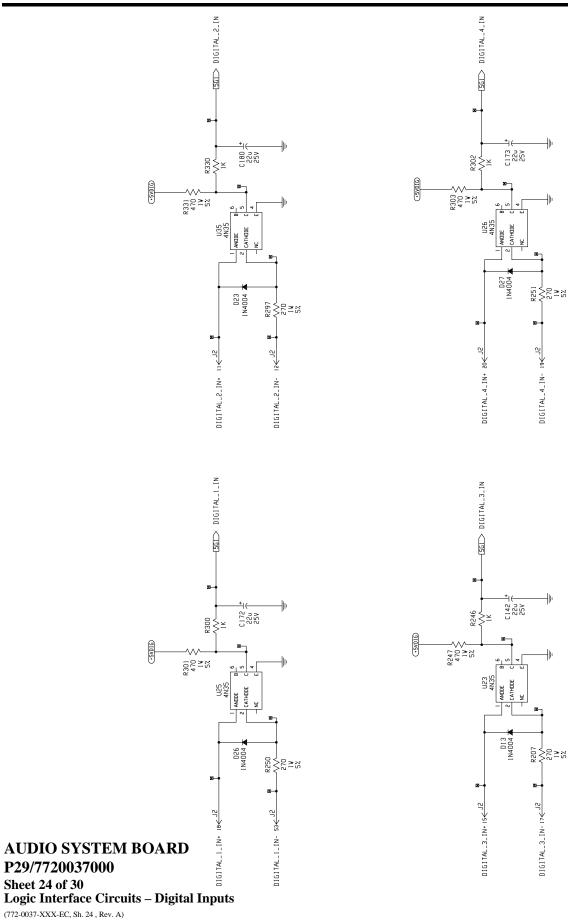

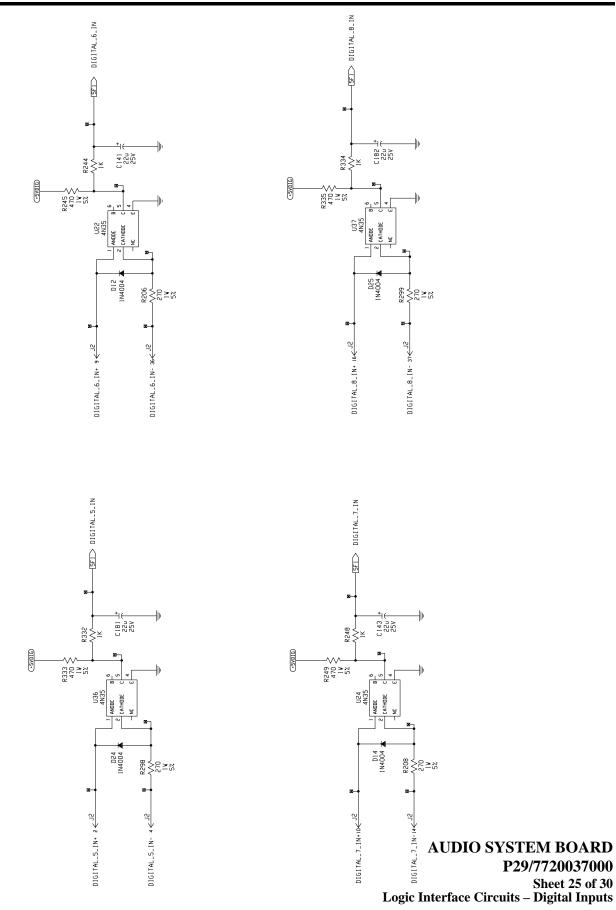

- input control of the digital optocoupler inputs (currently not used and not supported by firmware)

### **Microcontroller U56**

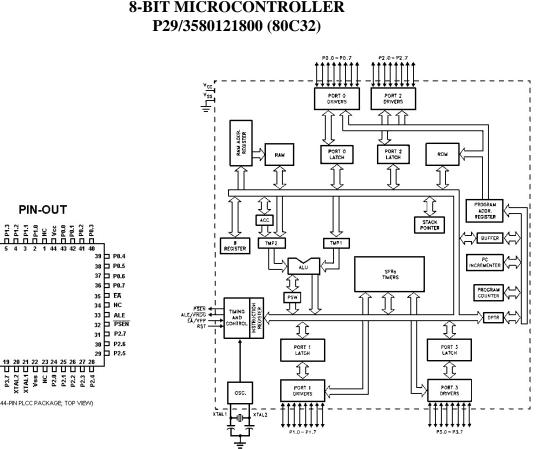

Microcontroller U56 is an Intel® 80C32 (or equivalent) 8-bit microprocessor which provides all processing power for the Audio System Board. Features of this chip utilized in the Enhanced Audio Enclosure include 64K bytes of external program memory storage addressing (ROM), 64K bytes of external data memory storage addressing (RAM; 32K of 64K used), a programmable serial communications port, and 16-bit timers/counters. [Audio System Board schematic diagram sheet 2.]

Specifically, the memory map includes 32K bytes of RAM, 8K bytes of boot ROM (normally only installed for flash applications), and either 64K bytes of one-time programmable ROM (non-flash applications) *or* 56K bytes of flash EEPROM. Firmware is stored in the ROM chip(s). If installed, the boot ROM may either be an 8K or 16K byte chip. Some boards do not use the boot ROM in which case the boot-up code is stored in the one-time programmable ROM.

The 80C32's port usage is detailed in Table 1. These ports provide both memory and I/O interfacing.

Table 1 – 80C32 Microcontroller U56 Port Usage

| PORT | USE                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------|

| 0    | multiplexed: low address byte output (A0 - A7)<br>and bidirectional data bus (D0 - D7)              |

| 1    | serial device control (digital pots, EEPROM)<br>and sinewave generator control                      |

| 2    | high address byte output (A8 - A15)                                                                 |

| 3    | single-line I/O control logic lines, serial comm<br>port, interrupts and memory control logic lines |

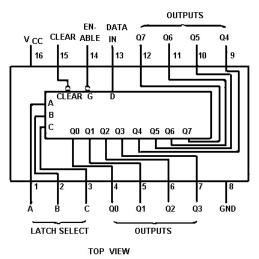

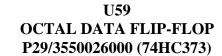

### Address Latch U59

As indicated in Table 1, microcontroller U56 incorporates a multiplexed 8-bit wide address and data bus at port 0 (pins 36 - 43). This port transfers both the lower address byte to external memory and 8-bit bidirectional data to and from external memory and I/O devices. Before U56 can read or write data, it must first latch the lower address byte to the Q outputs of octal data latch U59. [Audio System Board schematic diagram sheet 2.]

To latch the lower address byte, U56 first outputs the byte at port 0. It next pulls its ALE (address latch enable) logic line at U56 pin 33 low. The byte remains latched on U59's Q outputs until the external data read or write is completed via port 0, at which time, U56 brings ALE back

to a high state. This sequence repeats upon subsequent memory or I/O reads and writes.

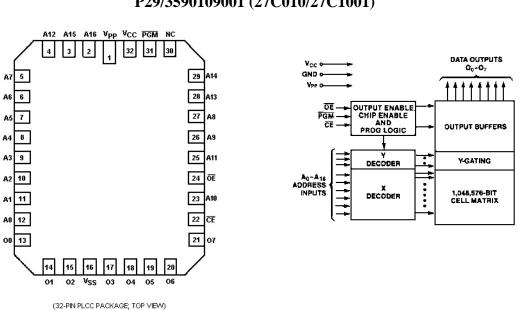

### **Boot ROM U85 (if installed)**

Boot ROM U85 is typically an EPROM chip. If installed, it stores the initialization and other low-level portions of the Audio System Board's operating program such as interrupt jump vectors. The installed chip may be either an 8K x 8-bit (2764 or equivalent) or a 16K x 8-bit (27128 or equivalent) device. U85 is mapped into the 0000 hexadecimal (0 decimal) to 1FFF hexadecimal (8191 decimal) program storage memory range of microcontroller U56 as described in the following paragraph. [Audio System Board schematic diagram sheet 2.]

Fourteen (14) address logic lines (A0 – A13) are applied to U85. With current chip enable decoding logic, address logic line A13 is never used by U85; it is wired to the ROM chip for future memory expansions, if required. Two (2) OR gates (part of U75) generate the BROMCS/ logic line for U85 by "ORing" the three (3) highest address lines (A13 – A15) from the 80C32. BROMCS/ is an activelow boot ROM chip select logic line which enables U85 during boot ROM reads via its active-low chip enable input at pin 23. BROMCS/ is active (low) only when address logic lines A13 thru A15 are all low. This maps the boot ROM into U56's 0000H to 1FFFH (hexadecimal) address space. BROMCS/ is always inactive (high) any time U56 addresses an external memory byte at 2000H or above.

After the address is set during a boot ROM read, microcontroller U56 next pulses its program store enable output (pin 32) low. This enables U85's data bus output buffers via its active-low output enable logic input at U85 pin 25. U56 then reads the boot ROM data byte at the addressed location.

### <u>PROM U84</u>

PROM U84 stores the majority of the Audio System Board's operating program (firmware) *or*, in cases where the boot ROM U85 is *not* installed, *all* of the operating program is stored within U84. The installed PROM may either be a one-time programmable ROM chip or, for flash applications, a flash EEPROM. Current firmware does not support flash programming.

In either case, the 64K x 8-bit PROM is mapped into the microcontroller's program storage memory address space from 2000H (8192 decimal) to FFFFH (65,535 decimal). All sixteen (16) address lines are applied to U84 – A0 thru A15. [Audio System Board schematic diagram sheet 2.] U84 chip selection is accomplished in one of the following methods based upon the installed/not installed status of boot ROM U85:

- If boot ROM U85 is installed, chip selection for U84 is generated by simply inverting the BROMCS/ logic line via an inverter within U73 (pins 1 & 2). In this case, jumper R502 is installed and jumper R503 is *not* installed. The inverted line, FPROMCS/, pulls U85's chip enable input low whenever microcontroller U56 addresses any memory location at 2000H or above.

- In cases where U85 is not installed, jumper R503 is installed and jumper R502 is *not* installed. This pulls U84's active-low chip enable input low at all times.

Microcontroller U56 reads U84 by pulsing its program store enable (PSEN/) logic line low. This microcontroller output is also applied to boot ROM U85 (if installed) and to I/O address decoder U76. [Audio System Board schematic diagram sheets 2 and 6.]

During normal program operations, the EE/RAM\* logic line from U56 pin 9 remains low. However, when U84 is flashed programmed, microcontroller U56 pulls EE/RAM\* high. EE/RAM\* and theactive-low write enable logic line from U56 pin 18 (WR/) are decoded by inverter U73 (pins 3 & 4) and OR gate U75 (pins 8, 9 & 10). The resultant decoded output, FPROMWR\*, transitions low when U56 writes a flash byte to U84.

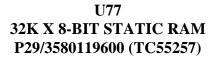

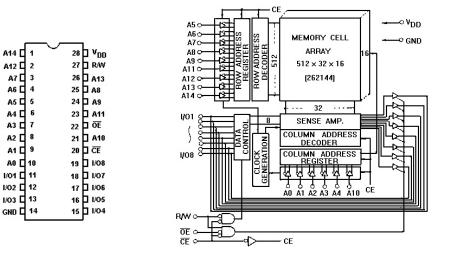

### **RAM U77**

RAM chip U77 provides 32K bytes of volatile static random access memory for the Audio System Board. This chip is mapped into the 0000H (0 decimal) to 7FFFH (32767 decimal) range of microcontroller U56's read/write memory space. Address logic lines A0 thru A14 are applied to U77's address inputs and A15 is tied to its active-low chip select logic line. [Audio System Board schematic diagram sheet 2.]

During normal (non-flash) operations, microcontroller U56 keeps the EE/RAM\* logic line at U56 pin 9 low. OR gate U75 (pins 11, 12 & 13) ORs the EE/RAM\* logic line with the active-low write enable logic line from U56. The resultant RAMIOWR\* logic line is applied to the active-low write enable input of U77 at pin 27. Accordingly, RAMIOWR\* pulses low when U56 writes a byte to the RAM.

RAMIOWR\* is also used by several memory-mapped I/O chips which are addressed by I/O address decoder U76 and additional OR gates. [Audio System Board schematic diagram sheets 4, 5 and 6.]

During a RAM byte read, U56 pulses its active-low read logic line (pin 19) low. This enables the data bus output buffers within U77 via its output enable logic input line at U77 pin 22. RAMIOWR\* remains high during the RAM read.

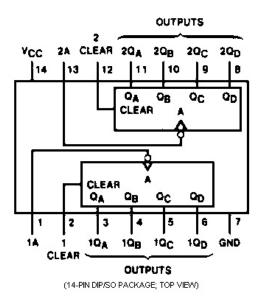

# Counter U74

Integrated circuit U74 is a dual 4-bit binary counter which generates several reference clocks from the microcontroller's 14.7456 MHz clock. U74 pins 4, 5 and 6 output divided-by 4, 8 and 16 clocks respectively. The 3.686 MHz (÷ 4) output is applied to the clock input of serial communications controller U71 and the 1.8432 MHz (÷ 8) output is applied to the clock input of I/O scanner U72. The 921.6 kHz clock (÷ 16) output drives the clock inputs of both sinewave generator chips, U46 & U58. [Audio System Board schematic diagram sheets 2, 3, 5 and 6.]

In addition, the 921.6 kHz clock output is applied to the clock input of the second counter within U74. This second counter's divided-by 16 output at U74 pin 8 is applied back to the microcontroller at U56 pin 16. When required, U56 can read these 57.6 kHz pulses and generate long time delays via software counters. [Audio System Board schematic diagram sheet 2.]

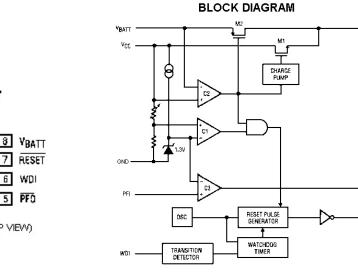

### Microcontroller Reset/Watchdog Timer U55

Integrated circuit U55 is a microprocessor supervisory chip that performs power-up reset and "watchdog" timer functions for microcontroller U56. Resets generated by this chip also reset other logic circuitry on the Audio System Board. [Audio System Board schematic diagram sheet 2.]

At power-up, U55 holds its reset output at pin 7 low until approximately 50 milliseconds *after* the +5VDIG power supply line stabilizes. Therefore, via inverter U73 (pins 5 & 6), the RESET logic line is held high for the same time interval. The Audio System Board is in a reset (non-operating) state when RESET is high.

U55 will also reset the microcontroller and other logic circuits on the Audio System Board if the microcontroller fails to periodically pulse U55's watchdog input or if the +5VDIG power supply line falls out of regulation. U55's watchdog input is located at pin 6 and +5VDIG voltage sensing is accomplished via the chip's power pin (U55 pin 2).

If U55 pin 6 remains low or high for more than 1.6 seconds, the watchdog timer will time-out and an active-low reset pulse will appear at U55 pin 7. This produces an active-high reset pulse at the output of inverter U73, the RESET logic line for the entire board. RESET is applied to

the microcontroller's reset logic line at U56 pin 10 and to various other logic circuits on the board.

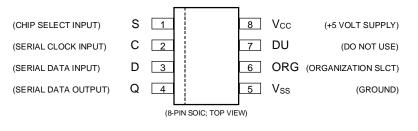

### Serial EEPROM U57

Integrated circuit U57 is a serially-accessed EEPROM (Electrically Erasable Programmable Read Only Memory) that provides 128 bytes of non-volatile memory storage for the Audio System Board. In this application, its stores data such as digital pot settings and other initialization values required at board power-up. [Audio System Board schematic diagram sheet 3.]

Microcontroller U56 writes data to and reads data from U57 using the SCLK (serial clock), SDATA (serial data) and EEPROM\_CS (EEPROM chip select) logic lines. These lines are located between U56's port 1 and U57's serial I/O pins. SDATA is a bidirectional data logic line and SCLK provides clock pulses for the synchronous serial data transfers. EEPROM\_CS basically provides a strobetype function before and after data activity on SDATA. [Audio System Board schematic diagram sheets 2 and 3.]

SCLK and SDATA are also used to load frequency data into the sinewave generator chips and pot settings into the digital pots. These processes are described in subsequent sections of this manual.

# LOGIC INTERFACE CIRCUITS

# **PTT And Sense Inputs**

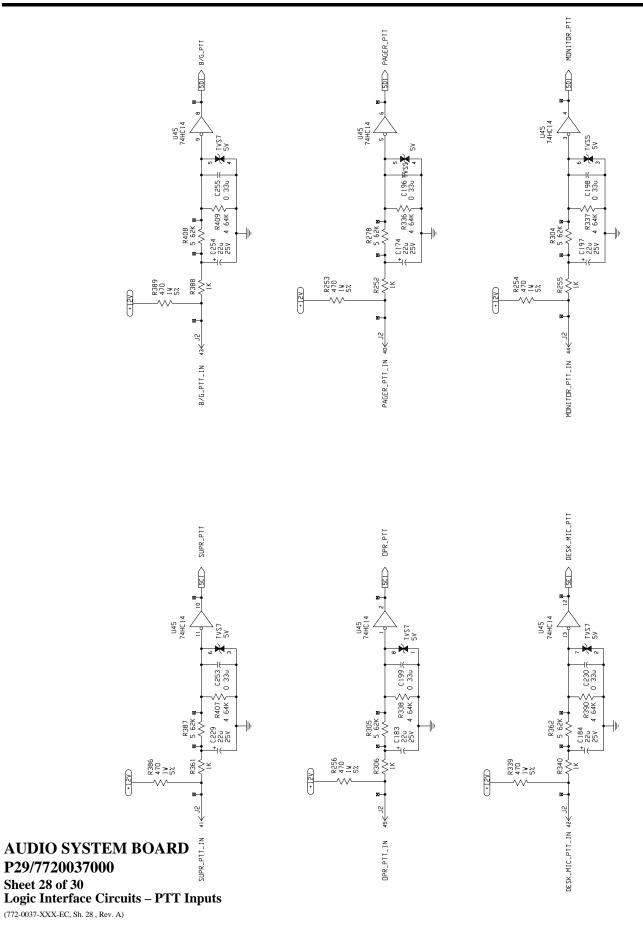

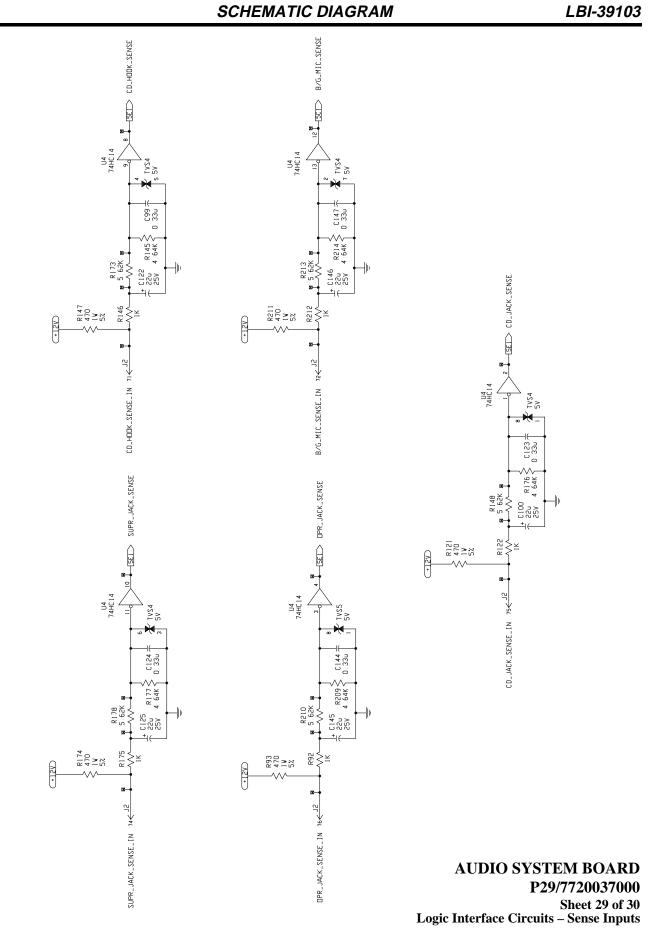

Eleven (11) identical logic input buffers circuits are located on the Audio System Board. Each circuit interfaces a PTT or sense logic line from the rear panel of the Enhanced Audio Enclosure into the Audio System Board's microcontroller circuits. PTT buffers are shown on sheet 28 of the schematic diagram and sense buffers are shown on sheet 29. A logic input line becomes active when it is pulled low by an external device. For example, DESK\_MIC\_PTT\_IN (J2 pin 42) is pulled low by the switch in the desk mic when the desk mic's PTT button is depressed. Sense logic lines provide connected/not status for the headsets, microphones. In addition, two (2) sense inputs are used for Call Director patch status interfacing.

Enhanced Audio Enclosure PTT and sense inputs originate from the connectors at the rear panel. All are routed through the I/O Backplane Board to Audio System Board connector J2. J2 is a 96-pin rectangular DIN connector that mates with I/O Backplane Board connector J21. The I/O Backplane Board contains no active or passive components, only connectors.

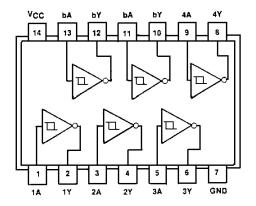

On the Audio System Board, each logic input buffer circuit consists of a pull-up resistor, an R-C low-pass filter network, a surge suppression diode and an Schmitt trigger

inverter. Each low-pass network provides a switch contact debounce function for its input. It also prevents induced charges such as static electricity from falsely triggering the input. Buffer circuit input and output schematic diagram labeling is given in Table 2.

The Schmitt triggers are located within hex inverters U45 (PTT inputs) and U4 (sense inputs). All eleven (11) inverter outputs are applied to the microcontroller's input scanning circuitry described in the following section. [Audio System Board schematic diagram sheet 5.]

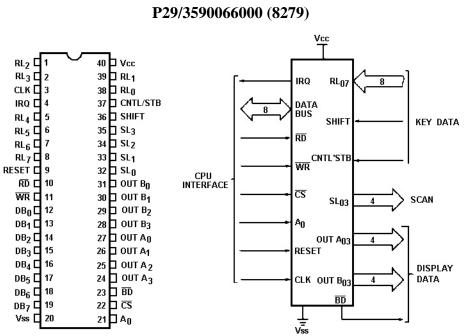

### **Input Scanning**

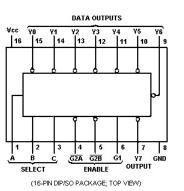

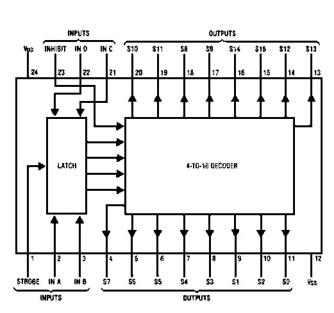

Integrated circuit U72 is an Intel® 8279 (or equivalent) keyboard/display interface chip. In the Enhanced Audio Enclosure, this chip is used only for input scanning functions. It scans a total of nineteen (19) Enhanced Audio Enclosure logic inputs. When a logic change occurs in one, it interrupts microcontroller U56 so the change can be read by U56. At power-up, microcontroller U56 programs U72 to operate in an 8279 "scanned sensor matrix mode". [Audio System Board schematic diagram sheet 5.]

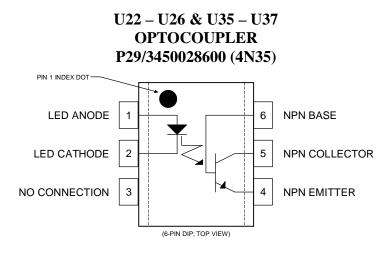

Scanned inputs include the six (6) PTT logic inputs from the mics, the three (3) mic sense (connected/not connected) logic lines, two (2) Call Director sense logic lines (jack sense and on-hook sense), and eight (8) digital input logic lines from on-board optocouplers. PTT and sense inputs originate from the buffer circuits described in the previous section. [Audio System Board schematic diagram sheets 5, 24, 25, 28 and 29.]

No debounce operations are performed by U72. This function is accomplished via the R-C and Schmitt trigger networks on the input lines as previously described.

U72 scans the inputs by sequentially reading threestate octal buffers U43, U70 and U54. This is accomplished using scan logic line outputs SL1 thru SL3 from U72 to sequentially strobe each octal buffer. The scan rate is 102.4 kHz or approximately 10 microseconds between scan logic line toggles. [Audio System Board schematic diagram sheet 5.]

For example, to read the eight digital input logic lines from the optocouplers, U72 pulls its SL1 output low and all other SL outputs high. This enables U43. When enabled, U43's eight output buffers drive U72's eight return logic line row inputs identified as RL0 thru RL7. Since the SL2 and SL3 outputs are high, all U70 and U54 buffer outputs remain in a high-impedance state. Next, U72 stores the logic state of each return logic line in an internal register so it can be read by microcontroller U56 if a change has occurred since the previous read. Approximately 10 microseconds later, scan logic line SL1 transitions high, disabling U43, and SL2 transitions low so U70's PTT and sense input logic lines can be read.

When a change occurs in one or more inputs, U72 pin

| FROM I/O<br>BACKPLANE<br>BOARD | J2<br>& J21<br>PIN | INPUT NAME - FROM<br>I/O BACKPLANE<br>BOARD (Active Low) | BUFFERED<br>NAME<br>(Active High) | USE                                     |

|--------------------------------|--------------------|----------------------------------------------------------|-----------------------------------|-----------------------------------------|

| J7 pin 6                       | 41                 | SUPR_PTT_IN                                              | SUPR_PTT                          | Supervisor Headset PTT Input            |

| J6 pin 6                       | 45                 | OPR_PTT_IN                                               | OPR_PTT                           | Operator Headset PTT Input              |

| J5 pin 6                       | 42                 | DESK_MIC_PTT_IN                                          | DESK_MIC_PTT                      | Desk Mic PTT Input                      |

| J4 pin 6                       | 43                 | B/G_PTT_IN                                               | B/G_PTT                           | Boom/Gooseneck Mic PTT Input            |

| J2 pin 3                       | 40                 | PAGER_PTT_IN                                             | PAGER_PTT                         | Pager PTT (Enable) Input                |

| J14 & J15 pins<br>4, J5 pin 3  | 44                 | MONITOR_PTT_IN                                           | MONITOR_PTT                       | Monitor Switch/Button                   |

| J7 pin 3                       | 74                 | SUPR_JACK_SENSE_IN                                       | SUPR_JACK_SENSE                   | Supervisor Headset Jack Box Sense Input |

| J6 pin 3                       | 76                 | OPR_JACK_SENSE_IN                                        | OPR_JACK_SENSE                    | Operator Headset Jack Box Sense Input   |

| J3 pin 3                       | 75                 | CD_JACK_SENSE_IN                                         | CD_JACK_SENSE                     | Call Director Handset Jack Sense Input  |

| J3 pin 2                       | 71                 | CD_HOOK_SENSE_IN                                         | CD_HOOK_SENSE                     | Call Director Off-Hook Sense Input      |

| J4 pin 3                       | 72                 | B/G_MIC_SENSE_IN                                         | B/G_MIC_SENSE                     | Boom/Gooseneck Mic Sense Input          |

Table 2 - PTT And Sense Inputs\*

$\ast~$  Refer to Audio System Board schematic diagram sheets 28 and 29.

4 transitions high. This pulls the interrupt logic line to microcontroller U56 identified as KEYINTR\* low via inverter U73 (pins 8 & 9). Upon being interrupted via the KEYINTR\* pulse, U56 reads U72 to determine which input(s) has changed.

Control inputs from U56 to U72 include the active-low read logic line (RD/), the active-low RAM or I/O write logic line (RAMIOWR\*) and a chip select logic line (8279CS\*). In addition, U72 is reset at power-up by RESET (high = reset) from microprocessor supervisory chip U55. [Audio System Board schematic diagram sheets 2 and 5.]

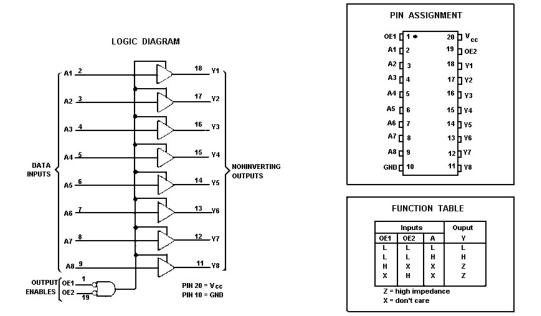

## **RS-232 Dispatch Keyboard Serial Port**

Integrated circuit U44 and the associated components perform TTL-to-RS-232 conversions between the microcontroller's TTL-level serial port and the Dispatch Keyboard's RS-232 serial port. This keyboard is sometimes referred to as the "Custom Keyboard". Connector J18, shown within dotted lines on the schematic, is the DB-9 connector located at the rear panel of the Enhanced Audio Enclosure. The keyboard plugs to this connector. J18 is a connector on the I/O Backplane Board. RS-232 serial keyboard data received from the keyboard is present on J18 pin 2. The transmit line to the Dispatch Keyboard (J18 pin 3) is not used with current keyboard hardware. [Audio System Board schematic diagram sheet 5.]

When a key on the keyboard is pressed, RS-232 serial data from the keyboard is applied J18 pin 2. This signal is routed through the I/O Backplane Board and applied to J2 pin 38 on the Audio System Board. Inductor L7 couples the signal, RX\_DATA\_KEYBOARD\_IN, to U44 pin 13 for RS-232-to-TTL conversion. A suppressor within transient voltage suppressor TVS9 provides surge suppression from induced charges such as static electricity. The levelconverted data (TTL-level) is sent to microcontroller U56's serial port input at U56 pin 11 via the RX\_DATA\_KEYBOARD line.

TX\_DATA\_KEYBOARD at U44 pin 11 is the TTLlevel keyboard transmit output serial data from the microcontroller's serial port (U56 pin 13). As previously stated, this output is not used with current keyboard hardware. However, if used in the future, data on this transmit logic line to the keyboard could include keyboard control codes such as keyboard buffer clear codes. U44 converts this TTL-level data to  $\pm 10$ -volt RS-232-level data. The RS-232 output is pin 14. Inductor L8 couples the identified signal to J2 pin 39. as TX\_KEYBOARD\_DATA\_OUT. As shown on the Audio System Board schematic diagram, J2 pin 39 is connected to J18 pin 3 on the I/O Backplane Board. A suppressor within

transient voltage suppressor TVS9 provides surge suppression.

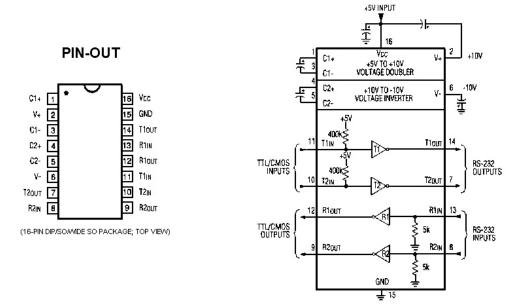

Integrated circuit U44 has a built-in +5-volt to  $\pm 10$ -volt charge pump converter; therefore, it only requires power from the +5VDIG supply to generate positive and negative RS-232 voltages. Capacitors C211 thru C213 are the chip's charge-pump capacitors. The  $\pm 10$ -volt supplies are used by the chip's RS-232 TX drivers, only one of which is wired for use.

Keyboard operating power is applied to J2 pin 34 and routed through the I/O Backplane Board to J18 pin 1 at the Enhanced Audio Enclosure's rear panel. Thermistor F1 provides an automatic resettable fuse function. In some cases, this component is not installed and as noted on the schematic, R12 is substituted.

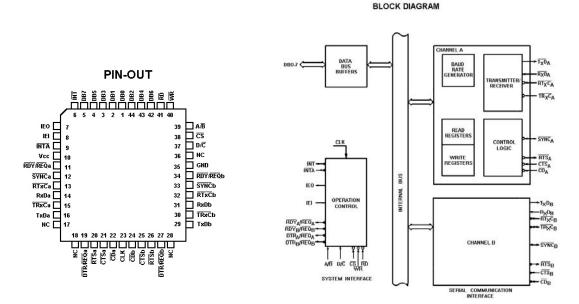

# Serial Communications Controller U71

Integrated circuit U71 is an Intel 82530 (or equivalent) Serial Communications Controller (SCC) chip. It provides two (2) additional serial ports for the Enhanced Audio Enclosure. One port – port A – is used for RS-232 serial interfacing to the PC (Personal Computer). The other – port B – provides an RS-422 serial port for expansion capability. U71 is addressed by microcontroller U56 as a part of U56's memory mapped I/O. [Audio System Board schematic diagram sheet 6.]

Drivers/receivers U68 for port A and U69 for port B convert U71's transmit and receive data TTL-level signals to RS-232 and RS422 level signals respectively. These drivers/receivers are described in greater detail in the following subsections.

On the microcontroller-side of U71, 8-bit parallel data is transferred to and from U71 via U56's multiplexed address/data bus, AD0 thru AD7. Transferred data includes the data to be converted and transmitted by U71, the data received and converted by U71, and SCC command data. U71 performs parallel-to-serial and serial-to-parallel conversions for the transmit and receive data respectively.

SERCS\* from I/O address decoder U76 is the activelow memory-mapped chip select line for SCC U71. It is applied to U71's chip select input at U71 pin 38. This chip select line is mapped to the microcontroller's external memory area between A000H and AFFFH. However, only the A000H thru A003H addresses are used as described in the following paragraph.

Address lines between microcontroller U56 and SCC U71 include only U56's lower two (2) address lines, A0 and A1. Thus, U56 reads from and writes to U71 via memory locations A000H thru A003H. A0 is applied to U71's data/command input at U71 pin 37. When high and the SCC is selected, data is transferred between U56 and U71.

When low and the SCC is selected, commands are transferred between the two chips. Address line A1 is applied to U71's A/B port select input at pin 39. When A1 is high and the SCC is selected, port A communications occur. When A1 is low and the SCC is selected, port B communications occur.

RAMIOWR\* from U56 and OR gate U75 (pins 11, 12 & 13) is applied to U71's active-low write enable input at U71 pin 40. This logic line pulses low when U56 writes a byte to a RAM location or to an memory-mapped I/O location such as address A000H. [Audio System Board schematic diagram sheet 2.]

#### **RS-232 Serial Port**

On the rear panel of the Enhanced Audio Enclosure, the DB-9 connector labeled "PC" provides RS-232 interconnections for the PC. Normally, serial port COM2 at the PC is used for PC-to-Enhanced Audio Enclosure control data interfacing. The data rate is 9600 baud.

Integrated circuit U68 is a Maxim MAX202 (or equivalent) dual transceiver device. As previously stated, U71's port A is utilized for communications with the PC and driver/receiver (transceiver) U68 performs TTL-to-RS-232 conversions between U71 port A and the PC's serial port. [Audio System Board schematic diagram sheet 6.]

Connector J17, shown within dotted lines on the schematic, is a female DB-9 connector at the Enhanced Audio Enclosure's rear panel (part of I/O Backplane Board). Transmit and receive RS-232 serial data to and from the PC is present on J17 pins 2 and 3 respectively. Interconnections are provided by 96-pin DIN connector J2 on the Audio System Board, mating connector J21 on the I/O Backplane Board, and the I/O Backplane Board's traces.

One driver within U68 is employed for RS-232 communications to the PC. TTL-level serial data signals from U71's port A transmit output at U71 pin 16 are applied to U68 pin 11, the input of the driver. The driver's output at U68 pin 14 is coupled to J2 pin 35 by inductor L12. This signal is identified TX\_PC\_DATA\_OUT and it is routed through the I/O Backplane Board to J17 pin 2 and from here, to the PC's serial COM port receive input.

The other driver within U68 is used as a power-up status line to the PC. POWER\_STATUS\_OUT from U68 pin 7 is applied to the COM port's clear-to-send pin. It is pulled to approximately -9 volts by the driver when the Enhanced Audio Enclosure is powered-up. This signal is routed through the I/O Backplane Board to J17 pin 8.

Only one receiver within U68 is used. Receive serial data from the PC's serial COM port is routed into the Enhanced Audio Enclosure via J17 pin 3 at the rear panel.

From this point the serial data is applied to J2 pin 13 on the Audio System Board. Inductor L11 couples this signal into the receiver at U68 pin 13. The receiver then converts the RS-232-level signals to TTL-level signals and applies them to U71's port A receive input at pin 14.

Three (3) suppressors within transient voltage suppressor TVS11 provide surge suppression on the serial and power-up status lines.

Integrated circuit U68 has a built-in +5-volt to  $\pm 10$ -volt charge pump converter; therefore, it only requires power from the +5VDIG supply to generate positive and negative RS-232 voltages. Capacitors C287 thru C290 are the chip's charge-pump capacitors. The  $\pm 10$ -volt supplies are used by the chip's two RS-232 TX drivers.

#### **RS-422 Serial Port**

Future serial I/O expansion capability is provided by the RS-422 full-duplex serial port at the back of the Enhanced Audio Enclosure. These connections are present at the female DB-9 connector labeled "I/O". This port meets EIA RS-422-A specifications up to a data rate of 19.2k baud. RS-422 serial links transfer data using balanced differential signals.

Integrated circuit U69 performs TTL-to-RS-422 conversions for SCC U71 port B. This chip is an Maxim MAX490 (or equivalent) device. Transmit and receive TTL-level serial data from U71 pins 29 and 31 is applied to the driver and receiver within U69 at pins 3 and 2 respectively. Differential lines on the external side of U69 are applied to the 96-pin connector J2 via inductors L13 thru L16. These differential lines are interconnected to J16 (part of I/O Backplane Board) at the Enhanced Audio Enclosure's rear panel.

Four (4) suppressors within transient voltage suppressor TVS12 provide surge suppression on the RS-422 differential serial data lines.

### AUDIO INPUT CIRCUITS

All audio signals applied to a C3 Maestro console system are routed into the console system by connectors and terminal blocks at the rear panel of the Enhanced Audio Enclosure. These connectors and terminal blocks are parts of the I/O Backplane Board. The I/O Backplane Board routes the signals to the input circuitry on the Audio System Board. Audio inputs include signals such as mic audio, line input audio from the CEC/IMC, and tones from a paging encoder.

After conditioning by the respective audio input circuits described in the following subsections, the audio signals are applied to the audio switching matrix formed by the cross-point switch chips. Before application to the audio matrix, each signal is adjusted for a nominal level of 436 millivolts rms (1.23 Vp-p) via one or more digital pots within the particular input audio circuit. Most audio input circuits on the Audio System Board have a dynamic range of approximately 12 dB.

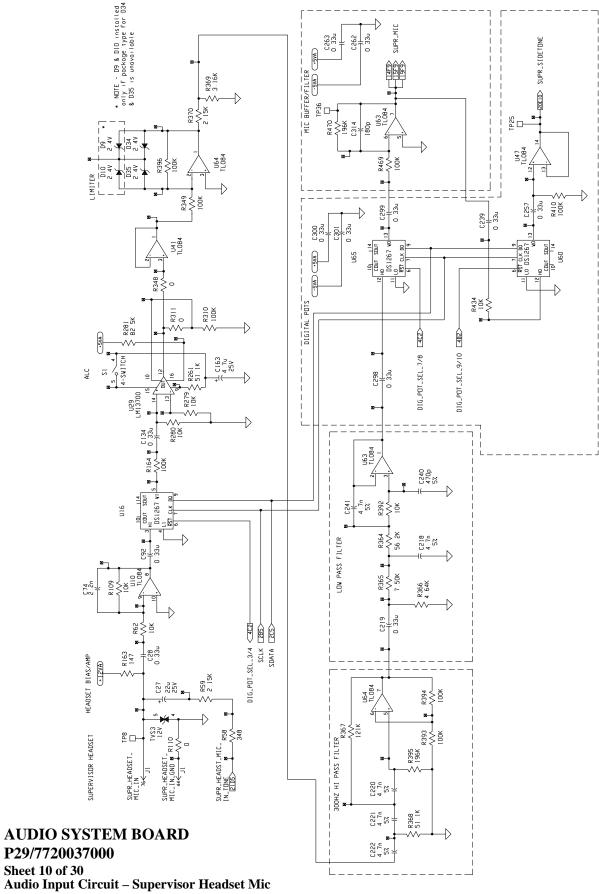

## Supervisor Headset Mic

Input At the rear panel of the Enhanced Audio Enclosure, the cable from the supervisor's headset jack box mates with the female DB-9 connector labeled "SUPER H/S". This is connector J7 on the I/O Backplane Board. Mic audio from the headset is applied to J7 pin 9 and the I/O Backplane Board routes this signal, SUPR\_HEADSET\_MIC\_IN, to the Audio System Board's supervisor mic input at connector J1 pin 76. On the Audio System Board, this line is also identified as SUPR\_HEADSET\_MIC\_IN. Connector J1 on the Audio System Board is a 96-pin DIN connector which mates with J22 on the I/O Backplane Board. [Audio System Board schematic diagram sheet 10. Also see I/O Backplane Board schematic diagram sheets 2 and 5 in LBI-39102.]

### Mic DC Bias & Surge Protection

SUPR\_HEADSET\_MIC\_IN is biased-up by the +12VA supply and resistor R163 on the Audio System Board. This relatively low-impedance dc bias is required for the mic and earphone amp circuits within the headset. When a headset is connected, the bias drops to approximately 3.0 Vdc. Static discharge surge protection is provided by one suppressor within transient voltage suppressor TVS3. As shown in the schematic, this suppressor is basically two 12-volt zener diodes connected back-to-back. [Audio System Board schematic diagram sheet 10.]

Ground reference for the supervisor's mic audio is provided by J1 pin 44. This connection is identified as SUPR\_HEADSET\_MIC\_IN\_GND on both the Audio System Board and the I/O Backplane Board schematic diagrams.

### **Input Buffer**

The moderate-level SUPER\_HEADSET\_MIC\_IN mic audio signal (approximately 200 mVp-p) is ac-coupled by C28 into an inverting buffer circuit formed by op-amp U10 (pins 8, 9 & 10) and associated components. This buffer stage does not provide any voltage gain for the mic audio signal but simply impedance buffering and high-frequency roll-off. C74 in the feedback loop sets the -3 dB roll-off point to approximately 7.2 kHz. U10's non-inverting input (+) is grounded and thus the output signal on pin 8 rides on a zero-volt dc potential in reference to analog ground. This is possible since all op-amps on the Audio System Board are powered by the bipolar (dual-polarity) power supply generated by the switching regulator circuits.

### **Input Level Control**

Buffered mic audio from U10 pin 8 is applied to the high-side (H1) of a digital pot within U16 (pins 3, 4 & 5). During alignment procedures performed at the Personal Computer (PC), this digital potentiometer (pot 4) provides input level-adjustment for the supervisor mic audio prior to application to the succeeding automatic level control (ALC) circuit. When commanded from the PC, microcontroller U56 loads wiper position data into U16. See the section entitled "**DIGITAL POT CIRCUITS**" for circuit analysis details describing how the digital pots are adjusted. The attenuated signal on U16's wiper at pin 5 is applied to the succeeding ALC circuit.

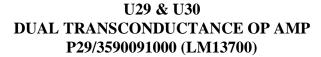

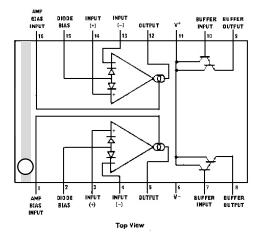

### Automatic Level Control (ALC)

One-half of U29 (pins 9 - 16), a dual transconductance op-amp, and the associated components form the supervisor headset mic ALC circuit. This high-performance ALC stage also provides pre-limiting functions for the supervisor mic audio. ALC can be enabled or disabled by changing the DIP switch at U29 pin 15 (S1 position 4). Normally, ALC is always enabled by selecting the "ON" or CLOSED" position. See LBI-39101 for additional information.

### **Buffer & Fast-Limiter**

The buffered, level-controlled and pre-limited output from U29 pin 12 is applied to op-amp voltage follower U41. The output of this stage at U41 pin 1 is applied to a fast-limiter stage.

Op-amp U64 (pins 1, 2 & 3) and associated components form a fast-limiter circuit for the supervisor headset mic audio signal. At the output, U64 pin 1, the maximum signal swing will not exceed approximately 5.9 Vp-p (2.1 Vrms). This signal is then scaled by divider network R369 and R370 and applied to high-pass and low-pass filter circuits which jointly, form a bandpass circuit for voice audio frequencies.

### High & Low-Pass Filters

The supervisor headset mic audio high-pass filter circuit is formed by U64 (pins 5, 6 & 7) and the associated components. This filter greatly attenuates any low-frequency signals such as 60 Hz hum which may exists in the mic audio signal.

The high-pass filter's output is fed to a low-pass filter formed by U63 (pins 1, 2 & 3) and the associated components. This filter greatly attenuates audio signals

above 3 kHz which may be present in the mic audio signal such as high-frequency hiss.

#### **Output Level Control**

The low-pass filter's output at U63 pin 1 is ac-coupled into the high-side of a digital pot within U65 (at U65 pin 12). This digitally-controlled potentiometer (pot 7) allows the supervisor's headset mic level to be set from the PC. This pot's setting should *not* be changed from the factory setting. See the section entitled **DIGITAL POT CIRCUITS**" for additional details.

#### **Output Buffer/Filter & Audio Matrix Inputs**

The signal on the wiper of the digital pot is ac-coupled into a buffer/filter circuit formed by U63 (pins 5, 6 & 7) and associated components. The output of this stage, identified as SUPR\_MIC (U63 pin 7), is applied to crosspoint switch chips U82, U81 and U80 for distribution (pins 23, 23 & 6 respectively). At nominal voice levels into the supervisor's headset mic, the signal on SUPR\_MIC is approximately 1.0 Vp-p. [Audio System Board schematic diagram sheets 10, 14, 15 and 19.]

In most instances, SUPR\_MIC is routed only to the Line 1 output via U82. (Supervisor mic audio is recorded by sending the Line 1 output audio to the recorder.) However, during local Call Director telephone operations (non-CD patch operations), SUPR\_MIC is routed via U80 to the Call Director output line so it can be applied to the phone line connected to the Call Director. See the section entitled "AUDIO OUTPUT CIRCUITS", subsection "Line Outputs", for details on the Line output circuits. [Audio System Board schematic diagram sheets 14 and 19.]

#### Sidetone

SUPR\_MIC audio is also applied to the supervisor sidetone level adjustment circuit consisting of one-half of digital potentiometer U60 and the associated components. This digital potentiometer (pot 9) provides adjustment for the supervisor's sidetone via PC control. The attenuated mic signal on the digital pot's wiper (U60 pin 13) is buffered by op-amp U47 (pins 12, 13 & 14) and applied to the audio matrix via the SUPR\_SIDETONE line from U47 pin 14.

Specifically, SUPR\_SIDETONE audio is applied to cross-point switch chip U40 at pin 22. The sidetone signal is switched to the supervisor's headset earphones by U40 under microcontroller U56 control. SUPR\_SIDETONE may also be switched to the operator's headset earphones. In both instances, other signals such as select audio (SELECT\_AUDIO) is summed with SUPR\_SIDETONE before application to a headset via U40 and the supervisor headset earphone output circuit. [Audio System Board schematic diagram sheets 10 and 20.]

See the section entitled **A'UDIO OUTPUT CIRCUITS**" for details on the supervisor and operator headset earphone output circuits.

### Keying

The supervisor's headset can be keyed from a footswitch via the "SUPR\_F/S" connector (I/O Backplane Board connector J15) at the rear panel, or the PTT input provided at the "SUPR H/S" connector (J7), also at the rear panel. It *cannot* be keyed from the Dispatch Keyboard. Footswitch and headset connectors on the rear panel have a common PTT line identified as SUPR\_PTT\_IN. SUPR\_PTT\_IN is applied to the Audio System Board at J2 pin 41. Microcontroller U56 reads SUPR\_PTT\_IN using the logic interface circuitry described in the sections entitled "**PTT And Sense Input**" and "**Input Scanning**". [Audio System Board schematic diagram sheets 5 and 28.]

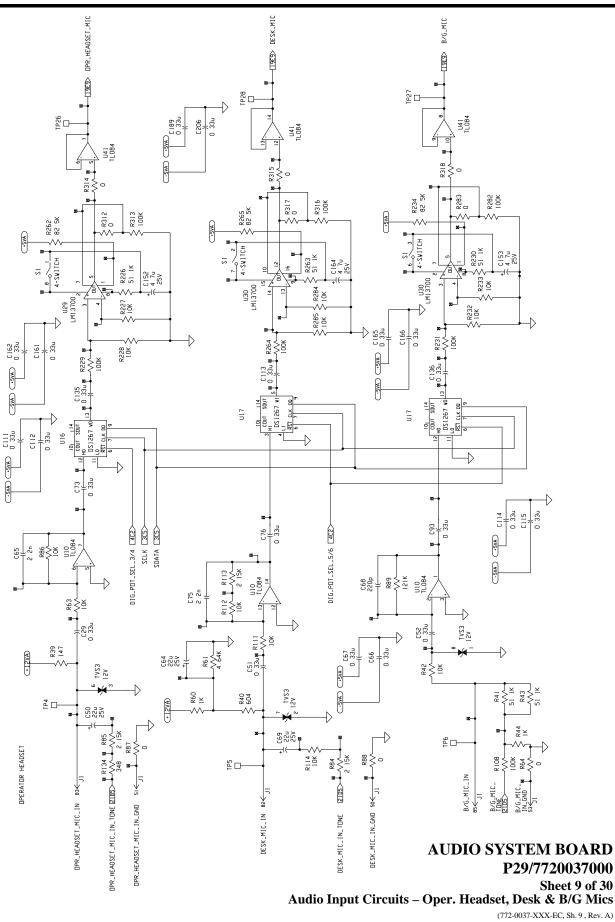

## **Operator Headset Mic**

Basically, the first four (4) stages of the operator's headset mic input circuit are identical to the first four stages of the supervisor's circuit. Therefore, these stages will not be discussed in full detail.

At the rear panel of the Enhanced Audio Enclosure, the cable from the operator's headset jack box mates with the female DB-9 connector labeled "OPER H/S". This is connector J6 on the I/O Backplane Board. Mic audio from the headset is applied to J6 pin 9 and the I/O Backplane Board routes this signal, OPR\_HEADSET\_MIC\_IN, to the Audio System Board's operator mic input at J1 pin 83. This input is also identified as OPR\_HEADSET\_MIC\_IN. J1 is a 96-pin DIN connector on the Audio System Board which mates with J22 on the I/O Backplane Board. [Audio System Board schematic diagram sheet 9. Also see I/O Backplane Board schematic diagram sheets 2 and 5 in LBI-39102.]

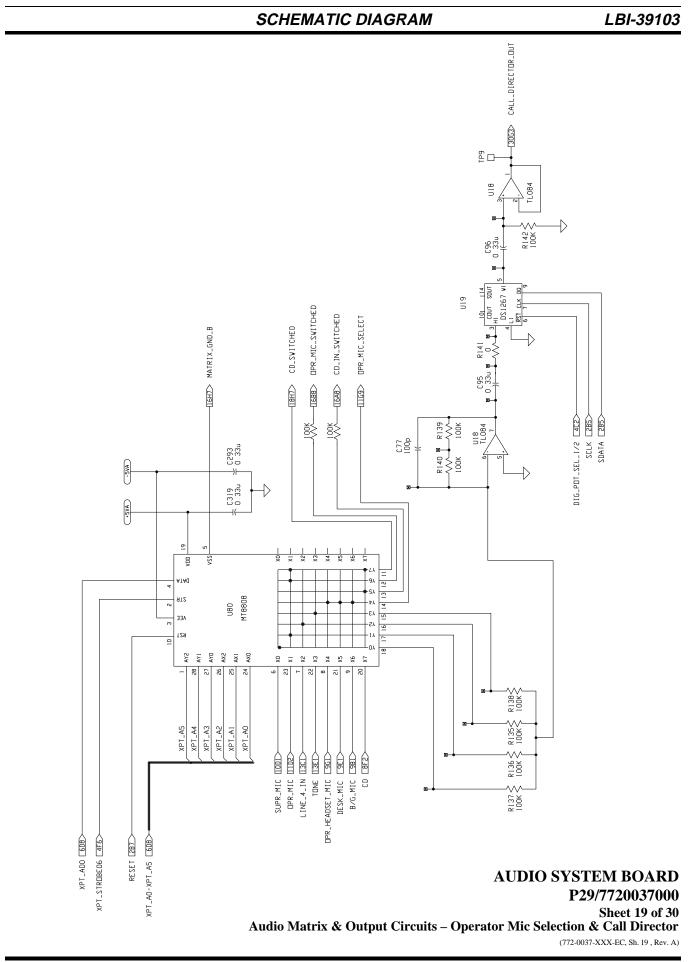

#### Selection

Buffered and level-controlled operator headset mic audio from the output of the first four stages at U41 pin 7 (OPR\_HEADSET\_MIC) is applied to the audio matrix at U80 pin 8. As shown in the schematic diagram, three (3) switches within U80 are used to select between the operator, desk or boom/gooseneck mic signals. The selected the output the signal at of matrix chip. OPR\_MIC\_SELECT (U80 pin 14), is routed to the input of non-supervisory mic audio post-conditioning circuit. [Audio System Board schematic diagram sheets 9, 11 and 19.]

See the following section entitled "<u>Non-Supervisory</u> <u>Mic Audio Selection And Post-Conditioning</u>" for circuit analysis details on the post-conditioning mic audio circuits.

#### Keying

The operator's headset can be keyed from any of several places including the Dispatch Keyboard, a footswitch, or the OPR\_PTT\_IN input. The OPR\_PTT\_IN input is located at "OPER H/S" connector J6 pin 6 on the Enhanced Audio Enclosure's rear panel. Microcontroller U56 reads OPR\_PTT\_IN (J2 pin 45 on the Audio System Board) via the associated I/O Backplane Board interconnections and theogic interface circuitry on the Audio System Board. Logic interface circuitry is described in detail in the sections entitled "**PTT And Sense Input**" and "**Input Scanning**". J2 is a 96-pin DIN connector on the Audio System Board which mates with J21 on the I/O Backplane Board. [Audio System Board schematic diagram sheets 5 and 28. Also see I/O Backplane Board schematic diagram sheets 3 and 5 in LBI-39102.]

#### **Desk Mic**

With the exception of the dc mic bias circuitry and slight input level differences, the first four stages of the desk mic input circuit is basically identical to the supervisor circuit previously described. Therefore, these stages will not be discussed in full detail.

At the rear panel of the Enhanced Audio Enclosure, the desk mic connects to the female DB-9 connector labeled "DESK MIC", connector J5 on the I/O Backplane Board. Audio from the mic is applied to J5 pin 9 and the I/O Backplane Board routes this signal, DESK\_MIC\_IN, to the Audio System Board's desk mic input at J1 pin 82. The Audio System Board desk mic input is also identified as DESK\_MIC\_IN. J1 is a 96-pin DIN connector on the Audio System Board which mates with J22 on the I/O Backplane Board. [Audio System Board schematic diagram sheet 9.]

#### **Mic DC Bias & Surge Protection**

A well-filtered dc bias for the desk microphone is provided by the network formed by R40, R60, R61 and C64. With a microphone connected (1000-ohm load), dc bias on DESK\_MIC\_IN is approximately 4 Vdc.

#### Selection

Buffered and level-controlled desk mic audio from the output of the first four (4) stages at U41 pin 14 (DESK\_MIC) is applied to the audio matrix at U80 pin 21. As shown in the schematic diagram, three (3) switches within U80 are used to select between the operator, desk, or boom/gooseneck mic signals. The selected signal at the output of the matrix chip (U80 pin 14) is routed to the non-supervisory mic audio post conditioning circuit. Desk mic audio is only selected if no headset and/or no boom/gooseneck mic is connected; it has the lowest

priority. [Audio System Board schematic diagram sheets 9, 11 and 19.]

### Keying

The desk mic can be keyed from the Dispatch Keyboard, footswitch, or the DESK\_PTT\_IN input at "DESK MIC" connector J5 pin 6. Microcontroller U56 reads DESK\_MIC\_PTT\_IN at J2 pin 42 via the associated I/O Backplane Board interconnections and the logic interface circuitry. This logic interface circuitry is described in detail in the sections entitled "PTT And Sense Input" and "Input Scanning". J2 is a 96-pin DIN connector on the Audio System Board which mates with J21 on the I/O Backplane Board. [Audio System Board schematic diagram sheets 5 and 28.]

### **Boom/Gooseneck Mic**

With the exception of the lack of any mic dc bias circuitry and increased signal gain in the first amplifier stage, the first four (4) stages of the boom/gooseneck mic input circuit is nearly identical to the supervisor circuit previously described. Therefore, these stages will not be discussed in full detail.

At the rear panel of the Enhanced Audio Enclosure, a boom or gooseneck microphone connects to the female DB-9 connector labeled "B/G MIC", connector J4 on the I/O Backplane Board. Audio from the mic is applied to J4 pin 9 and the I/O Backplane Board routes this signal, B/G\_MIC\_IN, to the Audio System Board's boom/gooseneck mic input at J1 pin 85. On the Audio System Board, this input is also identified as B/G\_MIC\_IN. [Audio System Board schematic diagram sheet 9.]

All boom or gooseneck microphones used with the C3 Maestro console employ dynamic magnetic cartridge-type voice coils and no internal amplifiers; therefore, no dc bias is required on the mic audio input line. Typically, these mics have output levels less than 10 millivolts peak-to-peak at average voice sound levels.

#### **Input Buffer/Amp**

Since audio from the boom/gooseneck mic is much lower than the headset and desk mics, the gain of the first amplifier on the Audio System Board stage is much larger. Op-amp U10 (pins 1, 2 & 3) and the associated components provide approximately 22 dB of gain. Capacitor C50 sets the -3 dB high-frequency roll-off point to approximately 7.2 kHz. This stabilizes the circuit by preventing oscillations.

#### Selection

Buffered and level-controlled boom/gooseneck mic audio (B/G\_MIC) from U41 pin 8 is applied to the audio matrix at U80 pin 9. As shown in the schematic diagram, three (3) switches within U80 are used to select between the operator, desk or boom/gooseneck mic signals. The selected signal at the output of the matrix chip (U80 pin 14) is routed to the non-supervisory mic audio post conditioning circuit. Boom/gooseneck mic audio is only selected if no headset (supervisor or operator) is connected to the Enhanced Audio Enclosure. [Audio System Board schematic diagram sheets 9, 11 and 19.]

### Keying

The boom/gooseneck mic can be keyed from the Dispatch Keyboard, footswitch, or the B/G\_PTT\_IN input at "B/G MIC" connector J4 pin 6 on the I/O Backplane Board. Microcontroller U56 reads B/G\_PTT\_IN at J2 pin 43 via the associated I/O Backplane Board interconnections and its logic interface circuitry. This logic interface circuitry is described in detail in the sections entitled "<u>PTT</u> <u>And Sense Input</u>" and "Input Scanning". J2 on the Audio System Board mates with J21 on the I/O Backplane Board. [Audio System Board schematic diagram sheets 5 and 28. Also see I/O Backplane Board schematic diagram sheets 2 and 4.]

#### - NOTE

All boom/gooseneck mic connectors (male DB-9) must have pins 2 and 3 jumpered together so B/G\_MIC\_SENSE\_IN will be activated (grounded) when the mic is connected to J4 (female DB-9).

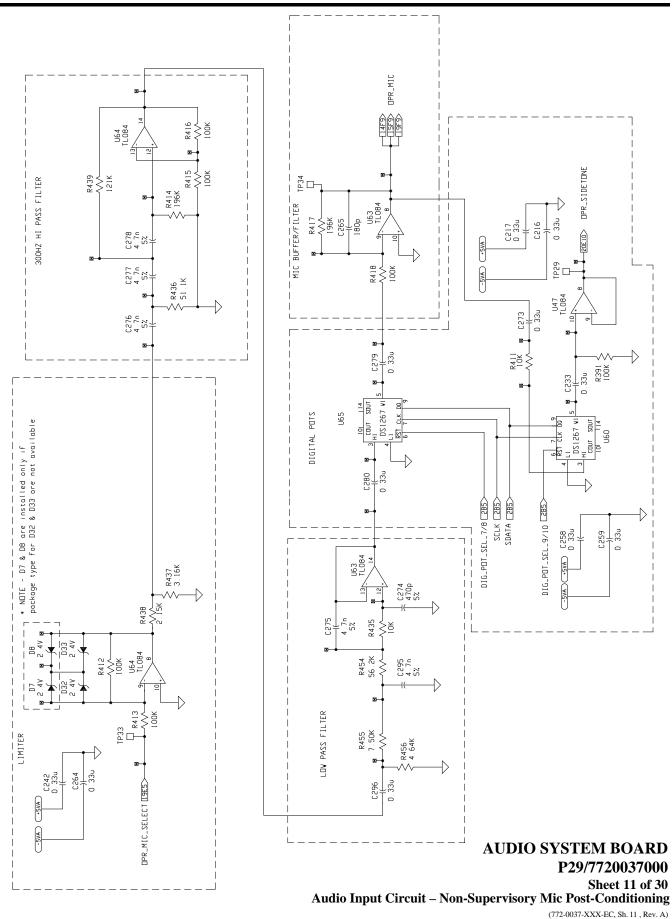

# **Non-Supervisory Mic Audio Selection And Post-Conditioning**

#### Selection

If no headset is connected to the Enhanced Audio Enclosure's supervisor headset connector, I/O Backplane Board J7 pin 3 and Audio System Board J2 pin 74 (SUPR\_JACK\_SENSE\_IN) are inactive or high. In this case, the Audio System Board selects a non-supervisory mic audio signal (OPR\_HEADSET\_MIC, DESK\_MIC or B/G\_MIC). This selection is based upon the boom/gooseneck mic senseput at Audio System Board J2 pin 72 (I/O Backplane Board J4 pin 3) and the operator headset sense input at J2 pin 76 (I/O Backplane Board J6 pin 3).

As previously described, the selected mic audio is connected to OPR\_MIC\_SELECT using switches within cross-point switch U80. Of these three non-supervisory mic inputs, the operator headset audio has the highest priority and the desk mic audio has the lowest. In other words, mic audio from the desk mic is never selected if a headset or a boom/gooseneck mic is connected. In addition, mic audio from the desk and boom/gooseneck mics are never used if a headset is connected. The microcontroller's operating firmware sets this mic priority. [Audio System Board schematic diagram sheets 9, 11, 19 and 29. Also see I/O Backplane Board schematic diagram sheets 3 and 5.]

### **Post-Conditioning**

The selected (switched-in) non-supervisory OPR\_MIC\_SELECT signal from U80 pin 14 is applied to post-conditioning circuits which are nearly identical to the supervisor post-conditioning mic audio circuits previously described. Therefore, these circuits will not be discussed in full detail. The circuitry includes a fast-limiter, high and low-pass filters which together provide voice-audio bandpass filtering, a digital pot level adjustment circuit, a mic buffer/filter, a sidetone digital pot level adjustment circuit, and a sidetone buffer/amp circuit. [Audio System Board schematic diagram sheets 11 and 19.]

The circuit's output, OPR\_MIC at U63 pin 8, is applied to cross-point switch chips U82, U81 and U80 for distribution as needed. In most instances, the selected nonsupervisory mic audio signal is routed only to the Line 1 output via U82. However, during local Call Director telephone operations (non-CD patch operations), OPR\_MIC is routed via U80 to the Call Director output line so it can be applied to the phone line connected to the Call Director. [Audio System Board schematic diagram sheets 11, 14, 15 and 19.]

OPR\_MIC is also applied to the non-supervisory sidetone level adjustment circuit consisting of digital potentiometer U60 (wiper = pin 5) and an op-amp buffer stage. This digital pot can be set via  $\langle Alt \rangle \langle Vol \uparrow \rangle$  (increase sidetone) and  $\langle Alt \rangle \langle Vol \downarrow \rangle$  (decrease sidetone) keystrokes at the Dispatch Keyboard program. The C3 Maestro's application program also allows digital pot adjustment via a note card. See the section entitled "**DIGITAL POT CIRCUITS**" in this manual for additional circuit analysis details. See LBI-39101 for specific details on adjusting a digital pot via a note card. [Audio System Board schematic diagram sheet 11.]

The attenuated and buffered sidetone signal, OPR\_SIDETONE, is applied to the cross-point switch chip U40 at pin 7. This sidetone signal is switched into a summing network and applied to the operator's headset earphones. It may also be summed with other signals and applied to the supervisor's headset earphones. [Audio System Board schematic diagram sheet 20.]

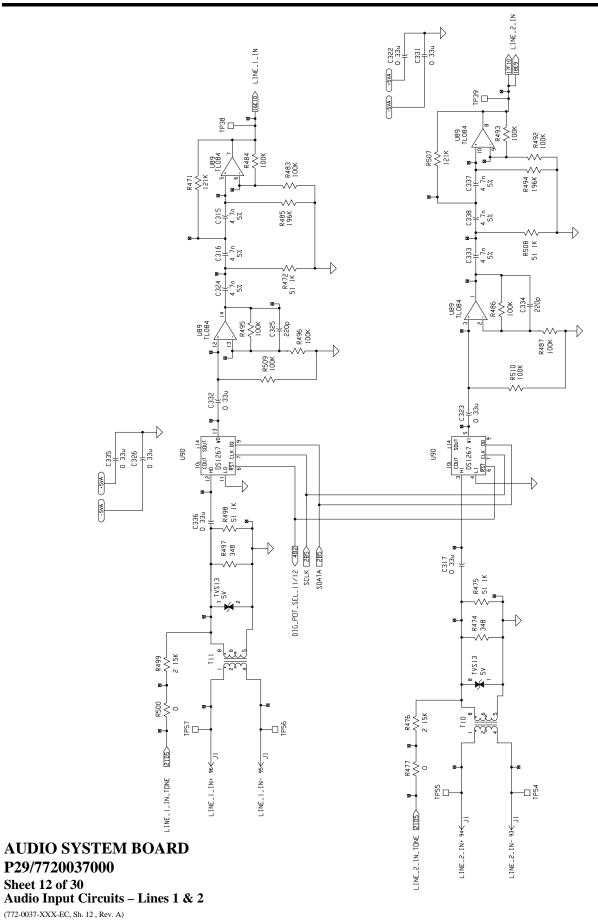

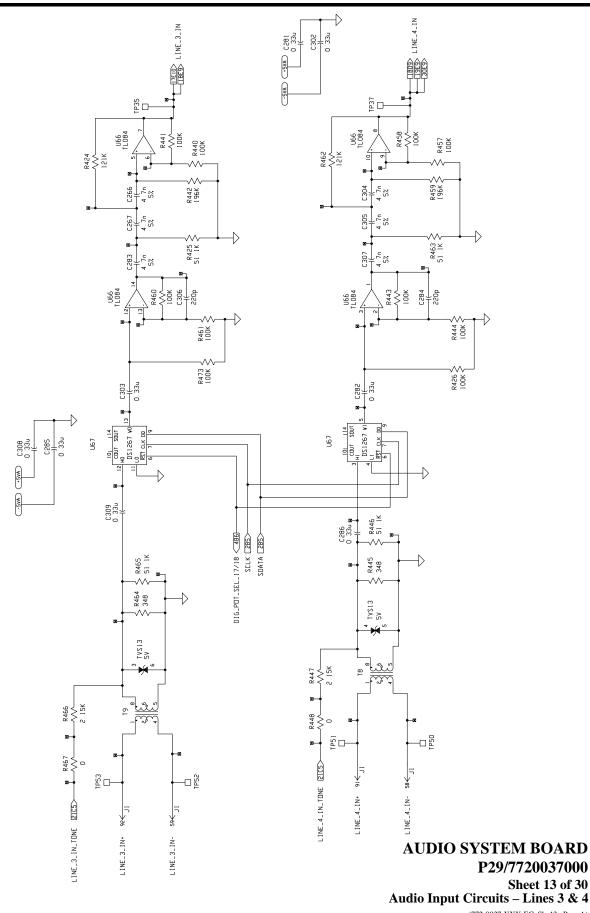

# **Line Inputs**

Four 600-ohm 4-wire balanced line interfaces are provided at the Enhanced Audio Enclosure's rear panel for interfacing to the CEC/IMC Digital Audio Switch. All four inputs are basically identical; therefore, only the Line 1 input circuit will be discussed in detail. [Audio System Board schematic diagram sheets 12 and 13.]

At the Enhanced Audio Enclosure, all 4-wire balanced line audio connections to and from the CEC/IMC are made at I/O Backplane Board connector J1. This female DB-25 connector is labeled "LINES 1-4" on the rear panel. All balanced line audio signals on J1 are routed to 96-pin DIN connector J22. J22 mates with Audio System Board connector J1.

### Line Coupling & Surge Protection

Audio on the Line 1 input pair is coupled into the Audio System Board via 600-ohm coupling transformer T11. The balanced inputs are identified LINE\_1\_IN+ and LINE\_1\_IN- at 96-pin DIN connector J1 pins 96 and 95 respectively. The I/O Backplane Board's DB-25 connector at the rear panel of the Enhanced Audio Enclosure also uses this same labeling (J1 pin 1 = LINE\_1\_IN+ and J1 pin  $2 = \text{LINE}_1_IN$ -). [Audio System Board schematic diagram sheet 12. Also see I/O Backplane Board schematic diagram sheets 1 and 5.]

On the Audio System Board, resistor R497 loads T11's secondary for an approximate line input impedance of 600 ohms. Surge protection on the transformer's secondary or non-line side is provided by one suppressor within transient voltage suppressor TVS13.

#### Level Control & Buffer/Amp

C336 ac-couples the signal on the secondary of T11 to one of the digital pots within U90. This digital pot provides computer-controlled level adjustment for the Line 1 audio input via the PC during alignment procedures. See the section entitled "**DIGITAL POT CIRCUITS**" for circuit analysis details describing how the digital pots are adjusted.

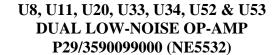

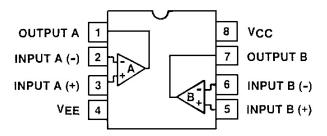

Op-amp U89 (pins 12, 13 & 14) and associated components form a non-inverting buffer/amplifier stage that provides a voltage gain of two (2). Capacitor C325 sets the -3 dB roll-off point at 7.2 kHz. This stage amplifies the signal from the wiper of the digital pot (U90 pin 13). The amplified signal is applied to the succeeding high-pass filter stage via capacitor C324.

#### High-Pass Filter/Buffer & Audio Matrix Input

Capacitor C324 ac-couples Line 1 audio from U89 pin 14 to the input of a high-pass filter circuit formed by U89 (pins 5, 6 & 7) and associated components. This active filter circuit passes all voice audio frequencies and greatly attenuates any frequency below 300 Hz which may be present on the Line 1 input (60 Hz hum, for example). The output of this filter, LINE\_1\_IN at TP38, is applied to matrix chip U49 at pin 6. Using a cross-point switch within U49, microcontroller U56 can switch Line 1 input audio to the SELECT\_AUDIO line as required. With a -5 dBm signal (436 mV rms into 600 ohms) on the Line 1 balanced input, the LINE\_1\_IN signal at TP38 is set via the digital pot to 436 millivolts rms (1.23 Vp-p).

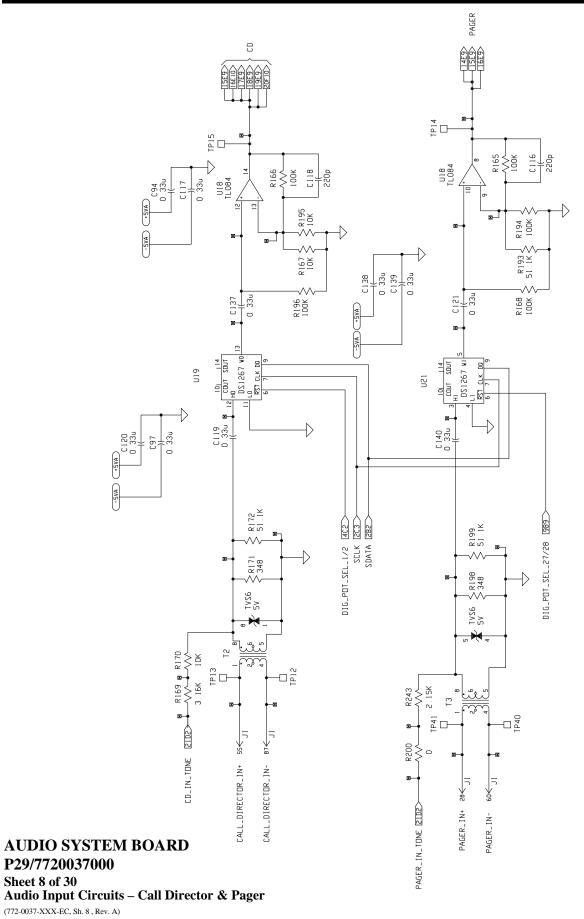

# **Call Director**

The C3 Maestro console system can be connected to Call Director (CD) for CD patch telephone operations. This feature allows the dispatcher to "patch" a telephone line to a specific unit, talk group, conventional channel or radio patch in the CEC/IMC network. When not being used for CD patch telephone communications, the dispatcher may also use the Call Director for local telephone operations.

A *Call Director patch* should not be confused with a *radio patch* in which a collection of radio talk groups are interconnected for common communications as one group.

Audio interfacing to a CD is performed by a 4-wire 600-ohm balanced line interface. On the Audio System Board, the input pair interface is very similar to the Line 1 input circuitry described in the previous section. Audio on this pair is from the CD (originating from the telephone's "mic") and it is heard by a radio in a patch operation or by the dispatcher in a local CD telephone operation.

### Line Coupling & Surge Protection

Audio from the Call Director is applied to connector J3 on the I/O Backplane Board. This female DB-9 connector at the Enhanced Audio Enclosure's rear panel is labeled "CALL DIR". I/O Backplane Board interconnections route the balanced line input signal from J3 to 600-ohm coupling transformer T2 on the Audio System Board. On the Audio System Board, these balanced line audio inputs are identified as CALL\_DIRECTOR\_IN+ and CALL\_DIRECTOR\_IN- at Audio System Board connector J1 pins 55 and 87 respectively. J1 is the 96-pin DIN connector on the Audio System Board that mates with J22 on the I/O Backplane Board. A typical CD balanced line

audio input signal is -20 dBm. [Audio System Board schematic diagram sheet 8.]

Resistor R171 loads T2's secondary for a 600-ohm line input impedance. Surge protection is provided by one suppressor within transient voltage suppressor TVS6.

#### Level Control & Output Buffer/Amp

Capacitor C119 ac-couples the signal on the secondary side of T2 to one of the digital pots within U19. This digital pot provides computer-controlled level adjustment for the CD input audio. See the section entitled "**DIGITAL POT CIRCUITS**" for circuit analysis details describing how the digital pots are adjusted.

Op-amp U18 (pins 12, 13 & 14) and associated components form a non-inverting buffer/amplifier stage with an approximate voltage gain of twenty-one (21) or 26 dB. C118 in the op-amp's feedback loop sets high-frequency roll-off to -3 dB at 7.2 kHz. With a -20 dBm CALL\_DIRECTOR\_IN+/- line input signal, the CD signal at TP15 (U18 pin 14) is set via the digital pot to 436 millivolts rms (1.23 Vp-p) into the matrix.

#### **Audio Matrix Inputs**

Buffered and level-adjusted CD input audio from U18 pin 14, identified as CD, is applied to cross-point switch chips U81, U49, U39, U48, U80 and U40 for distribution as required. For example, during a CD radio patch, a switch within U81 turns on to route the CD input audio (originating from telephone's "mic") to the CEC/IMC via CIM Line 4. [Audio System Board schematic diagram sheets 15 thru 20.]

If the unselect/telephone recorder output is used for sending *Call Director audio to a recorder*, CD input audio applied to U80 pin 20 is switched on and off via the switch within U80. Switched CD audio on the output side of the audio matrix, CD\_SWITCHED, is applied to the unselect/telephone recorder output circuit (output is USEL/TELE\_RECORDER\_OUT at J2 pin 86). However, if this output circuit is used for sending *unselect audio* to a recorder, CD\_SWITCHED is not used and line 2, 3 and 4 input audio is switched in via U48 pins 21, 9 and 20 respectively. [Audio System Board schematic diagram sheets 18 and 19.]

#### Pager Pager

Audio from a paging encoder (or similar device) is applied to terminal block J2 at the rear panel of Enhanced Audio Enclosure. This terminal block is labeled "PAGING". It provides connections for both pager audio (usually tones) and a pager PTT (enable) input. Pager audio is applied to J2 terminals 1 and 2. On both the Audio System Board and the I/O Backplane Board, the balanced line audio input is identified PAGER\_IN+ and PAGER\_IN-.

The pager PTT input is routed to the Audio System Board via the I/O Backplane Board and then interfaced to microcontroller U56. See the section entitled <u>PTT And</u> <u>Sense Input</u>" for specific details. Pager audio is only switched in when the paging encoder activates the pager PTT input.

#### Line Coupling & Surge Protection

Balanced audio from J2 terminals 1 and 2 is routed through the I/O Backplane Board and applied to 600-ohm coupling transformer T3 on the Audio System Board. PAGER\_IN+ is located at J1 pin 28 and PAGER\_IN- is located at J1 pin 60. Typical pager audio input level is -5 dBm. [Audio System Board schematic diagram sheet 8.]

Resistor R198 loads T3's secondary for a line input impedance of 600 ohms. Surge protection is provided by a suppressor within transient voltage suppressor TVS6.

#### Level Control & Output Buffer/Amp

Capacitor C140 ac-couples the signal on the secondary or non-line side of T3 to one of the digital pots within U21 (pot 28). See the section entitled **DIGITAL POT CIRCUITS**" for circuit analysis details describing how the digital pots are adjusted. The attenuated pager signal on the wiper of the pot (U21 pin 5) is applied to the buffer/amp stage formed by op-amp U18 (pins 8, 9 & 10) and associated components. This stage has an approximate voltage gain of four (4) or 12 dB. C116 in the feedback loop sets the high-frequency roll-off to approximately -3 dB at 7.2 kHz. The output at U18 pin 8 or TP14 is identified PAGER.

#### **Audio Matrix Inputs**

PAGER audio signals are applied to cross-point switch chips U82, U81 and U49 pins 7, 7 and 23 respectively. U82 and U81 switch the pager's signals to the line outputs. U49 switches the signals to the SELECT\_AUDIO line so it can be routed to the select audio output devices. These devices include the select speaker, headsets and the select recorder output. [Audio System Board schematic diagram sheets 14, 15, 16 & 20.]

### **DIGITAL POT CIRCUITS**

To provide computer-controlled level settings from the Personal Computer (PC), the audio input and output circuits incorporate 256-position digitally-controlled potentiometers. These digital pots allow all audio levels associated with the Enhanced Audio Enclosure to be adjusted via the PC. Adjustments include dispatch operatoradjustable audio levels such as headset sidetone volumes and system-level adjustments such as line input and output levels to and from the CEC/IMC Digital Audio Switch.

With the exception of the headsets' sidetone volume adjustments, none of the digital pots provide volume adjustments for the speaker or headset earphone audio signals. Speaker and headset volume adjustments are accomplished at the respective speaker or headset by mechanical potentiometers or as described in the following note.

#### – NOTE —

Communication module volume changes at the C3 Maestro effect CEC/IMC CIM line output levels, not the digital pots within the Enhanced Audio Enclosure.

Fifteen (15) dual potentiometer chips are located on the Audio System Board for a total of thirty (30) individual pots; there are *no* mechanical potentiometers – *all* audio level adjustments are made via software control. Basically, commands from the PC instruct microcontroller U56 to load new settings into a digital pot. See Table 3.

As shown in Table 3, for example, both pots within U16 are in separate circuits. One is located in the operator headset mic input preamp/pre-adjustment circuit (wiper is pin 13; pot 3) and the other is in the supervisor headset mic input preamp/pre-adjustment circuit (wiper is pin 5; pot 4). [Audio System Board schematic diagram sheets 9 and 10.]

All of the digital pots initially power-up with the wiper in a 50% or centered position. Microcontroller 56 then immediately loads each pot in accordance with its respective setting stored in a "working" area of serial EEPROM chip U57. This EEPROM also contains an unchangeable "default" digital pot storage area. When shipped from the factory, the working area matches the default area.

The operator sidetone digital pot (U60 pins 3, 4 & 5) can be set via  $\langle Alt \rangle \langle Vol \uparrow \rangle$  and  $\langle Alt \rangle Vol \downarrow \rangle$  key

stokes from the console's Dispatch Keyboard. [Audio System Board schematic diagram sheets 10 and 11.]

In addition, this pot and all other digital pots on the Audio System Board may be set using the console's application program via a note card. Refer to LBI-39101 for details.

DO NOT ADJUST any digital pot from the factory setting unless a full understanding of the consequences is known.

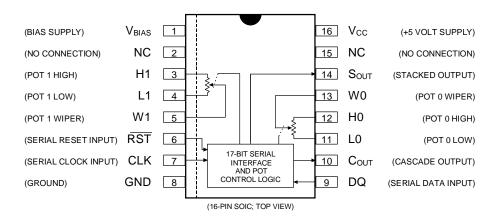

When a digital pot adjustment occurs, commands are sent from the PC to microcontroller U56 via the RS-232 serial communication link between the PC and the Enhanced Audio Enclosure. Next, U56 processes these commands and serially loads the new setting into the appropriate digital pot using the serial data (SDATA) line, the serial clock (SCLK) line, and a chip select logic line. As shown in Table 3, the fifteen (15) chip select logic lines, one for each dual pot chip, are identified as DIG\_POT\_SEL\_1/2 thru DIG\_POT\_SEL\_29/30. The serial data stream length sent out from U56 via SDATA during a digital pot adjustment is 17 bits long.

For example, to load both pots within U16 with new settings, DIG\_POT\_SEL\_3/4 transitions high to enable the chip. Next, seventeen bits which represent the two pots' new settings are clocked into U16 using SDATA and SCLK. Finally, DIG\_POT\_SEL\_3/4 returns low which latches the new pots settings and disables U16 from subsequent SDATA and SCLK activity. [Audio System Board schematic diagram sheets 9 and 10.]

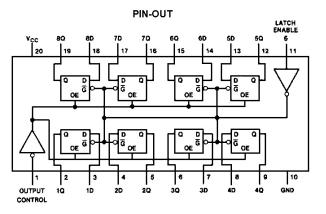

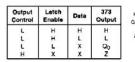

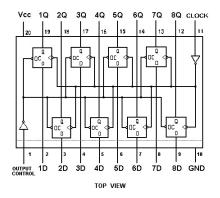

The DIG\_POT\_SEL\_xx logic lines are generated by microcontroller U56 by latching data bytes into octal data flip-flops U87 and U88. DIG\_POT\_SEL\_1/2 thru DIG\_POT\_SEL 15/16 are latched outputs from U88 and DIG\_POT\_SEL\_17/18 thru DIG\_POT\_SEL 29/30 are latched outputs from U87. [Audio System Board schematic diagram sheet 4.]

| SCH.<br>DGRM.<br>SHEET | IC  | WIPER<br>PIN | DIGITAL POT<br>SELECT LOGIC LINE<br>NAME | DIGITAL<br>POT<br>NUMBER * | CIRCUIT LOCATED IN / ADJUSTS                    |

|------------------------|-----|--------------|------------------------------------------|----------------------------|-------------------------------------------------|

| 1                      | U21 | 13           | DIG_POT_SEL_27/28                        | 27                         | N/A (pot not used)                              |

| 8                      | U19 | 13           | DIG_POT_SEL_1/2                          | 1                          | Call Director Input                             |

| 8                      | U21 | 5            | DIG_POT_SEL_27/28                        | 28                         | Pager Input                                     |

| 9                      | U16 | 13           | DIG_POT_SEL_3/4                          | 3                          | Operator Headset Mic Input (pre-adjustment)     |

| 9                      | U17 | 5            | DIG_POT_SEL_5/6                          | 6                          | Desk Mic Input (pre-adjustment)                 |

| 9                      | U17 | 13           | DIG_POT_SEL_5/6                          | 5                          | Boom/Gooseneck Mic Input (pre-adjustment)       |