# GETC<sup>™</sup> Shelf Assembly 19D901868G5 and G6

## **Includes:**

LOGIC BOARD 188D6500G1 and G4 REGULATOR ASSEMBLY 19C336816G2

## TABLE OF CONTENTS

| GETC FILTER BOARDS    | LBI-39204 |

|-----------------------|-----------|

| TURBO BOARD 19D903536 | LBI-38822 |

#### MANUAL REVISION HISTORY

| REV | DATE      | REASON FOR CHANGE                                |  |

|-----|-----------|--------------------------------------------------|--|

| Е   | Jan. 2005 | Updated drawing 188D6822 and Production Changes. |  |

M/A-COM Technical Publications would particularly appreciate feedback on any errors found in this document and suggestions on how the document could be improved. Submit your comments and suggestions to:

Wireless Systems Business Unit M/A-COM, Inc. Technical Publications 221 Jefferson Ridge Parkway Lynchburg, VA 24501 or fax your comments to: (434) 455-6851

or e-mail us at: techpubs@tycoelectronics.com

#### **CREDITS**

EDACS and MASTR are registered trademarks, and GETC, FailSoft, Aegis, and Guardog are trademarks of M/A-COM, Inc.

All other brand and product names are trademarks, registered trademarks, or service marks of their respective holders.

## **NOTICE!**

This manual covers M/A-COM products manufactured and sold by M/A-COM, Inc.

Repairs to this equipment should be made only by an authorized service technician or facility designated by the supplier. Any repairs, alterations or substitution of recommended parts made by the user to this equipment not approved by the manufacturer could void the user's authority to operate the equipment in addition to the manufacturer's warranty.

The software contained in this device is copyrighted by M/A-COM, Inc.

Unpublished rights are reserved under the copyright laws of the United States.

This manual is published by **M/A-COM, Inc.,** without any warranty. Improvements and changes to this manual necessitated by typographical errors, inaccuracies of current information, or improvements to programs and/or equipment, may be made by **M/A-COM, Inc.,** at any time and without notice. Such changes will be incorporated into new editions of this manual. No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of **M/A-COM, Inc.**

Copyright© 1996 - 2005, M/A-COM, Inc. All rights reserved.

#### SAFETY INFORMATION

## RADIO FREQUENCY INTERFERENCE

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna (i.e., the antenna for radio or television that is "receiving" the interference).

- Increase the separation between the equipment and receiver experiencing the interference.

- Connect the equipment into an outlet on a circuit different from the equipment receiving the interference.

#### WARNING

No one should be permitted to handle any portion of the equipment that is supplied with high voltage; or to connect any external apparatus to the units while the units are supplied with power. KEEP AWAY FROM LIVE CIRCUITS.

High-level RF energy in the transmitter Power Amplifier assembly can cause RF burns. KEEP AWAY FROM THESE CIRCUITS WHEN THE TRANSMITTER IS ENERGIZED!

#### NOTES

- The means of disconnecting power from a station cabinet is the cabinet power supply plug.

- When conducting repair/maintenance, disconnect the cabinet power supply plug from the AC source.

- In European applications, equipment must be installed in a closed cabinet.

- Only replace components with components specified by M/A-COM Private Radio Systems.

| TABLE OF CONTENTS                                               |             |

|-----------------------------------------------------------------|-------------|

| <u>Section/Paragraph</u>                                        | <u>Page</u> |

| SPECIFICATIONS*                                                 | 7           |

| RELATED PUBLICATIONS                                            | 8           |

| INTRODUCTION                                                    | 9           |

| IDENTIFICATION                                                  |             |

| DESCRIPTION                                                     | 10          |

| CONTROLS AND INDICATORS                                         |             |

| Front Panel Indicators                                          | 10          |

| Controls                                                        | 10          |

| OPTIONS                                                         | 10          |

| Turbo Board                                                     |             |

| ROCKWELL MODEM BOARD                                            | 11          |

| INTERFACE POINTS                                                |             |

| GETC COMMUNICATION LINKS                                        | 12          |

| CIRCUIT ANALYSIS                                                | 13          |

| GETC LOGIC BOARD                                                | 13          |

| Reset Circuitry                                                 |             |

| Clock Circuitry                                                 |             |

| Jumper Configuration                                            |             |

| Switch Settings                                                 |             |

| Power Supplies And Regulators                                   |             |

| Logic                                                           |             |

| Low-Speed Data Encode Filter                                    |             |

| Low-Speed Data Decode Filter                                    |             |

| High-Speed-Data Transmit Filter                                 |             |

| High-Speed Data Detector.                                       |             |

| 9600 Baud Modem Board And Telephone Line Interface              |             |

| INTERFACE                                                       |             |

| STATION CONTROL INTERFACE                                       |             |

| Synthesizer-Exciter Board Interface.                            |             |

| Data Load To Synthesizer-Exciter                                |             |

| SITE CONTROLLER INTERFACE                                       |             |

| Transmit Data                                                   |             |

| Receive Data                                                    |             |

| FAILSOFT INTERFACE                                              |             |

| BSL Receive Link                                                |             |

| BSL Transmit Link.                                              |             |

| Frame Sync Line                                                 |             |

| PERSONALITY PROGRAMMING                                         |             |

| Programming a Personality Using TQ-3357 V3 (or earlier)         |             |

| Programming a Personality Using TQ-3357 Version 4.03 (or later) |             |

| MAINTENANCE                                                     |             |

| SUBASSEMBLY REMOVAL AND REPLACEMENT                             |             |

| Replacing a 19D904266 or 19D902104 Logic Board                  |             |

| Replacing a 188D6500Gx Logic Board                              |             |

| Turbo Board                                                     |             |

| Rockwell Modem                                                  |             |

| Power Supply, A2                                                |             |

| TEST AND ALIGNMENT                                              |             |

| GETC TESTING.                                                   |             |

| Test Fauinment Required                                         | 35          |

## TABLE OF CONTENTS Section/Paragraph Page Input Buffer And Port Pins Test .......45 ON SITE TROUBLESHOOTING.......48 Installation 49

# LBI-39203E

| TABLE OF FIGURES                                                                    | Dara       |

|-------------------------------------------------------------------------------------|------------|

| <u>Figure</u> <u>Title</u>                                                          | <u>Pag</u> |

| Figure 1 - Typical GETC Shelf With Logic Board, Regulator Assembly, And Turbo Board | 9          |

| Figure 2 - GETC Front Panel Indicators                                              | 10         |

| Figure 3 - Turbo Board                                                              | 1          |

| Figure 4 - Reset Circuit                                                            | 13         |

| Figure 5a - Simplified GETC Block Diagram                                           | 14         |

| Figure 5b - Simplified GETC Block Diagram                                           | 15         |

| Figure 6 - Clock Circuit                                                            | 10         |

| Figure 7 - Dip Switches Shown In Programming Mode                                   |            |

| Figure 8 - Five-Volt Regulator Circuit                                              |            |

| Figure 9 - Oscillator/Inverter Regulated ±12 V Power Supply Circuit                 |            |

| Figure 10 - Low Speed Data Encode Filter                                            |            |

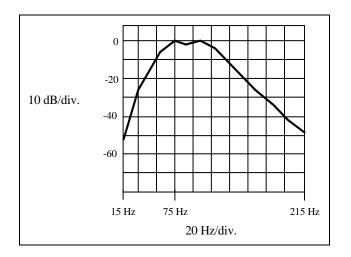

| Figure 11 - Lsd Encode/Decode Filter Response                                       |            |

| Figure 12 - Low Speed Data Decode Filter                                            |            |

| Figure 13 - Lsd Decode Filter Response Using Roa 117 2238 Filter Board              |            |

| Figure 14 - High Speed Data Transmit Filter                                         |            |

| Figure 15 - High Speed Data Detector                                                |            |

| Figure 16 - Rockwell Modem And Telephone Interface                                  | 23         |

| Figure 17 - GETC Data Sent To Site Controller                                       | 20         |

| Figure 18 - Site Controller Or BSL Data Sent To GETC                                |            |

| Figure 19 - Frame Sync Line Circuit                                                 |            |

| Figure 20 - System Hook-Up Using J100                                               |            |

| Figure 21 - System Hook-Up Using J104                                               |            |

| Figure 22 - Terminal-To-GETC Connection Cable                                       |            |

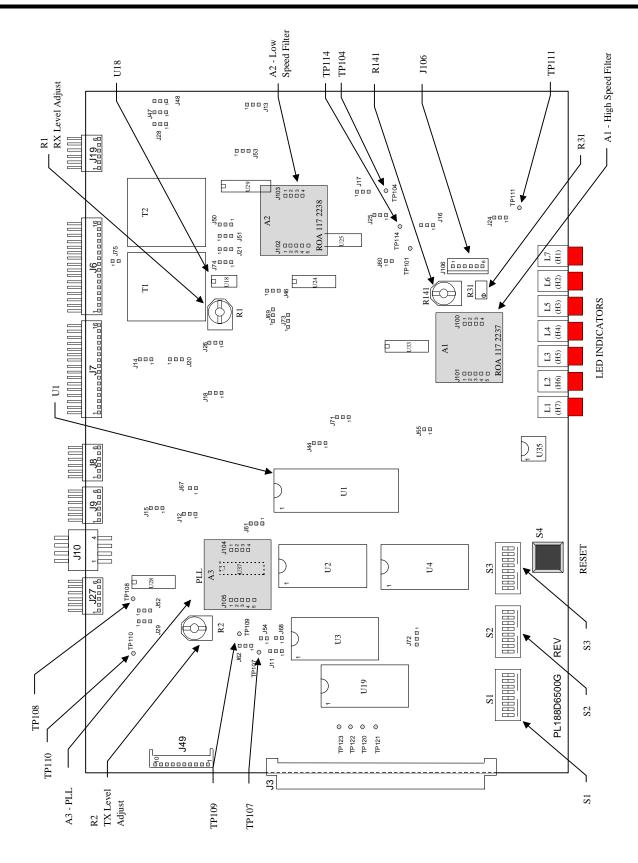

| Figure 23 - Station GETC (188d6500) Jumper And Test Point Locations                 |            |

| Figure 24 - Lightning-Protection Kit Installation Detail                            |            |

| Figure 25 - Lightning-Protection Kit Cabinet Installation                           |            |

| LIST OF TABLES                                      |             |  |  |

|-----------------------------------------------------|-------------|--|--|

| <u>Table</u> <u>Title</u>                           | <u>Page</u> |  |  |

| Table 1 - Interface Connections                     | 12          |  |  |

| Table 2 - Device Addresses                          |             |  |  |

| Table 3 - Decoding Scheme                           | 27          |  |  |

| Table 4 - Indicators In Programming Mode Using J100 | 30          |  |  |

| Table 5 - Indicators In Programming Mode Using J104 | 31          |  |  |

| Table 6 - GETC And RS-232C Pin Assignments          | 36          |  |  |

| Table 7 - GETC Logic Board Jumper Configuration     | 37          |  |  |

## **SPECIFICATIONS\***

# <u>ITEM</u> <u>SPECIFICATION</u>

INPUT VOLTAGE +13.8 ±20% Vdc

**CURRENT DRAIN**

Without 9600 baud modem 900 mA (typical), 1.5 A (maximum) With 9600 baud modem 1.5 A (typical), 2 A (maximum)

OPERATING TEMPERATURE  $-22^{\circ}\text{F to} + 140^{\circ}\text{F} (-30^{\circ}\text{C to} + 60^{\circ}\text{C})$

DIMENSIONS (H x W) 1.75 x 19 inches (4.5 x 48.3 cm)

DATA TRANSMISSION

High Speed 9600  $\pm 1$  bps (EDACS<sup>®</sup> Wideband) 4800  $\pm 1$  bps (EDACS Narrow band)

Low Speed  $150 \pm 1 \text{ bps}$

COMMUNICATION INTERFACE

Site Controller (Trunked)

Protocol RS-232C

Data Format 1 start bit, 1 stop bit, and 8 data bits

Data Rate 19.2 kilobaud

Back-up Serial Link (Failsoft)

Data Levels 0 to 13.8 Vdc swing (nominal)

Data Format 1 start bit, 1 stop bit, and 8/9 data bits

Data Rate 19.2 kilobaud

<sup>\*</sup> These specifications are intended for use during servicing. Refer to the appropriate Specification Sheet for the complete Specification.

#### RELATED PUBLICATIONS

The GETC is used in several applications, which LBI-38987 - EDACS Single Channel Autonomous Trunking (SCAT) GETC and Downlink broadly includes voting, Enhanced Digital Access **GETC Configuration Manual** Communications Systems (EDACS<sup>®</sup>), Aegis<sup>™</sup>, and Digital Voice. In each of these applications the same GETC is - EDACS Station GETC Configuration used, however, the Logic Board operates differently LBI-38988 Manual because of different jumper configurations, interfacing hardware, and software. Refer to the appropriate technical - EDACS Test Unit and Alarm Interface LBI-38989 manual for additional information on each application. (TUAI) GETC Configuration Manual LBI-33031 - Rockwell Modem 19A705178 (Model LBI-39004 - EDACS Guardog Installation and Operation R96FT) Manual LBI-31981 - Digital Voice Voting Tone Board SRN-1002 - Software Release Notes for GETC 1e Maintenance Manual Software, 19A149256G22 - Software Release Notes for GETC Turbo - EDACS Voter Interface Board Maintenance SRN-1010 LBI-38462 Board Software (344A4414G1 only) Manual - Software Release Notes for GETC 900 SRN-1024 - Turbo Board (GETC 1e) Maintenance LBI-38822 MHz Software, 19A705595G8 Manual - Software Release Notes for GETC 1e SRN-1060 LBI-38894 - GETC Trunking Card 19D904266G1 and Software, 349A9607G5 G4 Maintenance Manual SRN-1061 - Software Release Notes for Link Software. LBI-38174 - GETC Trunking Card 19D902104G1 344A4895G1 (or later) and Link Turbo Maintenance Manual Software 350A1121G4 (or later). LBI-38896 - EDACS Site Downlink and CEC/IMC SRN-1062 - Software Release Notes for GETC Turbo **Uplink Configuration Manual** Board Software (344A4414G2 or later) LBI-38954 - EDACS Voter Digital Receiver and TQ-3357 - GETC Shelf Programming Manual Selector GETC Configuration Manual LBI-38985 - EDACS Site Controller Maintenance Manual

LBI-38986

- GETC Conventional Network Interface

(CNI) Configuration Manual

## INTRODUCTION

This manual contains maintenance and servicing information for the M/A-COM Generic EDACS Trunking Card (GETC) Shelf Assembly 19D901868G5 and G6. Typically, all production models of the shelf consist of the following subassemblies:

- Logic Board (A1) ......188D6500G1 or G4

- Regulator Assembly (A2)...... 19C336816G2

#### **IDENTIFICATION**

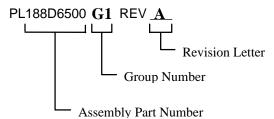

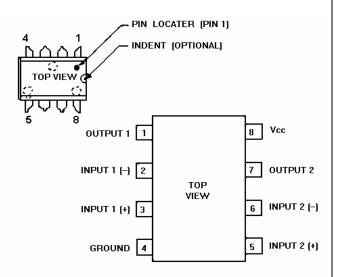

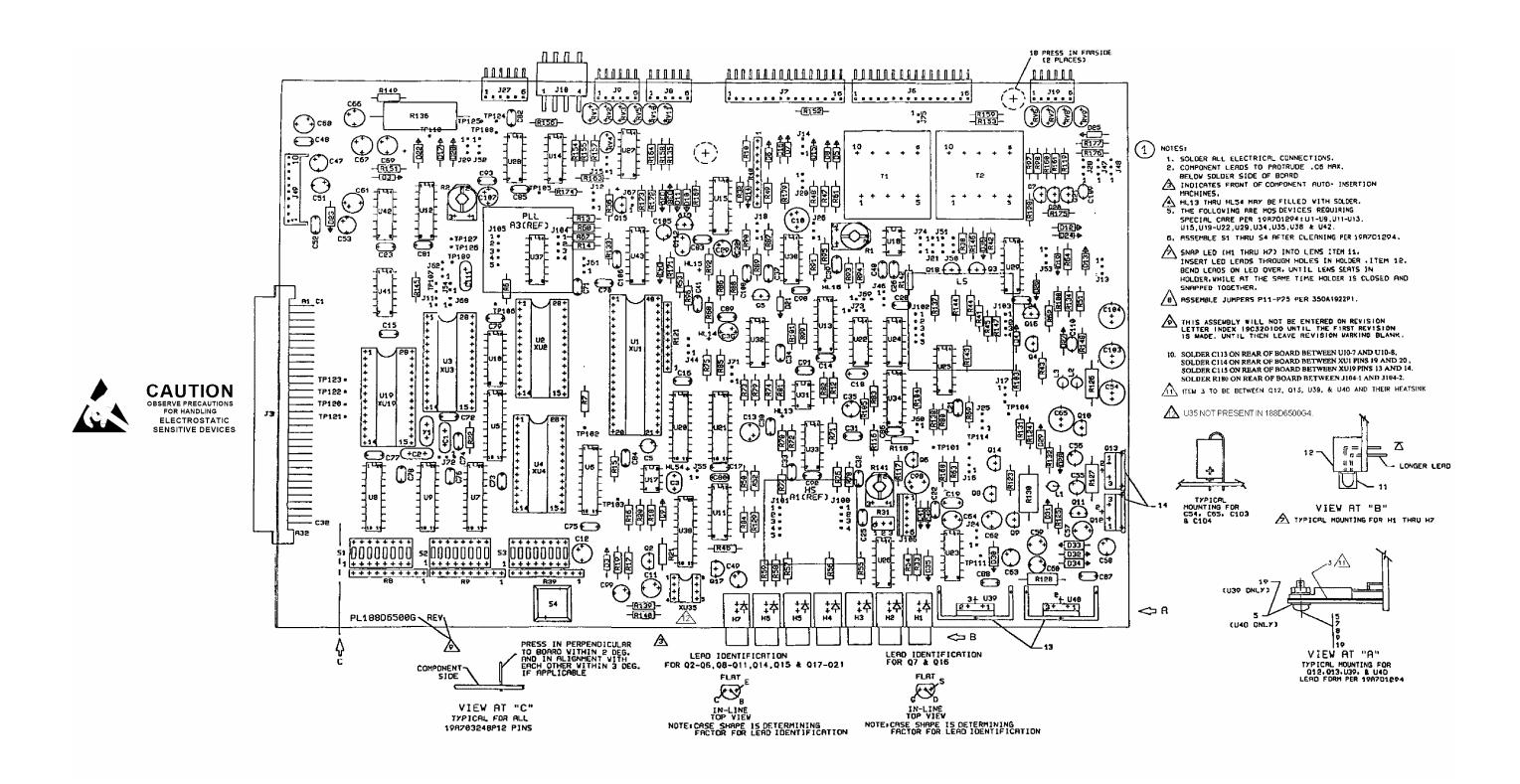

To properly identify the board, locate the "PL" number silk-screened on the logic board. Look for the designation

(as shown below) on the left side of the logic board, toward the front of the GETC shelf, and just below the three DIP switches.

Use the Assembly Part Number to determine the applicable maintenance manual. A Revision Letter stamped on the board indicates an improvement or production change. Refer to the Production Change section (located after the Parts List) for a description of the changes and affected parts.

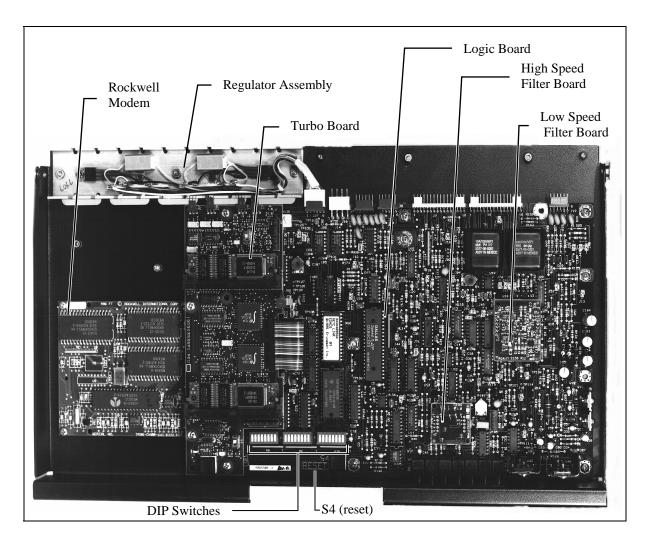

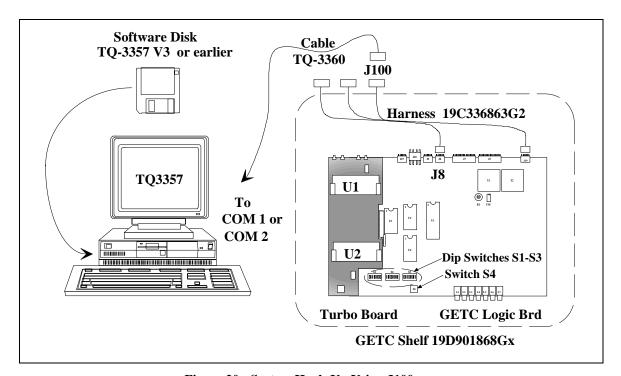

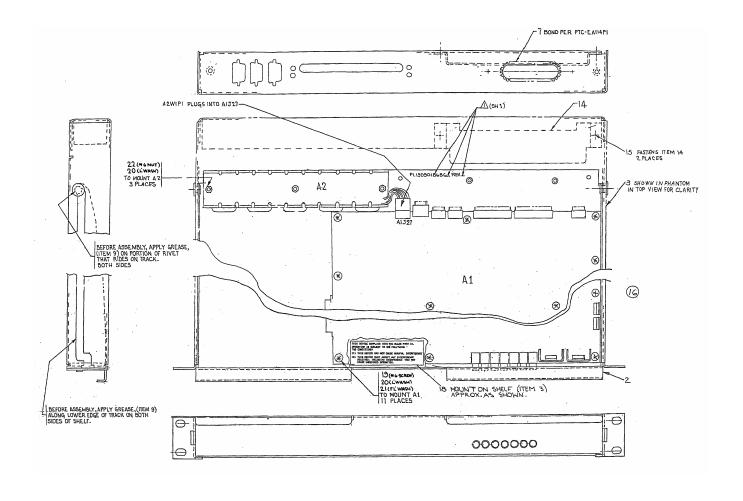

Figure 1 - Typical GETC Shelf With Logic Board, Regulator Assembly, and Turbo Board

## **DESCRIPTION**

The GETC is essentially a processor board with audio filtering and specialized I/O capability. Because of this flexibility in design, the GETC can be integrated into many applications.

The Logic Board, Regulator Board, Turbo Board, and Modem are mounted on a tray and enclosed in a slide-out shelf as shown in Figure 1. The GETC Shelf is a one-rack-unit assembly (1.75-inches x 19-inches) which is mounted in a standard 19-inch wide equipment cabinet.

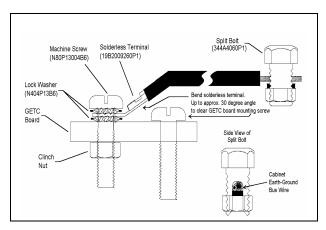

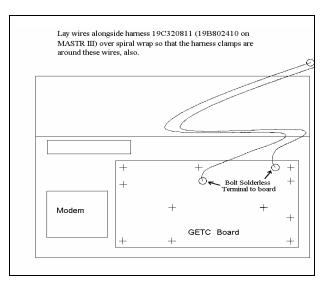

The GETC Logic Board uses Metal-Oxide Varistors (MOV's) for lightning protection on all RS-232C inputs and outputs. However, maximum lightning protection is achieved when the GETC is grounded to the cabinet earthground using the GETC Lightning-Protection Circuitry Grounding Kit 344A4500 and the Cabinet Grounding Strap Kit 344A4730. Specific details for installing these grounding kits are found in the Modifications section of this manual.

#### CONTROLS AND INDICATORS

This section describes the controls and indicators for the GETC.

## **Front Panel Indicators**

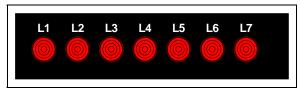

The following controls and indicators are on the GETC Logic Board. Refer to Figure 2.

L1 thru L7 - The seven front panel LED indicators (L1 thru L7) display the state of operation of the GETC. The interpretation of the indicators depends on the system application (refer to the configuration manual for the specific application).

**Figure 2 - GETC Front Panel Indicators**

## **Controls**

The following controls are found on the GETC board as shown in Figure 1:

• S1, S2, S3 (DIP Switches) - Used to set the GETC's operating mode and parameters.

S4 (RESET) - Pushbutton S4 allows the technician to manually reinitialize the GETC.

#### **OPTIONS**

Depending on the application, the GETC may be equipped with one or more of the following optional boards:

- □ Turbo Board .......19D903536P1

□ Rockwell Modem Board......19A705178

- ☐ Low Speed Data Filter.....ROA 117 2238

- ☐ High Speed Data Filter..... See below

- ROA 117 2237/1 9600 Baud, Wide Band

- ROA 117 2237/2 4800 Baud, Narrowband

- ROA 117 2237/3 ETSI Wide Band

- ROA 117 2237/4 ETSI Narrow Band

- ROA 117 2314/1 9600 Baud, Narrow Band

#### **NOTE**

GETCs with the "MODIFIED FOR EUROPEAN OPERATION" label must use High Speed Filter ROA 117 2237/3 or /4 to be ETSI (European Technical Standards Institute) compliant for adjacent channel power requirements. Refer to LBI-39204 for technical details on the High Speed Filter boards.

In addition to optional boards, the GETC may be equipped with different or modified interface cables. Consult the specific GETC installation manual and application specific manuals whenever field maintenance is performed on the GETC.

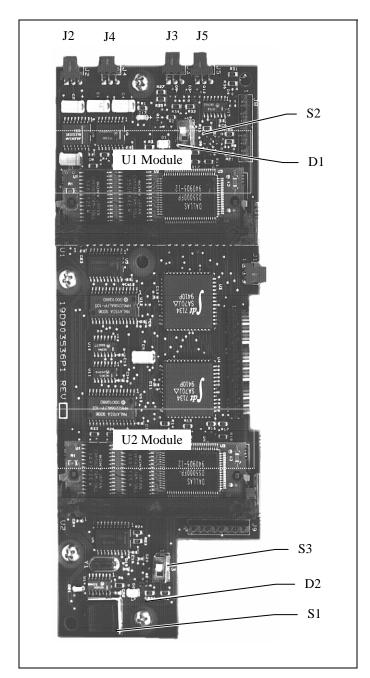

## Turbo Board

The Turbo Board, shown in Figure 3, provides the GETC with additional processing power and memory. The Turbo Board is connected to the GETC via a ribbon cable from J1 on the Turbo Board to the XU3 socket on the GETC Board.

Since the Turbo Board is used to store the GETCs personality programming, U35 is no longer required and is normally removed from the GETC.

The following controls and indicators are located on the Turbo Board:

• S1 (RESET) - Pushbutton S1 allows the technician to manually reinitialize the Turbo Board.

- S2 and S3 Slide switches S2 and S3 are used to select the run or load mode for Turbo Board microprocessors U1 and U2, respectively.

- D1 and D2 Indicate whether the Turbo board microprocessors are in the programming (OFF) or run (ON) mode.

Figure 3 - Turbo Board

#### ROCKWELL MODEM BOARD

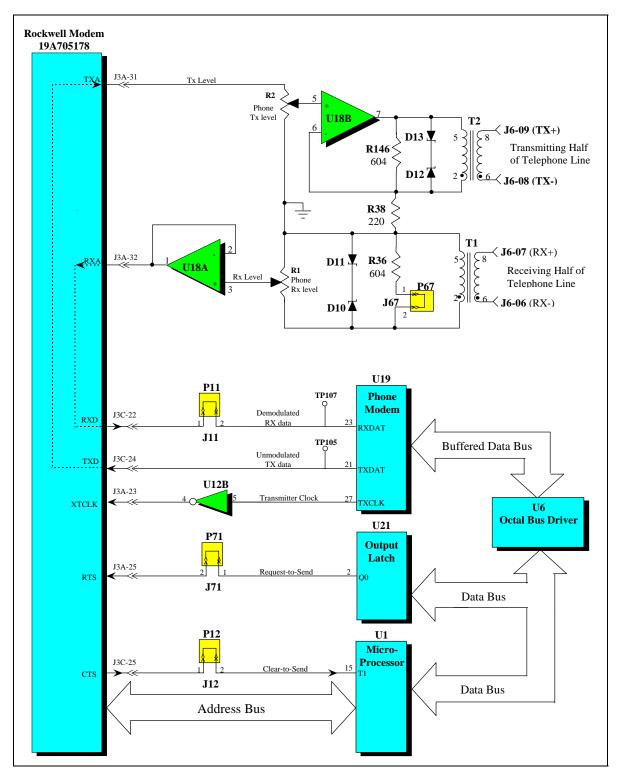

The 9600 Baud Rockwell Modem Board, 19A705178, is used in the GETC shelf to generate a fast-train, synchronous, serial data stream suitable for transmission over audio (phone) lines or microwave. The data stream is sent to a full-duplex, four-wire, dedicated 3002 grade telephone line.

Receive and transmit Phone Line Data lines (J6-6,7,8,9,) are two balanced pairs carrying Modem data to and from the station where the data is combined with station (voice) audio and routed to the Remote Line input and Line output.

In addition to the GETC provided transformer isolation and conditioning, the modem provides automatic adaptive signal equalization allowing normal operation using input signal levels from -40 dBm to 0 dBm. The Rockwell Modem demodulates the input signal and the resulting data is transferred using a serial interface between the Rockwell Modem and GETC. The physical connections for the interface are at J3C-22, J11-1, J11-2, and U19-19.

The modem senses a received signal by initiating a training state upon detecting an increase in the input signal level. The modem begins processing data at the end of the training state if the input signal is still above the nominal -40 dBm receiving threshold value. Otherwise, the modem returns to an idle mode at the end of the training state if the input signal is below the nominal receiving threshold value.

The duration of the modem's training state is determined through GETC control signals at the time of power up. Resetting the GETC (pressing S4) or cycling the GETC Shelf's operating power initializes the Rockwell Modem for proper operation.

#### INTERFACE POINTS

There are ten connectors on the GETC board used for interface connections. These connectors are identified in Table 1.

**Table 1 - Interface Connections**

| CONNECTOR | INTERFACE CONNECTION                                         |  |

|-----------|--------------------------------------------------------------|--|

| Ј3        | 9600 baud (Rockwell Modem)<br>Interface.                     |  |

| J27       | Regulator board interface.                                   |  |

| J49       | Voting board interface.                                      |  |

| J10       | 13.8 Vdc power connection                                    |  |

| J9        | External modem interface                                     |  |

| Ј8        | Site Controller interface                                    |  |

| J7        | RF station interface                                         |  |

| J6        | RF station interface                                         |  |

| J19       | Site Controller interface                                    |  |

| XU3       | Turbo Board Interface                                        |  |

| J102/J103 | Low Speed Filter Board Interface                             |  |

| J100/J101 | High Speed Filter Board Interface                            |  |

| J104/J105 | PLL Board Interface                                          |  |

| J106      | Remote Reset and Failsoft<br>Monitor (Guardog <sup>™</sup> ) |  |

#### **GETC COMMUNICATION LINKS**

The following are communication modes available to the GETC:

- (1) The GETC can communicate with other devices such as the Site Controller, IMC, and RF station. Communication occurs primarily through an RS-232C serial interface normally operating at 19.2 kilobaud. For GETCs interfacing with a SIM (Site Interface Module) this is set to 38.4 kilobaud.

- (2) The GETC can communicate with other GETCs, in the Failsoft mode of operation, over a backup serial link (BSL). The link uses 0-13.8 Vdc levels and operates at 19.2 kilobaud and is ordinarily used in a bus configuration. For GETCs interfacing with a SIM (Site Interface Module) this is set to 38.4 kilobaud.

- (3) A timing signal called the Frame Sync Line (FSL) helps arbitrate the use of the BSL serial bus in the Voter configuration. The FSL is also used for timing purposes. In the Station configuration, FSL signals use 0-13 Vdc levels to produce a periodic negative going pulse.

- (4) A 9600/4800 baud full-duplex, synchronous communication interface over an RF channel.

- (5) A 9600 baud phone line or microwave communication interface (this may be RS232 or modem data) through a Rockwell modem.

#### **NOTE**

GETC interface functions vary from application to application and between EDACS systems using a MASTR® II or MASTR III repeaters. Therefore, it is necessary to refer to the application's configuration manual for details regarding the specific hardware and software configuration of the GETC.

## CIRCUIT ANALYSIS

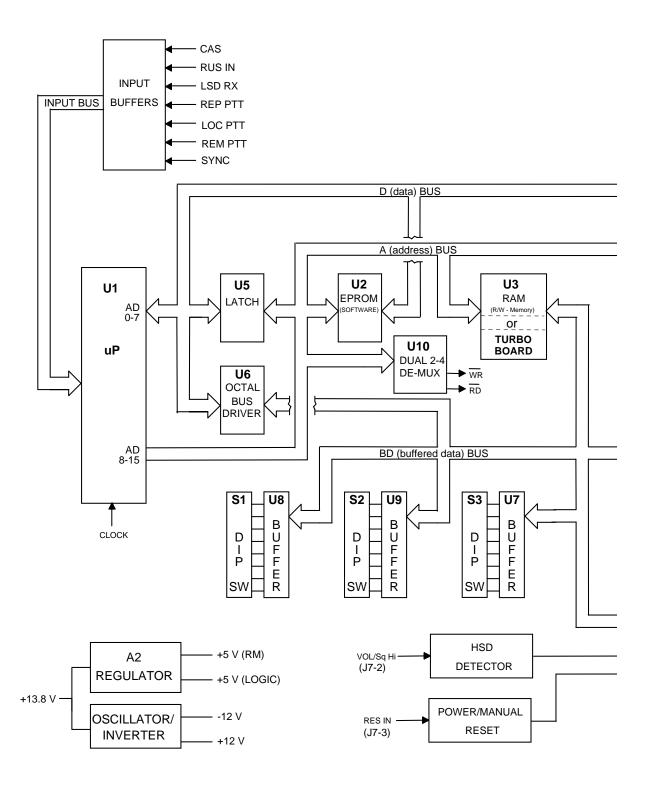

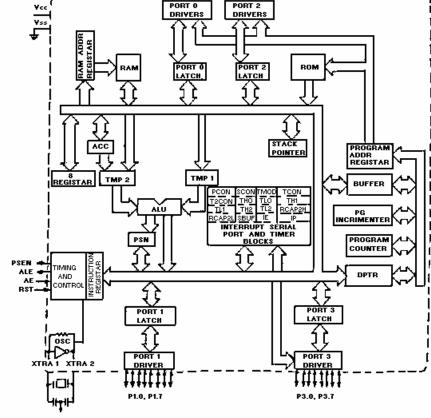

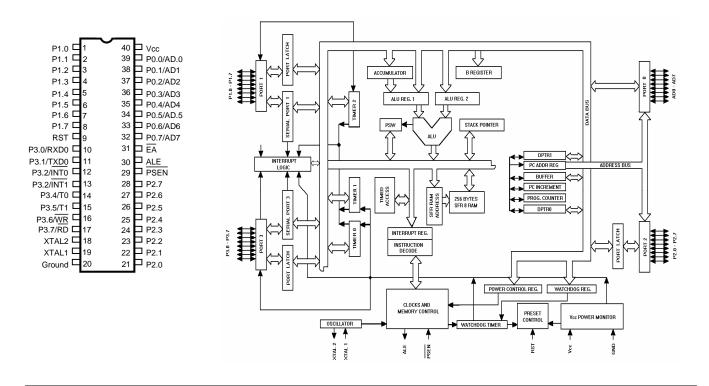

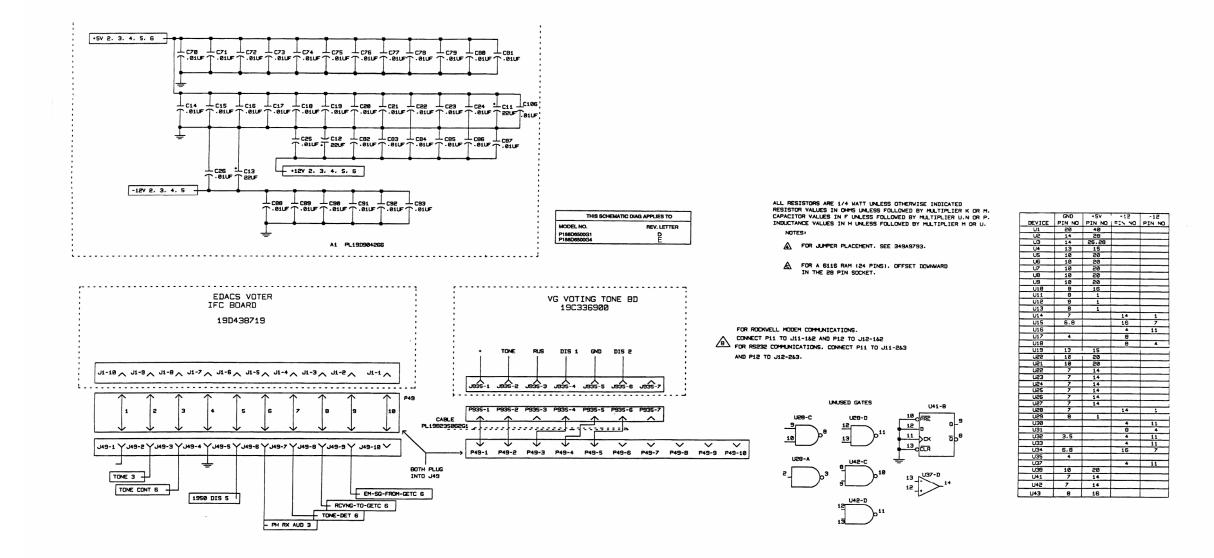

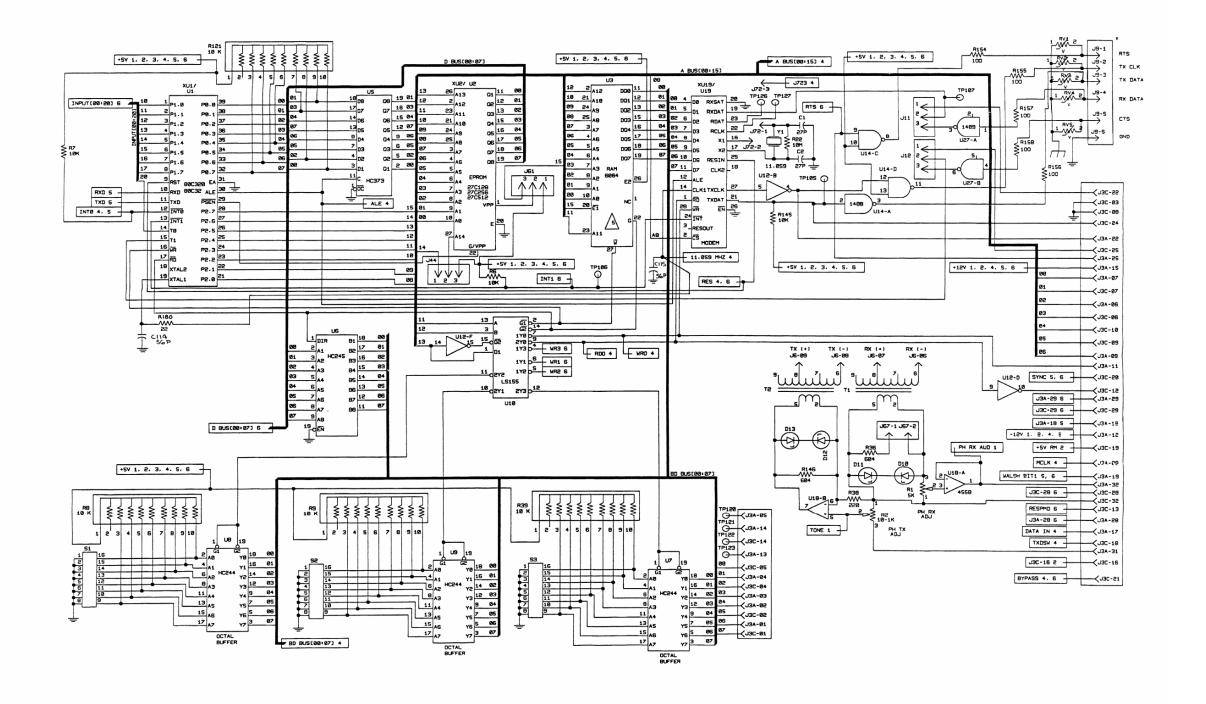

Theory of operation for each circuit card assembly and module used in GETC shelf is described in the following paragraphs. Refer to the schematic diagram 188D6822 and block diagram (Figure 5).

#### **GETC LOGIC BOARD**

The logic board contains all GETC functions except the power supply, Rockwell Modem, and Turbo processor and memory.

## **Reset Circuitry**

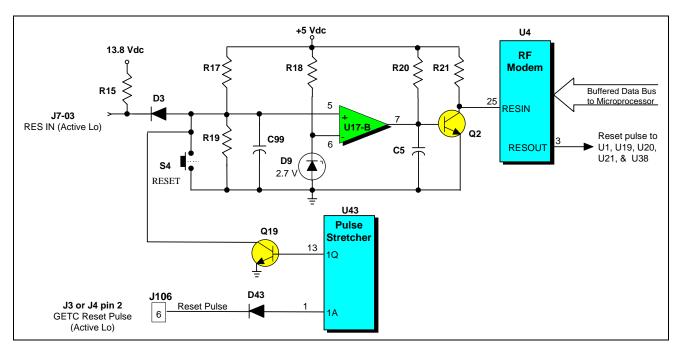

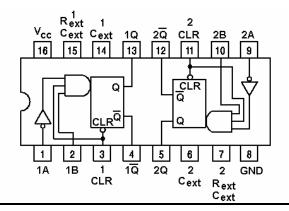

The GETC Logic board contains a Power-on/Manual reset for initializing the programmed code and hardware devices on the board. The reset circuit (Figure 4) consists of a comparator U17B, Zener diode D9, RESET switch S4, driver Q2, and associated circuitry.

A GETC reset may be initiated in one of five ways:

- 1. During power-on.

- 2. By manually pressing S4.

- 3. By the watchdog timer in U4.

- 4. By a constant low from an external device.

- 5. By a momentary low from an external device.

During power-on, the comparator U17B compares the +5.0 Vdc line with a reference level to generate a reset to the GETC logic board.

A reference level of 2.7 Vdc is set up on pin 6 of the comparator by Zener diode D9. After power-up, the steady-state level on pin 5 is set to 3.2 volts by the resistor divider (R17 and R19). The output of comparator U17B is pulled up through resistor R20. Normally, Q2 is on and the base-emitter junction clamps U17-7 to +0.8 Vdc.

When the RESET button S4 is pressed, U17-5 goes to ground and the comparator output (U17-7) goes to zero (0) volts (nominal logic 0) turning transistor Q2 off. The collector of Q2 is pulled high by R21, sending a pulse to the reset input (RES IN) of the modem (U4-25). The modem RES OUT line (U4-3) is the logical-OR of the RES IN line and the internal watchdog-timer pulse (if not serviced by microcomputer U1).

The reset out (RES OUT) of the modem is sent to the microcomputer and other logic devices on the GETC logic board. When the RESET button is released, the level on U17-5 returns to +3.2 volts after C99 charges. The comparator output (U17-7) turns off, allowing the base of Q2 to be pulled high (to 0.8 volt) as C5 charges. The time constant set up by R20 and C5, results in a 140 millisecond turn-on delay for Q2. After the reset pulse is gone, the microcomputer restarts operation from program counter address 0.

Figure 4 - Reset Circuit

Figure 5A - Simplified GETC Block Diagram

Figure 5B - Simplified GETC Block Diagram

A reset may occur automatically if the microcomputer fails to service the watchdog timer in modem U4. This reset will occur if the microcomputer misses a service for a two-second period (jumper P62 on J62 pins 1 & 2) or a four-second period (P62 on J62 pins 2 & 3).

A reset may also be generated by an external device. The external device resets the GETC by applying a logic low on J7-3, which is diode-coupled (D3) to the comparator. The reset circuit then operates as described for the RESET switch (S4).

A monetary low on J106-6 triggers one-shot U43. Its Q output goes high for approximately 100 ms, turning on Q19. Q19-C is wire OR'ed with the other RESET inputs at U17-5. From here, the RESET circuit acts just as it does for the other RESET inputs.

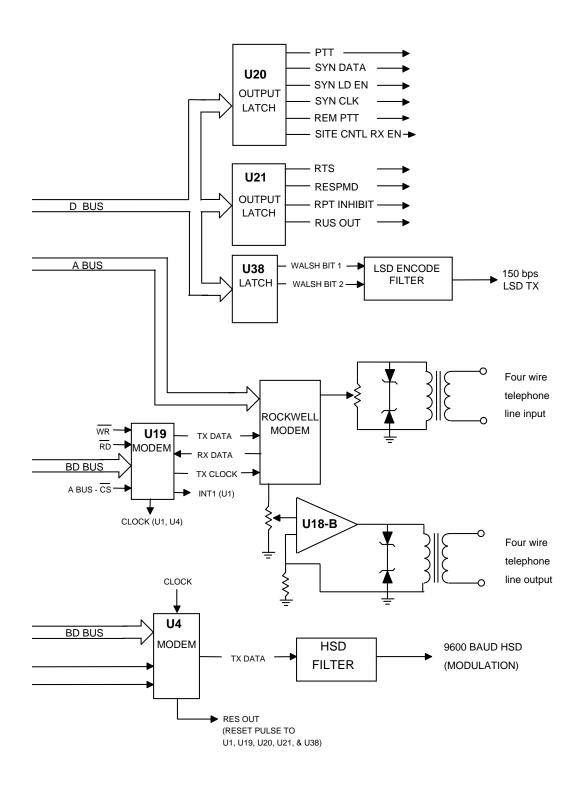

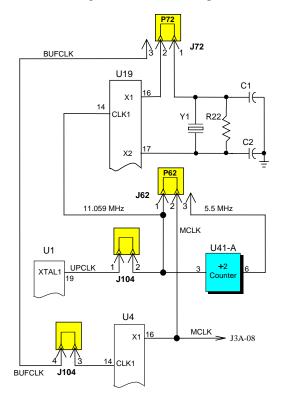

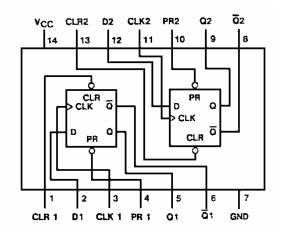

## **Clock Circuitry**

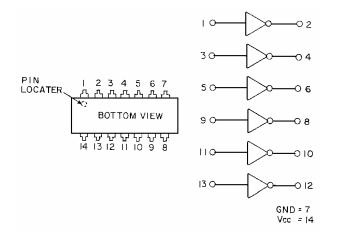

The internal clock for the GETC logic board originates in Phone modem U19. The clock oscillator consists of crystal Y1, modem U19, and associated circuitry (see Figure 6). The oscillator circuit runs at 11.0592 MHz as determined by crystal Y1. The CLK 1 line (U19-14) output provides the clock signals to the microcomputer (U1)

Figure 6 - Clock Circuit

For 9600 baud (wideband) operation, a jumper P62 is placed on J62 pins 1 & 2. For 4800 baud (narrowband) operation, J62 pins 2 & 3 are jumpered, this routes the clock signal through the divide-by-two counter (U41-A) to generate a 5.5296 MHz clock. The 11.0592 MHz ( or 5.5296 MHz) clock signal (MCLK) from J62 pin 2 is routed to the RF modem (U4-16).

For Simulcast system operation or other applications using an external reference clock, the jumper P72 is placed on J72 pins 2 & 3 and the jumper on J62 is removed. This routes the external clock signal (MCLK) from J3A-08 to the RF data modem. The amplified output signal (BUFCLK) is then routed to the Phone modem U19-16. U19 buffers the signal which is then routed to the microprocessor U1.

Future Simulcast installations may require using the 9600 Hz signal from the T1 mux as the external clock signal. This signal will input at J19-3 and be routed to J105-4. The PLL daughter board will be installed on connectors J104 and J105. This board will develop an 11.0592 MHz clock (BUFCLK) based the external 9600 Hz reference signal. The BUFCLK signal will then be routed through J72-2 and 3 to the Phone Modem U19.

## **Jumper Configuration**

There are several jumpers on the GETC logic board used for configuring the GETC for different applications. For the proper jumper settings, always refer to the Software Release Notes covering the specific application and software version.

#### **NOTE**

Jumper settings contained in this manual are for bench test and alignment only. Refer to applicable SRN for operational jumper configuration.

## **Switch Settings**

There are three eight-position DIP switches (S1 thru S3) located on the GETC logic board. These switches are used to configure the GETC for different applications, such as testing, programming, or operation. Refer to the Software Release Notes for the specific application when setting the DIP switches.

#### **NOTE**

DIP switch settings contained in this manual are for test and alignment only. Refer to applicable SRN for operational DIP switch configuration.

Figure 7 - DIP Switches Shown in Programming Mode

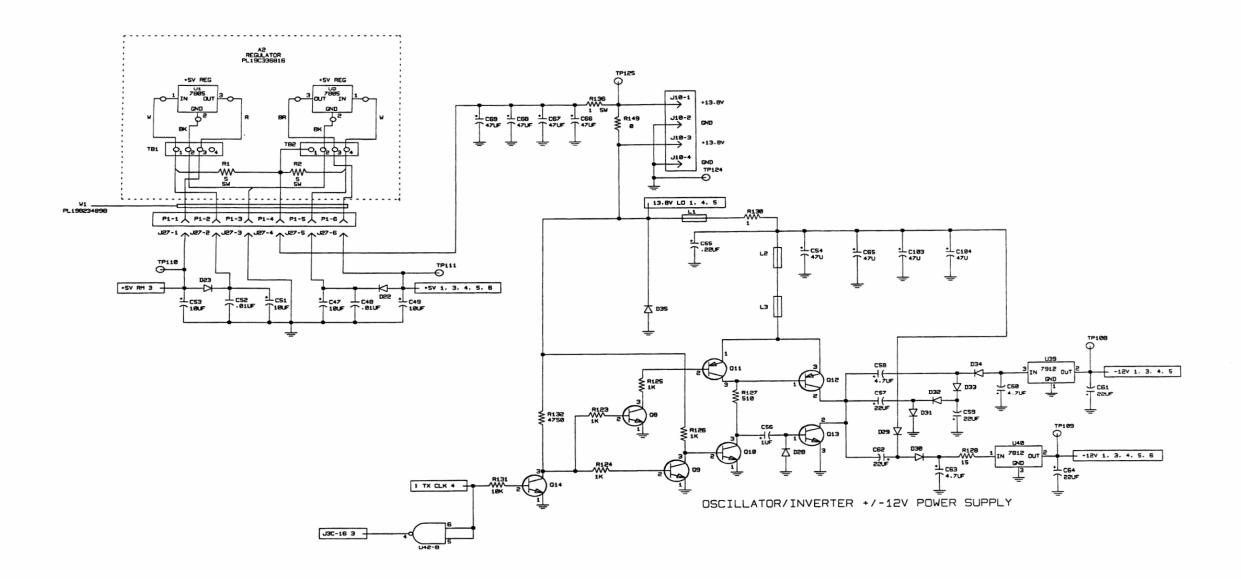

## **Power Supplies And Regulators**

The GETC receives its primary power from the station power supply (13.8 volt nominal) through connector J10-1. Regulated +5.0 volts, +12.0 volts and the -12.0 volts are derived from this source.

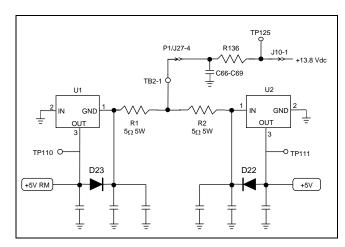

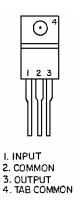

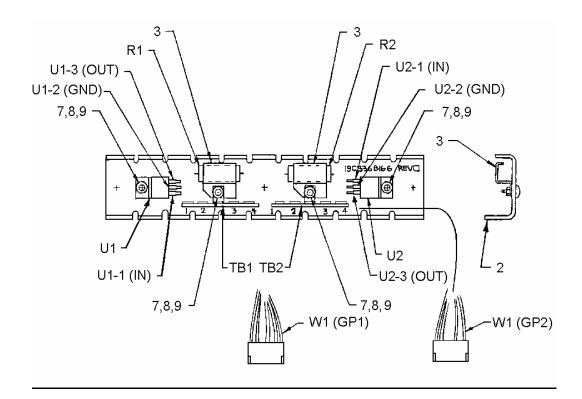

Generation of the regulated +5.0 volts is accomplished through the Regulator Assembly (19C336816G2). This assembly (Figure 8) gets 13.8-volt station power through connector J27-4. Regulated +5.0 volts is returned to the GETC logic board devices through J27-6. Regulated +5.0

Figure 8 - Five-Volt Regulator Circuit

volts used to power the 9600 baud Rockwell Modem is returned at connector J27-1.

Resistors R1 and R2 are used to lower the voltage across the regulators, reducing their dissipation. Terminal strips TB1 and TB2 serve as interconnect points for the harness (W1) that mates into the GETC logic board (P1/J27).

Regulator U2 is the power source for the GETC logic board devices, while U1 is the power source for the 9600

Figure 9 - Oscillator/Inverter Regulated ±12 V Power Supply Circuit

baud modem board. Ripple filtering for the +5.0 volt regulators is provided on the GETC logic board by capacitors C47 thru C49 and C51 thru C53. Diodes D22 and D23 provide back-bias protection on the +5 volt power regulators.

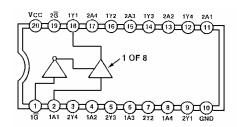

Regulated +12.0 and -12.0 volts are generated using the oscillator-inverter circuitry. These sources supply power to the analog circuits and RS-232C driver devices on the GETC Logic Board, as well as the 9600 baud Rockwell Modem.

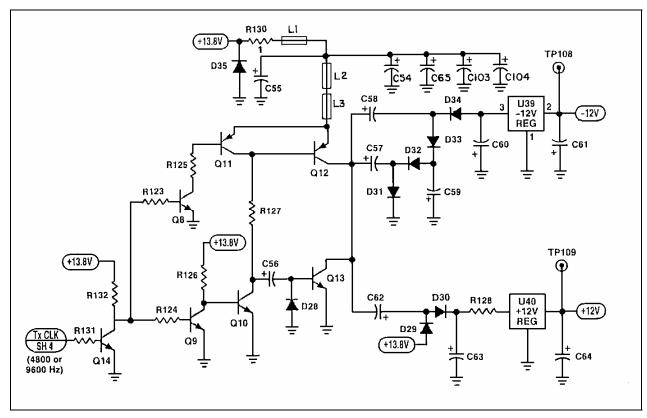

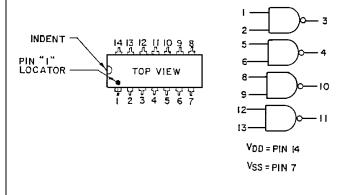

The oscillator-inverter circuit, shown in Figure 9, obtains a 9600 Hz (or 4800 Hz if P62 is on pins J62-2 & 3) square wave input from modem U4-27, which is sent to the base of transistor Q14. Transistor Q14 translates the TTL square wave to a 0 to 13.8 volt square wave. Transistor Q8 and O9 provide additional buffering to drive O11 and O10, respectively. Transistor Q11 and Q10 drive Q12 and Q13 to obtain a push-pull, high-level drive output. Capacitor C56 and diode D28 are used to quickly turn off Q13. The output at the collectors of transistors Q12 and Q13 is a high-drive 9600 Hz (4800 Hz if P62 is on pins J62-2 & 3) square wave which swings from 0 to 13.8 volts. Capacitors C57 thru C60 and diodes D31 thru D34 comprise a negative voltage doubler, which maintains a nominal value of -23 volts to the input of the negative voltage regulator U39. Capacitors C62 and C63, and diodes D29 and D30 comprise a positive voltage doubler, which maintains a nominal value of +25 volts to the input of the positive voltage regulator U40. Resistor R128 is used as a current limiting resistor to reduce the case temperature of regulator U40.

The two voltage regulator, U39 and U40, reduce the input voltage to obtain a regulated -12.0 volts and a regulated +12.0 volts, respectively. Capacitors C61 and C64 provide additional ripple filtering on the -12.0 and +12.0 volt lines.

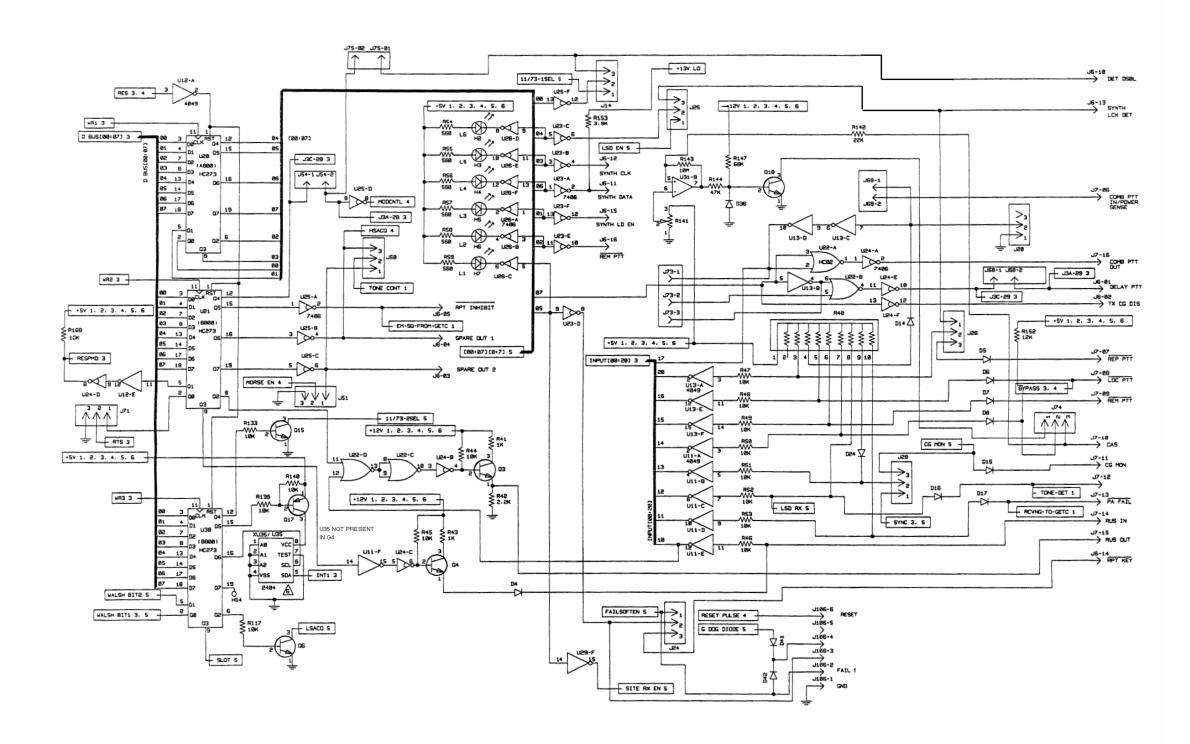

#### **Logic**

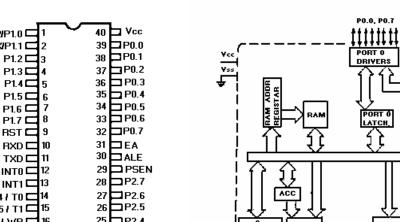

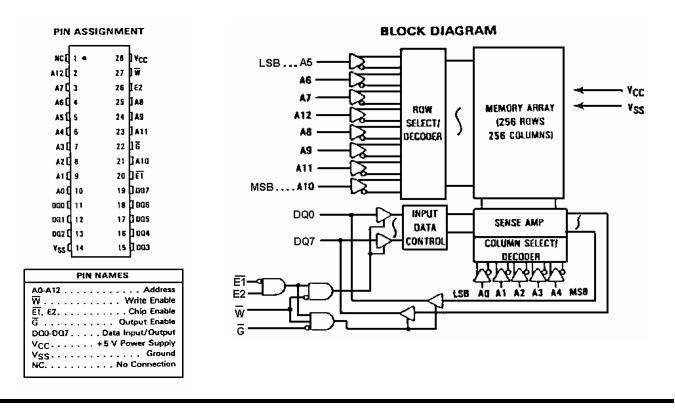

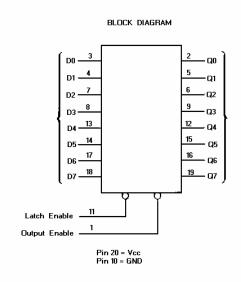

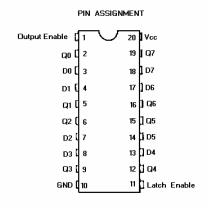

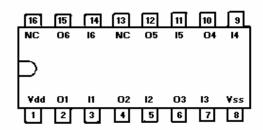

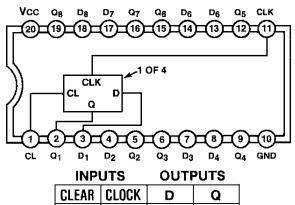

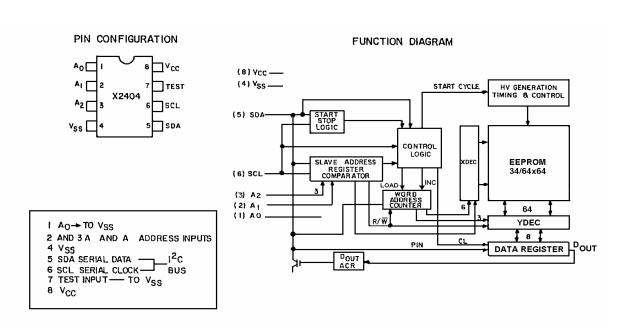

The GETC Logic board provides the station control and interfacing in the system. The main controller on the GETC shelf is the microcomputer (U1) found on the GETC logic board. The microcomputer obtains its instructions from the program stored in PROM U2. The upper eight address lines of the microcomputer (U1) go directly to the PROM, while the lower address lines are latched into register U5. The output of U5 supplies the lower eight address lines to the PROM. The microcomputer accesses the data from the PROM using the control line PSEN (Program Store Enable) on U2-22. An external RAM (U3) (or Turbo Board when installed) holds data and tables. The address lines to the RAM are identical to that of PROM U2.

Microcomputer U1 accesses the Phone modem (U19) to interface to the 9600 baud Modem board or 9600 baud RS-232 link. This provides a remote data interface. The RF modem U4 provides the high-speed data encode to the station transmitter, as well as the high-speed data decode from the station receiver.

The configuration of the GETC is partly determined by the settings of DIP switches S1 thru S3. The microcomputer reads these settings via octal buffers U7 thru U9. Resistor packs R8, R9, and R39 are pull-ups for the switch lines.

The microcomputer accesses data to or from RAM (U3), Phone modem U19, RF modem U4, and octal buffers U7 thru U9, via the octal bus transceiver U6. The transceiver, when directed by the microcomputer read command (RD at U1 pin 19) transfers the data from the switches, RAM and BD (buffered data) Bus to the D(data) Bus. Data going to or from the PROM, and octal latches U20, U21, and U38 is handled by the D (data) bus.

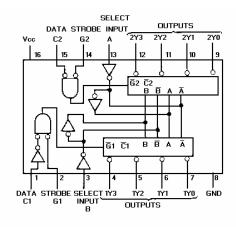

Program memory is selected by the PSEN(-) strobe (U1-29). Address Latch Enable (ALE) addresses the devices on the A (address) bus by latching the lower eight bits of the address through U5. The upper eight bits of the address are sent directly to the devices. The two-to-four demux/decoder (U10) is used to decode the upper address lines (A11 thru A13). When gated by RD(-) or WR(-), the demux/decoder enables the desired device to transmit or receive data. The devices on the microcomputer bus are addressed according to Table 2.

**Table 2 - Device Addresses**

| DEVICE          | HEXADECIMAL ADDRESS |  |  |

|-----------------|---------------------|--|--|

| U3              | 0000 - 1FFF         |  |  |

| U4              | A170 - A172         |  |  |

| U7              | B800                |  |  |

| U8              | B000                |  |  |

| U9              | A800                |  |  |

| U19             | A0F0 - A0F2         |  |  |

| U20             | A800                |  |  |

| U21             | B000                |  |  |

| U38             | B800                |  |  |

| 9600 baud modem | A1E7                |  |  |

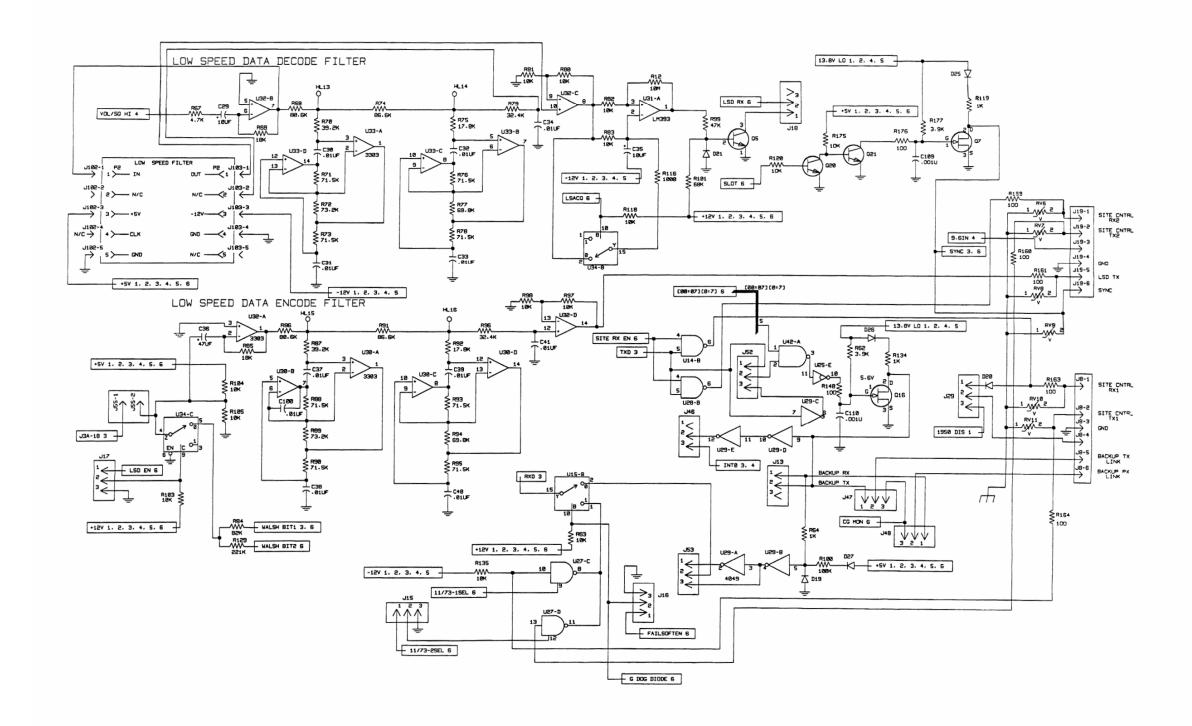

### **Low-Speed Data Encode Filter**

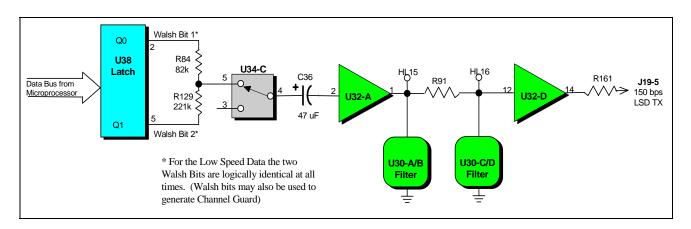

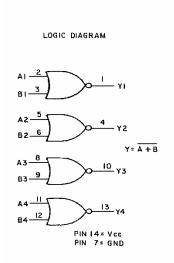

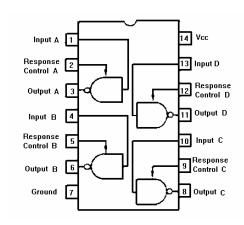

The low-speed-data encode filter (Figure 10) is comprised of U30, U32A, U32D, and associated circuitry. This filter is a low-frequency response filter consisting of a two-stage gyrator section. The filter is used to smooth out the transitions of data which is impressed upon the voice audio. Low-speed data is a 150 bit per second data stream generated by the microcomputer, and used to produce subaudible data on the voice audio.

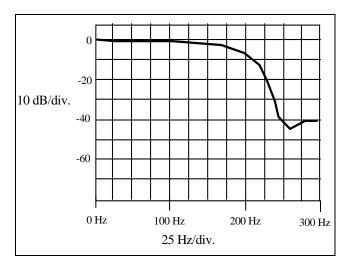

Low-speed data is generated by the microcomputer on Walsh bit 1 and 2 on octal register U38 (pins 2 and 5). For low-speed data, two Walsh bits are scaled and summed through the analog switch (U34C) to the input of the low-speed-data encode filter. The LSD Tx output of the filter leaves the GETC logic board on J19-5, and goes to transmitter where the filtered data is added to the voice audio. The audio (plus low-speed data) combination comes back to the GETC logic board on J7-5, where the analog and digital paths are controlled by the microcomputer through switch U15A. The frequency response of the low-speed-data encode filter is shown in Figure 11.

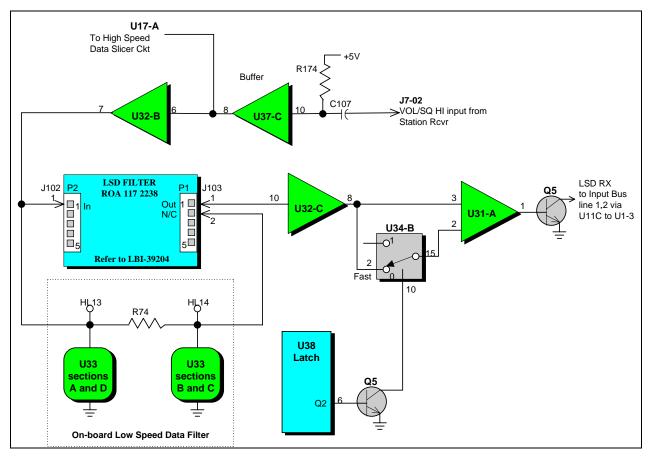

## **Low-Speed Data Decode Filter**

The Low Speed Data Decode Filter is used to remove voice-audio (300-3000 Hz) leaving only the low-speed or subaudible data for input to the microprocessor.

The VOL/SQ HI audio is coupled through capacitor C29 to the low-speed-data-decode voice-reject filter U32B-6 as shown in Figure 12.

The GETC LSD plug-in filter, ROA 117 2238, is used in all GETC receiver applications, except CNI GETCs. The filter is a four-pole elliptic filter with a nominal bandwidth of 50 Hz and a lower frequency peak ripple response of the

Figure 11 - LSD Encode/Decode Filter Response

filter centered at 75 Hz, as shown in the filter response curve in Figure 13. This centering at a nominal 75 Hz is controlled by the filter's on-board clock (9100 Hz).

This improved filter mounts on connectors J102 and J103. Its design allows it to reject the voice audio above 300 Hz and low frequency modulation below 25 Hz. This eliminates the loss of low speed data resulting from low frequency modulation generated by some personal radios when subjected to vibration.

The output from U32B-7 is routed to the filter input at J102-1. The filtered low-speed data is routed to a limiter consisting of U31A and associated circuitry. Analog switch U34B switches the low-speed data acquisition time constant from a higher rate to a slower rate. The output at U31-1 is a data waveform swinging from -12 volts to about 1 volt. This waveform is converted to a TTL waveform by Q5, and sent to buffer U11-7 and then to the microprocessor U1. The microcomputer software decodes the low-speed data.

Figure 10 - Low Speed Data Encode Filter

The plug-in LSD Filter ROA 117 2238 is not used in CNI applications. This GETC application uses the on-board Low Speed Data Filter. In order to use this filter, the plug-in LSD filter must be removed (if installed) and a jumper must be installed on J103-1 & 2.

The on board LSD filter consists of U33, U32B, U32C, and associated circuitry. The filter is a low-frequency response filter, consisting of a two-stage gyrator section. It is used to reject the voice audio and obtain the low-speed data or subaudible signaling. The frequency response of the on-board low-speed-data decode filter is shown in Figure 11.

Figure 13 - LSD Decode Filter Response Using ROA 117 2238 Filter Board

Figure 12 - Low Speed Data Decode Filter

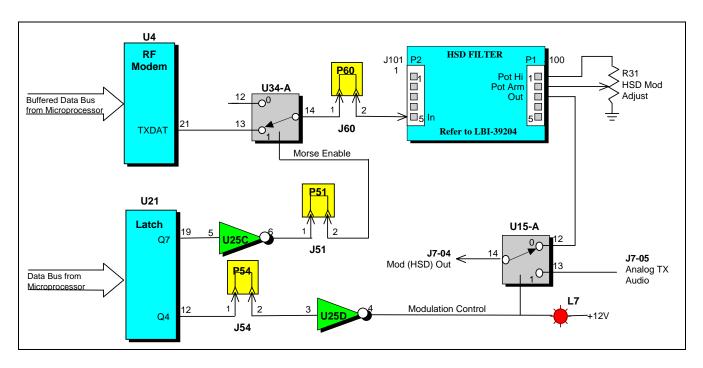

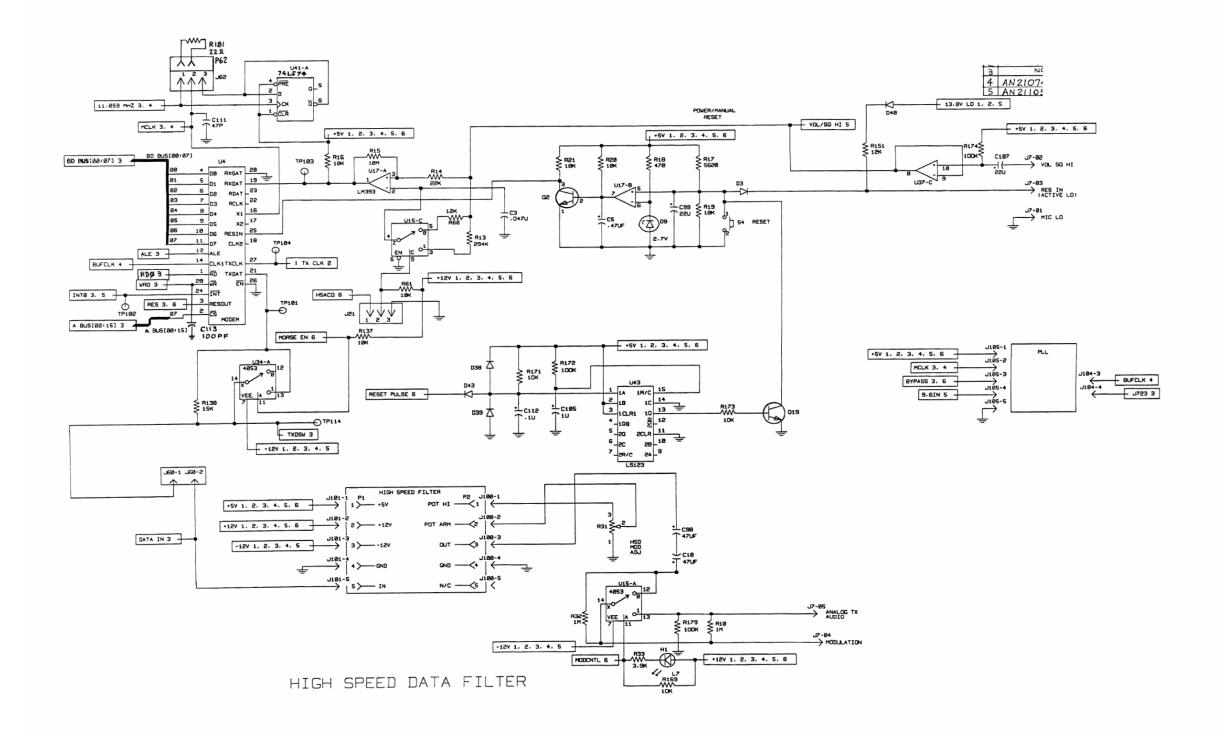

### **High-Speed-Data Transmit Filter**

The High Speed Data (HSD) filter is basically an active GMSK (Gaussian Minimum Shift Keying) filter that filters the data transitions to minimize the high-speed-data transmission bandwidth. The frequency response of the HSD filter section is changed by installing one of the following plug-in filters:

- ROA 117 2237/1 9600 Baud, Wide Band

- ROA 117 2237/2 4800 Baud, Narrowband

- ROA 117 2237/3 ETSI Wide Band

- ROA 117 2237/4 ETSI Narrow Band

- ROA 117 2314/1 9600 Baud, Narrow Band

#### **NOTE**

GETCs with the "MODIFIED FOR EUROPEAN OPERATION" label must use High Speed Filter ROA 117 2237/3 to be ETSI (European Technical Standards Institute) compliant for adjacent channel power requirements. Refer to LBI-39204 for technical details on the High Speed filter boards.

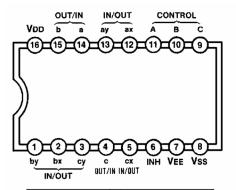

The high-speed-data filter (Figure 14) section consists mainly of a replaceable HSD plug-in filter board and

control circuitry on the GETC Logic Board. The plug-in filters are fully described in LBI-39204.

High-speed data is a 4800 or 9600 bit per second data stream generated by the microcomputer through the RF data modem (U4).

Each of the HSD filter boards has four sections, serving as the transmit filter and buffer/driver. The output of the filter drives high speed data into switch U15A-12. (In MII and MIIe systems, audio from the TX synthesizer-exciter board is fed into J7-5 and routed to U15A-13). The MODCNTL signal, controlled by the microprocessor, switches U15A, enabling or disabling the HSD (or audio) sent to the TX modulator. When the MODCTRL is low, the HSD LED (L7) turns on indicating U15A-12 is selected and high speed data is being routed to the transmitter.

Variable resistor R31 is used to set the high-speed data deviation in the station. This is the only deviation control on the GETC logic board. The voice and low-speed data deviation is set on the synthesizer-exciter board at the station transmitter.

Figure 14 - High Speed Data Transmit Filter

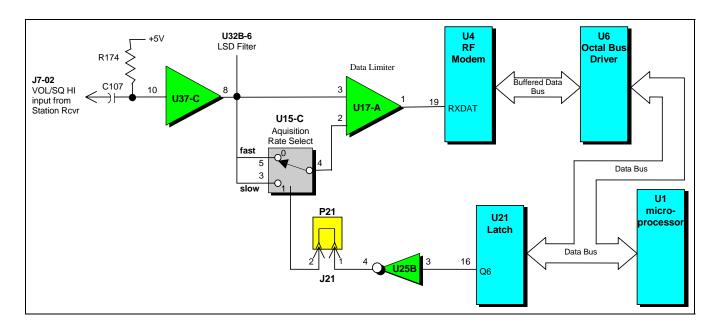

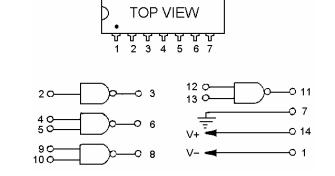

### **High-Speed Data Detector**

The high-speed-data detector is comprised of U17A and associated circuitry. The received input (VOL/SQ HI) enters the GETC logic board at J7-2 and is coupled to U37C-10. This signal is sent to the data limiter (U17A). The microcomputer controls the acquisition rate of the high-speed-data detector through switch U15C. A slow acquisition rate is set when the microcomputer brings U21-16 low, similarly a high on U21-16, sets the fast rate. A low on U21-16 causes a high on U15-9.

Slow acquisition rate is used if the GETC logic board has locked into mobile/portable transmissions. The fast acquisition rate is used if the GETC is looking for mobile/portable transmissions. Speeding up the acquisition rate is achieved by allowing the bias level on U17A to adapt quickly to the DC bias level on the incoming VOL/SQ HI received signal.

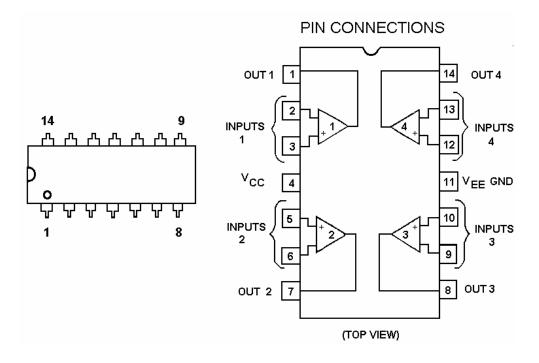

# <u>9600 Baud Modem Board And Telephone Line</u> Interface

The GETC interfaces to the 9600 baud Rockwell Modem Board through connector J3. Address and control of the 9600 baud modem board is over the A bus (lower seven address lines), the BD bus, and Phone Modem U19. The microcomputer addresses the Rockwell Modem Board to set

the modem board timing for external clock, and sends data to the Rockwell Modem Board through U19. When data is to be sent, the microcomputer sends a request to send (RTS) and waits for a clear to send (CTS) from the modem board. The RTS line is sent to the modem board from latch U21-2, and is an active-low TTL signal.

The CTS signal back to the microcomputer is read on U1-15, and is an active-low signal from the modem board. The telephone line transformers T1 and T2, couple the four-wire telephone line to the Rockwell Modem Board.

Transformer T1 receives data from the telephone line and couples the data to the modem board at J3A-32. A voltage follower (U18A) drives the data to the modem board. Resistor R1 is used to adjust the telephone line level to the proper modem reference level. The reference level is 0.16 volts rms. at U18-1. Diodes D10 and D11 are used for surge protection.

Transformer T2 transmits data from the modem board to the telephone line. The serial transmit data is obtained from J3C-32, and sent to U18B for coupling to the telephone line. Resistor R2 is used to adjust the telephone line level to the proper transmit reference level. The reference level is usually 0.77 volts rms. (0 dBm) across J6-8 and J6-9 (balanced). Diodes D12 and D13 are used for surge protection.

Figure 15 - High Speed Data Detector

Figure 16 - Rockwell Modem and Telephone Interface

### **INTERFACE**

#### STATION CONTROL INTERFACE

The following lines are available to the GETC for interface to a trunked station:

| J6-1  | DELAY PTT            | Keys the station transmitter.                                                                                 |

|-------|----------------------|---------------------------------------------------------------------------------------------------------------|

| J6-10 | DET DIS              | Routes HSD and enables or disables LSD.                                                                       |

| J6-11 | SYNTH DATA           | Synthesizer-exciter data line (MII/IIe only).                                                                 |

| J6-12 | SYNTH CLK            | Synthesizer-exciter clock line (MII/IIe only).                                                                |

| J6-13 | SYNTH LCK DET        | Synthesizer-exciter lock detect indicator (MII/IIe only).                                                     |

| J6-15 | SYNTH LD EN          | Synthesizer-exciter load enable pulse line (MII/IIe only).                                                    |

| J6-5  | 1950 DIS             | For EDACS Voting System to enable or disable the 1950 Hz Tone (squelch tone).                                 |

| J7-13 | PA FAIL              | RF power amplifier failure sensing line.                                                                      |

| J7-15 | RUS OUT              | Mutes or unmutes receiver audio.                                                                              |

| J7-2  | VOL\SQ HI            | Unfiltered receiver audio including 9600 baud High Speed Data (HSD), voice, and 150 bps Low Speed Data (HSD). |

| J7-4  | MOD OUT<br>(EXT HSD) | Filtered HSD or Digital Voice to be transmitted.                                                              |

| J19-5 | CG HI (EXT LSD)      | Low Speed Data to be transmitted along with voice.                                                            |

#### **Synthesizer-Exciter Board Interface**

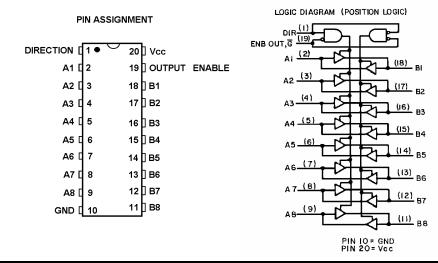

The GETC logic board loads the transmit (800 MHz applications) and transmit/receive (900 MHz applications) frequency information into the station synthesizer(s) (MII/IIe only). The SYNTH DATA (J6-11), SYNTH CLK (J6-12), SYNTH LD EN (J6-15), and SYNTH LCK DET (J6-13) signals are used. The microcomputer loads the

frequency code into the synthesizer-exciter board at powerup, reset, or whenever an out-of-lock indication is obtained from the synthesizer-exciter board. The frequency code is generated by the microcomputer based upon the settings of the DIP switches or Personality Programming on the GETC logic board.

A 32-bit pattern consisting of a reference number (R), the synthesizer divide-by-N counter value (N), the synthesizer divide-by-A counter value (A), and a control bit, make up the frequency code. A single 32-bit load is made to the transmit synthesizer in 800 MHz applications. For 900 MHz applications, a 64-bit load is made (32 bits for transmit and 32 bits for receive).

The sequence of entering data into the synthesizer-exciter board is shown below. This sequence is repeated once for the transmitter and once for the receiver in 900 MHz applications.

| MSB       |           |          | LSB     |

|-----------|-----------|----------|---------|

| R VALUE   | N VALUE   | A VALUE  | CONTROL |

| (14 BITS) | (10 BITS) | (7 BITS) | (1 BIT) |

#### Data Load To Synthesizer-Exciter

The clock, data, and load enable lines (for MII and MIIe only) are initialized to logic 0 at octal register U20. The data is presented on U20-16 (bit 6). After about 40 microseconds, the data is then changed to reflect the next data bit of the synthesizer load. After 32/64 bits have been clocked into the synthesizer-exciter, the load enable line changes states for a 20 millisecond period, and then returns to its previous state. Lock detect is checked at U13-2. If lock is not achieved, then the GETC attempts to reload the synthesizer-exciter board until a lock-detect is established.

The data, clock, and load enable lines are inverted as they leave the GETC and become SYNTH DATA (J6-11), SYNTH CLK (J6-12), and SYNTH LD EN (J6-15). The open-collector drivers on the GETC (U23A-2, U23B-4, and U23F-12) drive the SYNTH DATA, SYNTH CLOCK, and SYNTH LD EN lines to the synthesizer-exciter board over a bus which includes a pull-up to 7.6 volts. The SYNTH LCK DET (J6-13) line is a high (low for 900 MHz) for a positive lock-detect indication. This signal arrives at U13-3 which inverts the logic level so that the microcomputer detects a lock-detect indication by a logic 0 (1 for 900 MHz) on U13-2.

### **Station Control Interface**

The microcomputer on the GETC logic board controls a MASTR II, IIe, or III station operation using the following control and interface lines:

The **SYNTH DATA**, **SYNTH CLK**, **SYNTH LD EN** and **SYNTH LCK DET** lines enable the microcomputer to load the frequency code to the synthesizer-exciter board (MII or IIe only).

The **DELAY PTT** line (J6-1) enables the microcomputer to turn on the station transmitter by pulling J6-1 low (logic high on U20-19). The station transmitter is turned on to 90% of full power in less than 10 milliseconds.

The RUS OUT line (J7-15) disables the voice audio from the transmitter (0 volts on J7-15 or logic high on U21-6). The line is grounded when High Speed Data is being transmitted, no "on channel" carrier is being received, or in the absence of received Low Speed Data. This stops the receiver from routing audio (vol/sq) to the transmitter and the Line output (using RUS\_MUTE and STOP RUS\_PTT). This signal is gated directly back to the station from Sys RUS Out but the GETC can control it. In MASTR II (IIe) systems, the MODULATION line is the direct FM signal from the GETC to the synthesizer-exciter board.

The VOL/SQ HI input line (J7-2) carries unfiltered receiver audio. This includes 9600 BAUD data, Voice and Low Speed Data. Once in the GETC, this signal is routed to the RF Data Modem U4 where it detects High Speed Data and to the Low Speed Data Decode Filter where it separates the audio from the Low Speed data. The High speed data received can be control signaling or digital voice (encrypted or not). Low speed data indicates valid channel activity.

The **LSD TX** line (J19-5) routes the Low Speed Data to the transmitter for transmission along with voice (from the receiver or the Line input). Low speed data goes into the station and through the channel guard pot and to the transmitter. The Low speed data from the GETC is transmitted to accompany voice as an indicator of valid channel activity or to pass on priority scan information.

The **PA FAIL** line (J7-13) is normally high when the RF transmitter is keyed. Low power output or too much reflected power will cause the line to go low. The line is always low when the transmitter is off.

The **RUS IN** line (J7-14) is set high (+5 Vdc) when the receiver unsquelched by an "on channel" carrier. It is reporting carrier activity. It is low when the receiver is squelched.

The **REP**EAT **PTT** (J7-7) line is high (+5 Vdc) when the MASTR III Receiver Synthesizer is locked. When the Receiver Synthesizer is unlocked for 200 mS, the station grounds this line indicating a fault status to the GETC.

The **1950 DISABLE OUT (RPT INHIBIT)** line (J6-5) is only used in an EDACS voting system. In a voting system, when this line is high (+5 Vdc) it mutes the 1950 Hz tone (squelch tone) which is on the Line output in the absence of a clear voice, working channel call. The 1950 Hz tone will however, remain active during digital voice calls such as AEGIS or Voice Guard.

The **REM PTT** line (J7-9) is grounded when the station decodes a 2175 Hz Secur-it tone on the Line input. This signal alerts the GETC to the presence of a call from a remote source (CEC/IMC) for the duration of the 2175 hold tone

The **DELAY PTT** line (J6-1) is pulled low when the GETC wants to key the station for any reason

The **REM PTT** line (J6-16) is connected to the same line as the System Module's REM PTT switch. When the GETC grounds this line, the station executes a Rem PTT which is a higher priority than the Delayed PTT (EXT PTT). This will route audio from the Line input and will key the station if it is not already transmitting.

The **DETECT DISABLE** line (J6-10) is connected to the Modulation Control line (U25D-9) for MIII EDACS. This line is high (+5 Vdc) when High Speed Data is being routed to the transmitter (see EXT HSD) and Low Speed Data is disabled. When this line is high, the transmitter EXT HSD is set forcing the System Module to use High Speed Data regardless of the state of the EDACS system. When this line is grounded, High Speed Data is not routed and Low Speed Data is enabled.

The **EXT HSD** (J7-4) is the High Speed Data sent to the transmitter. A low MODCNTL signal (U25D-8) switches U15A (pin 12 to 14) routing filtered High Speed Data. This audio is not filtered at all in the MASTR III. The High Speed Data can be high speed control signaling or digital voice (encrypted or not).

#### SITE CONTROLLER INTERFACE

The GETC uses the following lines to communicate with the Site Controller:

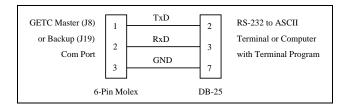

| SITE CNTRL RX 1<br>(J8-1)  | RS-232C transmit data sent to the Master Site Controller. |

|----------------------------|-----------------------------------------------------------|

| SITE CNTRL TX 1<br>(J8-2)  | RS-232C receive data from the Master Site Controller.     |

| SITE CNTRL RX 2<br>(J19-1) | RS-232C transmit data sent to the backup site controller. |

| SITE CNTRL TX 2<br>(J19-2) | RS-232C receive data from the backup site controller.     |

The GETC communicates with the Site Controller (both the master and the backup Site Controllers) through the RS-232C communication ports J8 and J19. This data link is referred to as the Master Serial Link (MSL).

The characteristics of the MSL are as follows:

| Type      | RS-232C       |

|-----------|---------------|

| Baud rate | 19.2 kilobauc |

| Start bit | 1             |

| Stop bit  | 1             |

| Data bits | 8             |

| Parity    | None          |

| Data Type | Binary        |

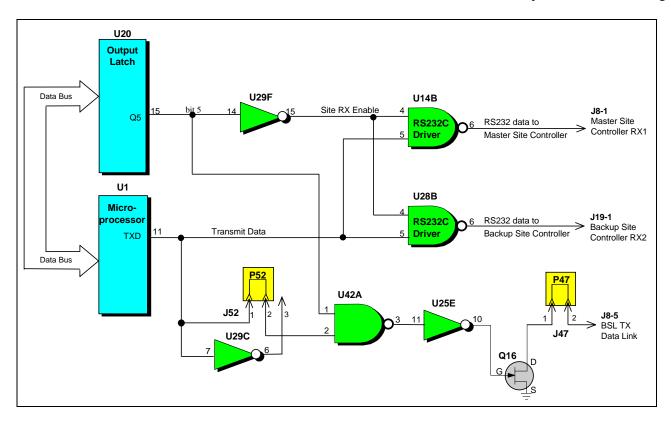

## **Transmit Data**

The GETC communicates to the master and backup Site Controllers through U14B, U27C, U28B and U27D. When the GETC is in the transmit data mode, the serial transmit data (TXD) from the microcomputer (U1-11) is sent to the RS-232C drivers (U14B and U28B) as shown in Figure 17. When gates U14B and U28B are enabled via U20 and U29F, the TX data output (U14B-6 and U28B-6) is routed to the Master Site Controller through J8-1. The TX data is also routed to the Backup Site Controller through

Figure 17 - GETC Data Sent To Site Controller

J19-1.

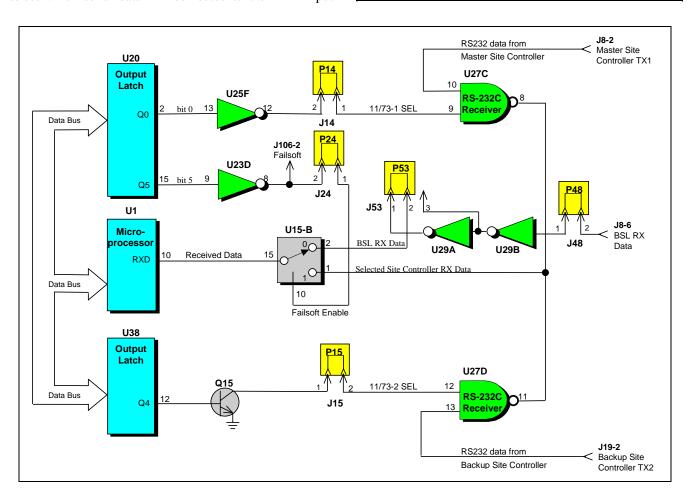

### **Receive Data**

The serial receive data from the Master Site Controller, enters the logic board at J8-2 (*Figure 18*) and goes to the RS-232C receiver (U27C-10). The serial receive data from the Backup Site Controller, enters the logic board at J19-2 and goes to the RS-232C receiver (U27D-13). The output of either Master Site Controller receiver (U27C-8) or the Backup Site Controller receiver (U27-11)is selected by the selection signal sent to the receivers. The output from the selected receiver is sent to the analog switch (U15B-1).

When the analog switch (U15B) is in fully trunked mode, the received Site Controller data output from the analog switch (U15B-15) is sent to the microprocessor receive data (RXD) input (U1-10). When the system is in Failsoft, BSL Rx Data is routed to RXD.

The decoding scheme used by the microcomputer to select which serial data will be routed to the RXD input

A high on U20-2 will turn on the open-collector driver (U25-12) and pull the control line (U27-9) low, disabling the output line (U27-8). A low on U20-2 enables the output at U27C. A logic high on U38-12 will turn on the open-collector transistor (Q15), and pull the control line (U27-12) low, disabling output line U27-11. A low on U38-12 enables the output of U27D.

**Table 3 - Decoding Scheme**

| LOGIC LEVEL        |                     | SIGNAL                  |             |                           |

|--------------------|---------------------|-------------------------|-------------|---------------------------|

| U20-2<br>(11/73-1) | U38-12<br>(11/73-2) | U20-15<br>(FAILSOFT EN) | TO<br>U15-5 | PATH<br>SELECTED          |

| О                  | 1                   | 0                       | U27C-8      | Master Site<br>Controller |

| 1                  | 0                   | 0                       | U27D-11     | Backup Site<br>Controller |

| X                  | X                   | 1                       | U29A-2      | Backup Serial<br>Link     |

Figure 18 - Site Controller or BSL Data Sent To GETC

(U1-10) is given in Table 3.

#### **FAILSOFT INTERFACE**

The GETC uses the following lines to communicate with a SIM or other GETC's during Failsoft operation:

BACKUP TX LINK Backup serial link, transmit output.

(J8-5)

BACKUP RX LINK Backup serial link, received input.

(J8-6)

Frame Sync Link Provides working channel-to-control

(J19-6) channel data synchronization in

trunked stations.

The characteristics of the communication link are given below:

Level 0 to 13.8 volts (nominal)

Mark/Space 13.8 volts (mark)/0 volts (space)

Baud rate 19.2 kilobaud

Start bit 1

Stop bit 1

Data bits 8/9

Parity None

Data type Binary

## **BSL Receive Link**

Receive data on the BSL RX link enters the GETC at J8-6 as shown in Figure 18. The data is buffered and inverted (if required) by U29-A and B and routed to the analog switch U15 pin 2.

When it is necessary for the GETC microcomputer U1 to enable the Failsoft mode of operation, the output at U20-15 is set high. The open-collector driver (U23D) inverts the signal and applies it to the analog switch U15B-10. This action selects the Backup Serial Link (BSL) RX link from J8-6 and routes the BSL RX data to the RXD input at U1.

The low output from U23D is also routed to J106-2. This Failsoft signal may be used by other GETC circuits to enable Failsoft operation.

## **BSL Transmit Link**

When the GETC is transmitting TX data in the Failsoft mode, the transmit data from U1-11 (TXD) is routed to U42A-2, as shown in Figure 17. This data may be inverted,

if required, by U29C. The output from U42A is enabled when the microcomputer directs U20-15 to go low. The output is buffered by U25E and sent to the output FET Q16.

The FET is used to control the rise and fall time of signals applied to the BSL. This reduces crosstalk on the clock and data lines in the cable bundles. Resistor R148 and capacitor C110 control the fall time and R62 and C110 control the rise time of the FET drive. The FET inverts these edges

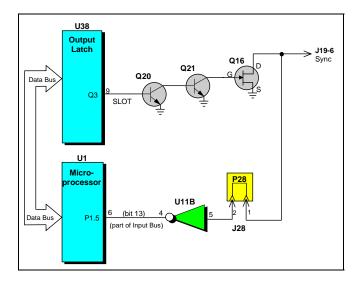

## **Frame Sync Line**

The Frame Sync Line (FSL) is a +13.5 Vdc Bus, with periodic negative pulses (to 0 Vdc), originated by the Control Channel GETC and used by the Working Channel GETCs to synchronize messages to radios.

When the GETC operates as the Control Channel GETC (Figure 19), the microcomputer directs the Output latch U38 to emit sync pulses from U38-9. These pulses are sent to Q20 and Q21 which buffer the signals for input to FET O7.

The FET controls the rise and fall time of the pulses to reduce crosstalk on the clock and data lines in the cable bundles. Resistors R176, R177 and capacitor C109 control the rise and fall time of the FET drive. The SLOT signal interfaces with the other GETCs via J19-6, Sync line.

Working Channel GETCs receive the synchronizing pulses at J19-6 and route the signals to U11B. U11B is the interface to the Input bus (bit 13). The pulses are routed to the microcomputer U1 at pin 4, where they are processed.

Figure 19 - Frame Sync Line Circuit

## PERSONALITY PROGRAMMING

A *personality* is simply a computer file generated (created) by the user. The computer file (or personality) is downloaded into the GETC and contains data that will direct certain operating characteristics of the GETC unit. This allows each GETC to be programmed as required to meet the criteria of the application. The GETC's Personality includes system configuration information such as channel frequencies, call parameters, operating modes, and identification information.

The Personality Programming process stores data in a non-volatile region of memory. The Non-Turbo GETC's non-volatile memory consists of an EEPROM installed in the XU35 socket. For applications using the Turbo Board, Personality data is stored in the Turbo Board's battery backed memory and U35 is removed.

The Personality Programming process involves using the TQ-3357 GETC Shelf PC Programmer which creates the desired personality and transfers the Personality data to the battery backed-up RAM located on the Turbo Board.

#### **NOTES**

- If installing GETC software 349A9607G4 (or later), you must use PC Programmer V4.03 (or later). Version 4.03 (or later) allows you to download Field Macros containing the new features' personality parameters.

- 2. When using 349A9607G5 software, the Field Macro "gtc\_9505.mac" must be installed. When using 349A9607G6 software, the Field Macro "gtc\_9506.mac" must be installed.

- 3. It is not necessary to recreate the personality when upgrading from Group 1 or Group 2 software to Group 4. However, to activate new features, read the existing personality and edit the personality as required.

TQ-3357 V4.03 (or later) also allows you to upload the GETC's Personality without changing the DIP switch settings.

When using PC Programmer TQ-3357 V3 (or earlier) and downloading 344A4414G3 (and earlier) software, the data from the PC files is routed to the Turbo Board microprocessors through Turbo Board programming connector J100 at the rear of the GETC Shelf.

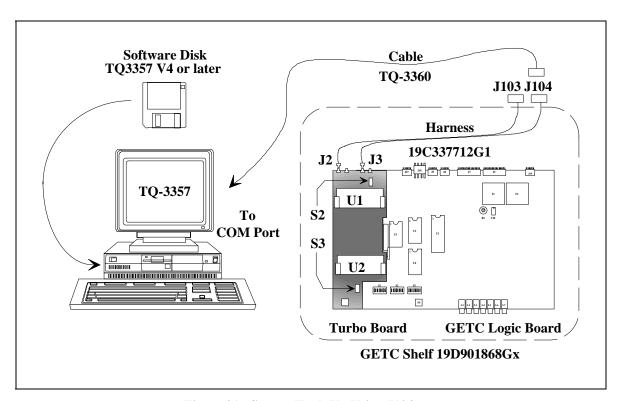

When using PC Programmer TQ-3357 V4.03 (or later), the Turbo software is downloaded to the Turbo Board microprocessors through Turbo Board programming connector J104. Programming through J104 also allows you to load the GETC personality without changing setups. In addition, the V4.03 PC Programmer will diagnose any problems between the PC and the GETC during the downloading process and simplify the handling and archiving of the Turbo software.

## **Equipment Required**

- IBM PC/XT/AT or compatible with Turbo software loaded in the LOAD1e directory.

- TQ-3360 programming cable.

- Male DB-25 to female DB-9 adapter or cable if the PC's serial port connector is a male DB-9 connector instead of a male DB-25 connector.

# <u>Programming a Personality Using TQ-3357 V3</u> (or earlier)

When using TQ-3357 Version 3 (or earlier) you must program the personality through J100.

- 1. Connect one end of the serial programming cable (TQ-3360) to the computer. Connect the other end of the serial cable to the GETC Shelf connector J100, see Figure 20.

- 2. Set the GETC DIP switches S1, S2, and S3 for the programming mode as shown in Figure 7. Set S2-8, S3-3 and S3-6 to OPEN. All other S3 positions should be CLOSED. Switches S1-1 thru S2-7 can be in any position and need not be changed. DIP switches S1-S3 are located near the front of the GETC Shelf, (see Figure 23).

- 3. Reset the GETC by either applying power or pressing the GETC RESET switch S4, located just below the DIP switches. Resetting the GETC, in combination with the DIP switch settings, places the GETC into the Personality Programming mode.

- 4. Verify that front panel LEDs L3, L4, and L5 are ON, as shown in Table 4. This indicates the GETC is ready for programming.

**Table 4 - Indicators in Programming Mode Using J100**

| LED INDICATORS                                                                                   | L1 | L2 | L3 | L4 | L5 | L6 | L7 |

|--------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|

| Programming Mode                                                                                 | 0  | O  | •  | •  | •  | 0  | O  |

| Legend: $\mathbf{O} = \mathbf{OFF}  \mathbf{\Phi} = \mathbf{ON}  \mathbf{*} = \mathbf{FLASHING}$ |    |    |    |    |    |    |    |

Run the load1e.exe program. Follow the on screen instructions and program the Turbo Board. Additional programming instructions may be found in SRN1062 and LBI-38822.

#### **NOTE**

When using Turbo Board 344A4414 Group 2 (or later) software, re-programming the GETC Turbo Board will not alter previously stored Personality Data. When Personality Data is present, "loadle.exe" clears and performs CRC functions over the code portion of memory only.

- 6. Proceed with the Personality programming as described in TQ-3357.

- 7. After saving the personality and downloading it into the GETC, perform an operational checkout of the GETC.

Figure 20 - System Hook-Up Using J100

# Programming a Personality Using TQ-3357 Version 4.03 (or later)

When using TQ-3357 Version 4.03 (or later), you must program the personality through J104.

- Connect one end of the serial programming cable (TQ-3360) to the computer. Connect the other end of the cable to the GETC Shelf connector J104. See Figure 21.

- 2. Move Switch S2 on the <u>Turbo Board</u> to the front placing the Turbo into the programming mode.

- 3. Verify that front panel LEDs L6 and L7 are flashing, as shown in Table 5. This indicates the GETC is ready for programming.

**Table 5 - Indicators in Programming Mode Using J104**

| LED INDICATORS                                | L1 | L2 | L3 | L4 | L5 | L6 | L7 |

|-----------------------------------------------|----|----|----|----|----|----|----|

| Programming Mode                              | 0  | О  | О  | 0  | 0  | 米  | *  |

| Legend: $O = OFF  \bullet = ON  * = FLASHING$ |    |    |    |    |    |    |    |

- 4. Proceed with the Personality programming as described in TQ-3357.

- 5. After saving the personality and downloading it into the GETC, perform an operational checkout of the GETC.

Figure 21 - System Hook-Up Using J104

# **MAINTENANCE**

The Maintenance Section provides procedures for maintaining the GETC and for the removal and reinstallation of defective subassemblies.

# SUBASSEMBLY REMOVAL AND REPLACEMENT

The following procedures provide step-by-step instructions for the removal and reinstallation of GETC subassemblies.

## WARNING

Before attempting to remove any subassembly, disconnect all power from the GETC.

## **CAUTION**

Observe precautions for handling

# ELECTROSTATIC SENSITIVE DEVICES

## **NOTE**

GETCs with the "MODIFIED FOR EUROPEAN OPERATION" label must use High Speed Filter ROA 117 2237/3 to be ETSI (European Technical Standards Institute) compliant for adjacent channel power requirements. Refer to LBI-39204 for technical details on the High Speed filter boards.

# Replacing a 19D904266 or 19D902104 Logic Board

This procedure details the steps for replacing the 19D904266G1, 19D904266G4, 19D902104G1 Logic Board with the new GETC logic Board 188D6500G1 or G4.

## **NOTE**

Ensure a 188D6500G4 board is used whenever a Speedy microprocessor is required.

#### **Remove:**

- 1. Remove power from the GETC. If this unit is part of an EDACS site, only turn power off to one channel at a time.

- 2. Disconnect the cables from the Logic Board connectors J19, J6, J7, J8, J9, J10, and J27.

- 3. Remove the PROM from the XU2 socket.

- 4. Remove the Turbo Board if installed.

- 5. Remove the Rockwell Modem if installed.

- 6. Disconnect the cable from J49 if installed.

- 7. Remove the optional Guardog cable 19B803258P1, if installed.

- 8. Remove the 11 pan head screws securing the Logic Board to the GETC shelf plus two screws connecting the lightning ground.

- The Logic Board may now be removed from the shelf.

#### **Install:**

- 1. Mount the Logic Board in the GETC shelf as shown in Assembly Diagram 19D901868G3.

- 2. Install the 188D6500G1 or G4 Logic Board and secure the board and Lightning Protection cables to the shelf using the 13 mounting screws.

- 3. Reconnect the cable to J49 if applicable.

- 4. Reconnect the cables to the Logic Board connectors J19, J6, J7, J8, J9, J10, and J27.

- 5. Install the Rockwell Modem if removed.

- 6. Install the Turbo Board if removed.

- 7. Install the PROM removed from the old board into socket XU2.

- 8. Install Guardog cable RPM 113 2515, if the Guardog option is required, and plug harness connector into J106. Ensure jumpers J16 and J24 are removed.

- 9. If the GETC is for use in a MASTR II station, remove the wire from J6-10 in the station harness and insulate it.

- 10. If the GETC is for use with a MASTR III station, remove the jumper from J26.

- 11. Ensure Low Speed and High Speed filters are properly installed (refer to LBI-39204 for additional filter board information).

- Set DIP switches exactly like the old board being replaced.

- 13. Apply power and perform the required alignment and checkout procedures.

### Replacing a 188D6500Gx Logic Board

This procedure details the steps for removing and reinstalling the GETC Logic Board 188D6500Gx in a 19D901868G5 or G6 GETC shelf.

#### Remove:

- 1. Remove power from the GETC. If this unit is part of an EDACS site, only turn power off to one channel at a time.

- 2. Disconnect the cables from the Logic Board connectors J19, J6, J7, J8, J9, J10, and J27.

- 3. Remove the PROM from the XU2 socket.

- Remove the Turbo Board if installed.

- 5. Remove the Rockwell Modem if installed.

- Disconnect the cable from J49 and J106 if installed.

- 7. Remove the eleven pan head screws securing the Logic Board to the GETC shelf (11 mounting screws plus two ground leads).

- 8. The Logic Board may now be removed from the shelf.

#### **Install:**

1. Mount the Logic Board in the GETC shelf as shown in Assembly Diagram 19D901868G5.

- 2. Install the 188D6500G1 or G4 Logic Board and secure the board and Lightning Protection cables to the shelf using the eleven mounting screws.

- 3. Reconnect the cable to J49 and J106, if applicable.

- 4. Reconnect the cables to the Logic Board connectors J19, J6, J7, J8, J9, J10, and J27.

- 5. Install the Rockwell Modem if removed.

- 6. Install the Turbo Board if removed.

- Install the PROM removed from the old board into socket XU2.

- 8. Ensure Low Speed and High Speed filters are properly installed (refer to LBI-39204 for additional filter board information).

- Ensure the jumpers installed on the new board match those on the old board.

- 10. Set DIP switches exactly like the old board being replaced.

- 11. Apply power and perform the required alignment and checkout procedures.

#### Turbo Board

This procedure details the steps for removing and installing the Turbo Board. Additional maintenance information regarding the Turbo Board assembly may be found in LBI-38822.

## Remove:

- 1. Remove power from the GETC.

- Disconnect the ribbon cable from the GETC Logic Board XU3 socket.

- 3. Disconnect the Turbo Board harness (19C337712) from the Turbo Board connectors J2 and J3.

- 4. Remove the Turbo Board guard (secured by three flat head screws).

- 5. Remove the three threaded inserts and the two pan head screws securing the board. The board may now be removed from the GETC.

#### **Install:**

Reinstall the Turbo Board using the following procedure. Refer to the Installation Diagram (19D438125) in LBI-38822 for parts identification.

- 1. Align the Turbo Board holes over the threaded spacers (orient the Turbo Board so connectors J2 and J3 are toward the rear of the GETC Shelf).

- 2. Secure the Turbo Board by installing two (2) pan head screws (item #6) and two (2) lock washers (item #7) through the board and into the threaded inserts located near the front of the GETC Shelf (near S1 and Y1).

- 3. Install three threaded inserts (item #3) through the board into the remaining spacers. These will be used to mount the guard.

- 4. Install the guard (item #1) using three (3) flat head screws (item #4).

- 5. Plug the ribbon cable from J1 on the Turbo Board into the XU3 socket on the GETC Logic Board.

- 6. Connect plugs P2 and P3 on the Turbo Board Harness (19C337712G1) to the Turbo Board J2 and J3 connectors, respectively.

- 7. Apply power and reprogram the Turbo Board and GETC Personality as required.

#### **Rockwell Modem**

This procedure details the steps for removing and reinstalling the Rockwell Modem.

#### Remove:

- 1. Remove power from the GETC.

- 2. Remove the Turbo Board if installed.

- 3. Remove the four screws securing the modem. If the GETC has a Turbo Board, remove two threaded inserts and two screws.

- 4. Slide the modem out of Logic Board connector J3 and lift out of GETC.

#### **Install:**

- Insert the Rockwell Modem into J3 on the GETC Logic Board and align the mounting holes over the GETC shelf standoffs.

- Isolate the modem by installing the eight (8) fiber washers (4035306P25). Insert four washers between the board and the GETC shelf mounting standoffs and place four washers on top of the modem board over the mounting holes.

#### **NOTE**

Ensure the modem is insulated from its mounting standoffs using the eight 4035306P25 washers. Four washers mount on top of the modem's printed circuit board and four washers mount on the bottom between the modem's printed circuit board and the GETC shelf standoffs.

- 3. Secure the modem by installing two screws through the washers and modem board into the standoffs located on the end opposite J3.

- 4. On the connector side (J3) of the modem, install the two (2) threaded inserts when also installing the Turbo Board or two screws to complete the modem installation.

- 5. Install the Turbo Board if previously removed.

- 6. Reapply power as required.

#### Power Supply, A2

This procedure details the steps for removing and reinstalling the GETC Power Supply, A2.

#### Remove:

- 1. Remove power from the GETC.

- 2. Unplug the Power Supply cable A2W1P1 from the GETC Logic Board connector A1J27.

- 3. Remove the Power Supply mounting hardware (nut and lockwasher) securing the Power Supply to the shelf (3 places).

- 4. Lift the Power Supply out of the GETC.

#### **Install:**

- 1. Mount the Power Supply in the GETC shelf as shown in Assembly Diagram 19D901868G3.

- 2. Secure the assembly using the three #6 nuts and lock washers.

- 3. Plug the Power Supply Cable A2W1P1 into the GETC Logic Board connector A1J27.

- 4. Reapply power and verify the regulator supplies the proper voltage as detailed in the test and alignment procedures.

#### TEST AND ALIGNMENT

The procedures presented in this section are for bench testing and aligning the GETC. When field testing the GETC, refer to the procedures contained in the GETC Installation and Configuration manual for the specific application.

#### **GETC TESTING**

The test procedures use the SIMON Test program and simulate the operation of a GETC configured for use in an **EDACS Station.**

## **Test Equipment Required**

The equipment necessary for the test is listed below. This is a list of suggested equipment only. Substitutions may be made as necessary. Equivalent test equipment means you may use equipment that performs an equivalent function as required in the test. For example, the frequency counter substituted for a Fluke-1920A need only cover the required frequency range and provide the proper resolution for the test - it does not need to be equivalent to the 1920A in all aspects.

- DC Power Supply with current limiting, HP-6286A (or equivalent), capable of producing 13.8 Vdc @ 2A.

- Digital Multimeter, Data Technology Model 30 (or equivalent) with 20 Vdc range.

- Oscilloscope, Tektronix-465 (or equivalent) medium bandwidth, non-storage.

- Frequency Counter, Fluke-1920A (or equivalent) capable of measuring 12 MHz.

- Function Generator, HP-3312A (or equivalent), capable of producing a 0 to 10 kHz sine wave.

- Distortion Analyzer, HP-334A (or equivalent).

- Triplett Model 630-PL Type 5 (or equivalent) AC Volt-Ohm Meter.

- ASCII Terminal or Personal Computer (PC) with terminal emulation program.

- Interconnecting Cable (PC to GETC) (see Terminal Connection, step 2, for fabrication details).

- SIMON Test PROM, 349A9607G2 (see Software Requirements for details).

- Miscellaneous materials:

- Jumpers 19A702104P2, 2-pin (36 ea. required). Normally supplied as part of 344A3450G9 Hardware Kit.

- Capacitor, coupling, 10 µF.

- Resistor, 100 ohm, 5 watt.

- Resistor, 680 ohm, 1/4 watt.

- Resistor, 10K ohm, 1/4 watt (2 required).

# **Terminal Connection**