# LBI-39107

# MAINTENANCE MANUAL

# T1/E1 INTERFACE CARD 188D5909P1

# TABLE OF CONTENTS

Page

| SPECIFICATIONS                             | 3      |

|--------------------------------------------|--------|

| DESCRIPTION                                | 5      |

| T1/E1 PORT                                 | 5      |

| SUBRATE PORTS                              | 5      |

| OPERATING MODE                             | 5      |

| Analog/Modem Mode                          | 5<br>5 |

| CEC/IMC SYSTEM CLOCKS                      | 5<br>7 |

| A/B Redundant System Clocks                | 7      |

| Network Synchronization Design             | 7      |

|                                            | /      |

| CIRCUIT ANALYSIS                           | 9      |

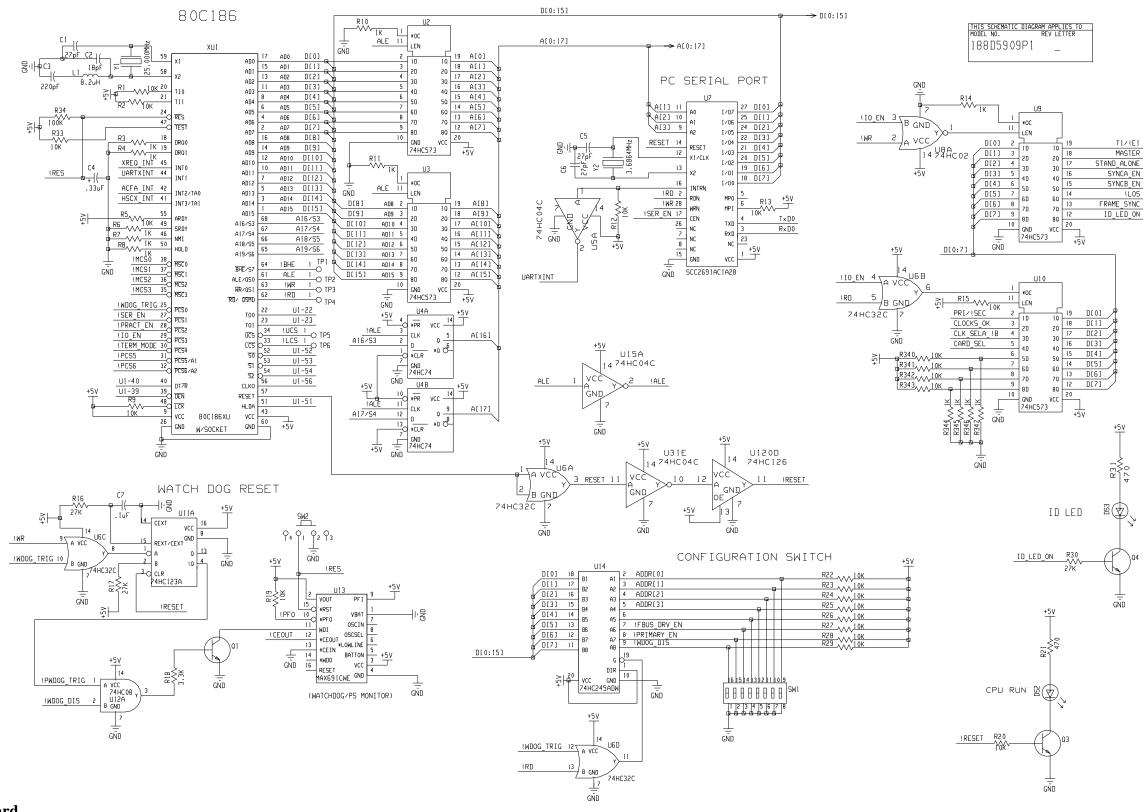

| MICROPROCESSOR CIRCUITS                    | 9      |

| Microprocessor                             | 9      |

| Reset Circuit With Watchdog Timer          | 9      |

| Address Latches                            | 10     |

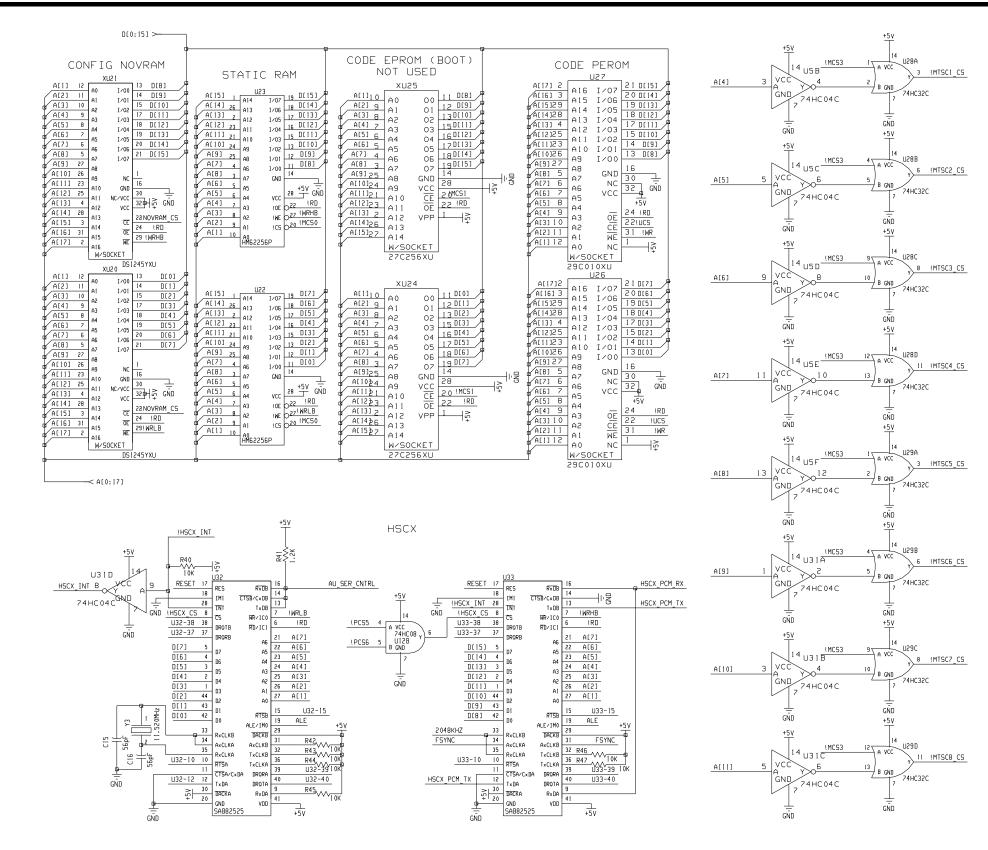

| Memory                                     | 10     |

| PEROM and EPROM                            | 11     |

| NOVRAM and Static RAM                      | 11     |

| PC Diagnostic Serial Port                  | 11     |

| Dual-Channel HSCX Controllers              | 11     |

| U32 Channel B – Controller Board HDLC Link | 12     |

| U33 Channels A & B – Embedded HSCX Links   | 12     |

| Microprocessor Interface                   | 12     |

| Configuration DIP Switch                   | 13     |

| Positions 1 Thru 3                         | 13     |

| Positions 5 Thru 8 – Card Address Setting  | 13     |

| Input/Output Port                          | 14     |

| Status Indicators                          | 14     |

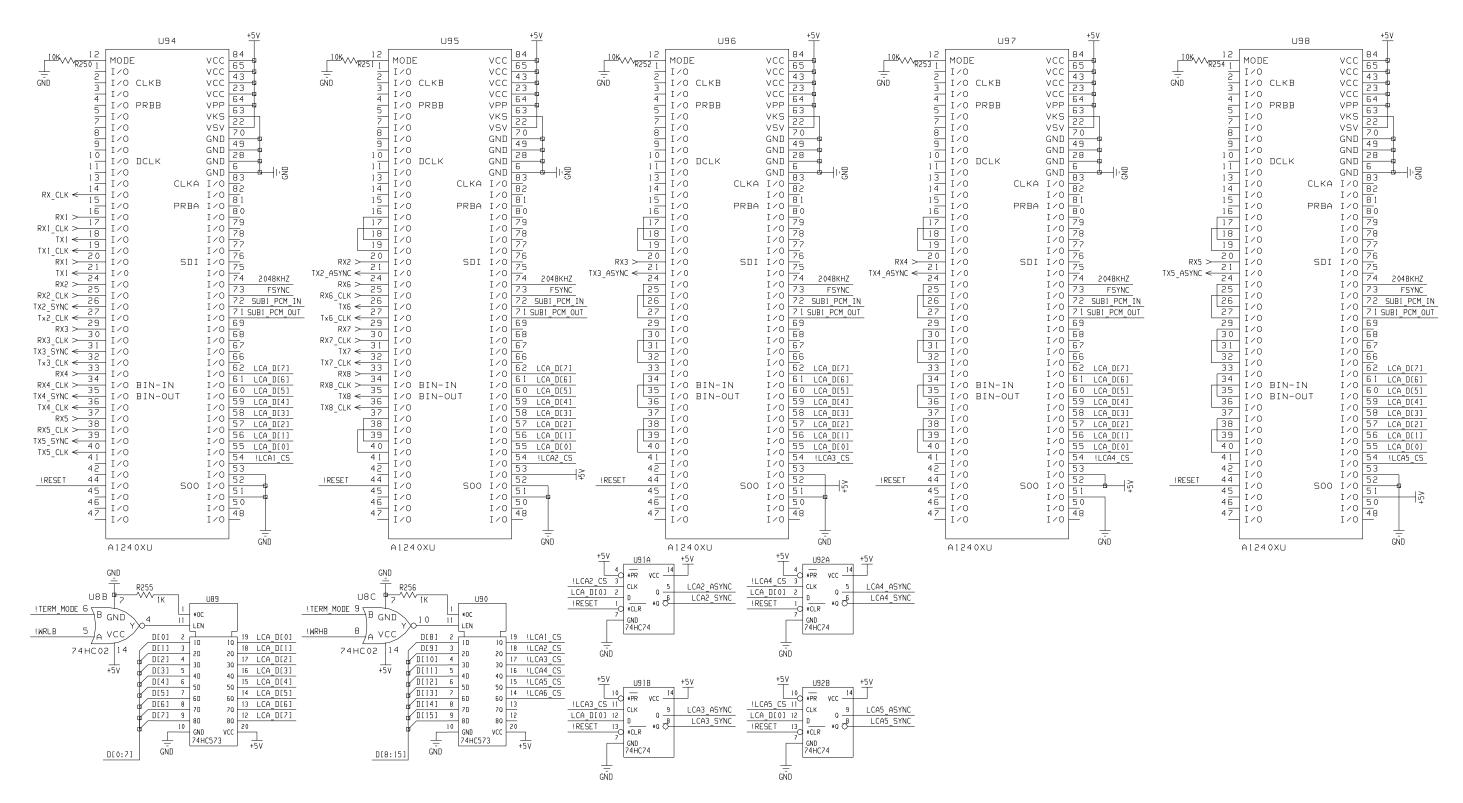

| MEMORY TIME SWITCHES                       | 14     |

| MTSC Connection Examples                   | 19     |

| Microprocessor Interface                   | 19     |

| Clock Inputs                               | 19     |

| FUTUREBUS TRANSCEIVERS                     | 20     |

| TDM Bus Interfacing                        | 20     |

| Clock Inputs                               | 21     |

| Clock Outputs                              | 21     |

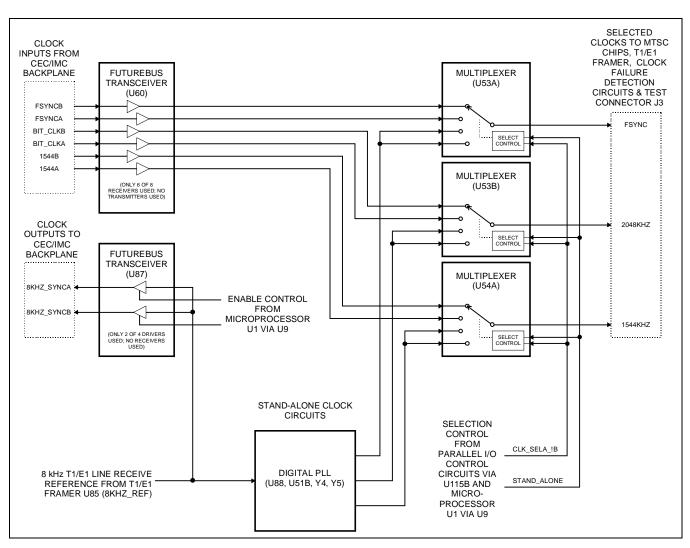

| CLOCK SELECTION AND GENERATION             | 21     |

| System Clock Mode & Selection Circuits     | 21     |

# TABLE OF CONTENTS (Continued)

|                                                         | Page |

|---------------------------------------------------------|------|

| Stand-Alone Clock Mode                                  | 23   |

| Clock Generation                                        | 23   |

| 4 MHz Clock                                             | 24   |

| Clock Failure Detection                                 | 24   |

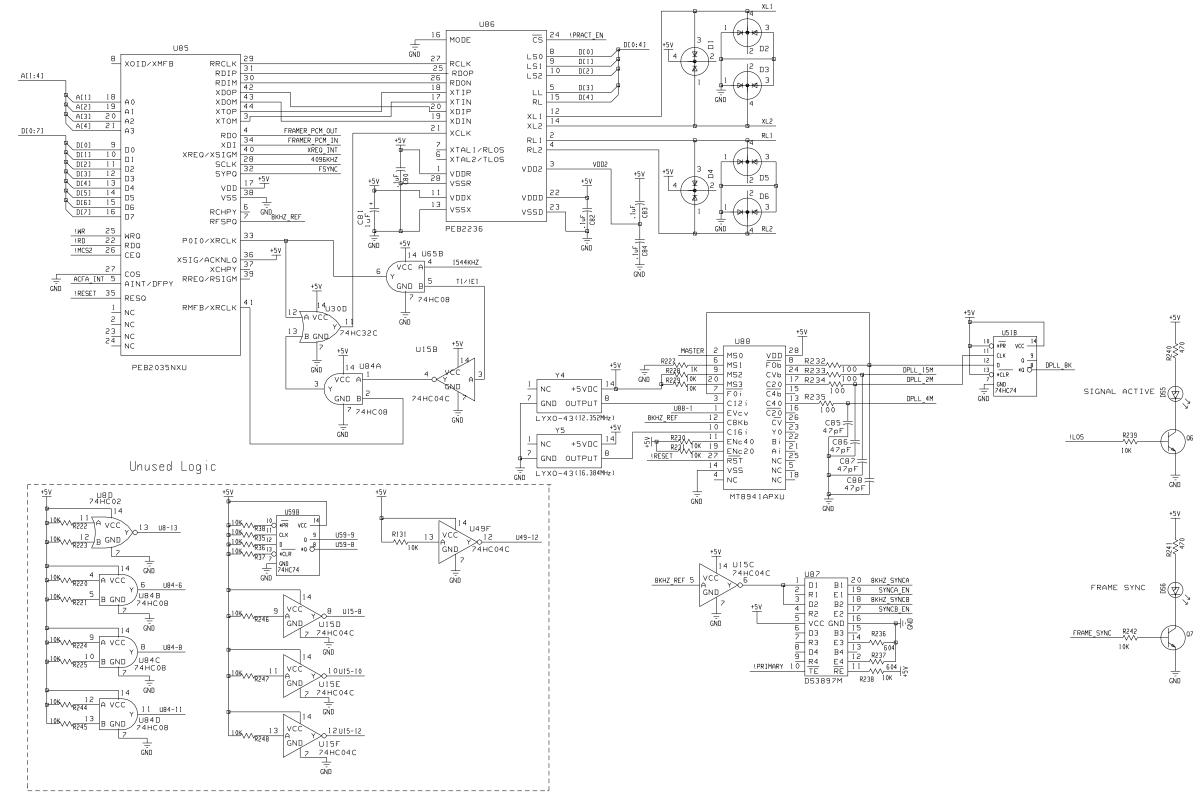

| T1/E1 LINE FRAMER AND LINE INTERFACE                    | 25   |

| Framer U85                                              | 25   |

| Microprocessor Interface                                | 25   |

| MTSC Interface                                          | 25   |

| Reset Logic                                             | 26   |

| Line Interface U86                                      | 26   |

| Framer Connections (U85-to-U86 Interface)               | 26   |

| T1/E1 Line Interface                                    | 26   |

| Microprocessor Interface                                | 26   |

| T1/E1 Mode Clock Switching                              | 27   |

| 8 kHz Reference Clock Output                            | 27   |

| 8 kHz Reference Clock To U88                            | 27   |

| 8 kHz Reference Clock To U87                            | 27   |

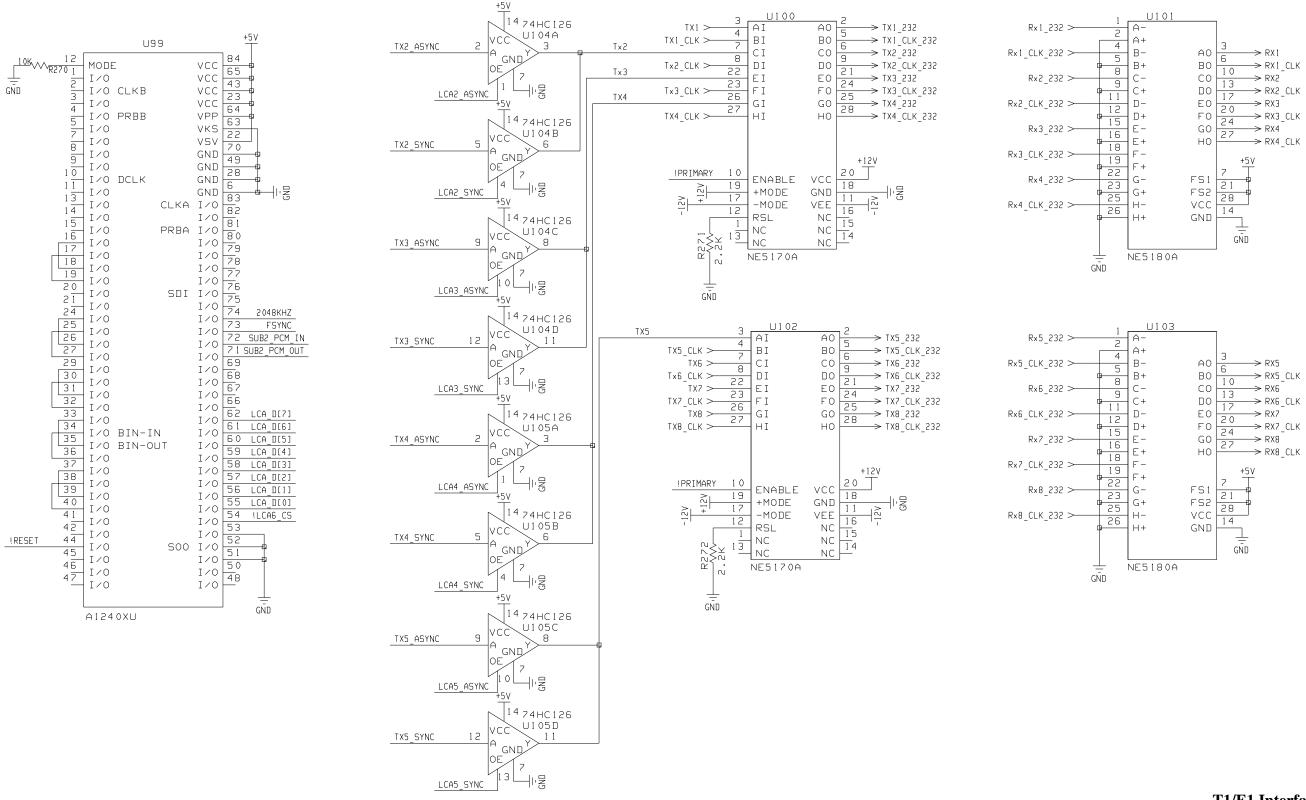

| GATE ARRAYS, SUBRATE PORTS AND RS-232 DRIVERS/RECEIVERS | 28   |

| Subrate Port Interfacing                                | 28   |

| Receive Data And Clock Gate Array Inputs                | 29   |

| Transmit Data And Clock Gate Array Outputs              | 29   |

| Subrate Ports 2 – 5 Sync/Async Transmit Data Selection  | 29   |

| RS-232 Drivers                                          | 30   |

| RS-232 Receivers                                        | 30   |

| Microprocessor Interface                                | 30   |

| On-Card TDM Network                                     | 31   |

| Gate Array Modes                                        | 31   |

| Analog/Modem Mode (Uses Gate Array Mode 1 Only)         | 33   |

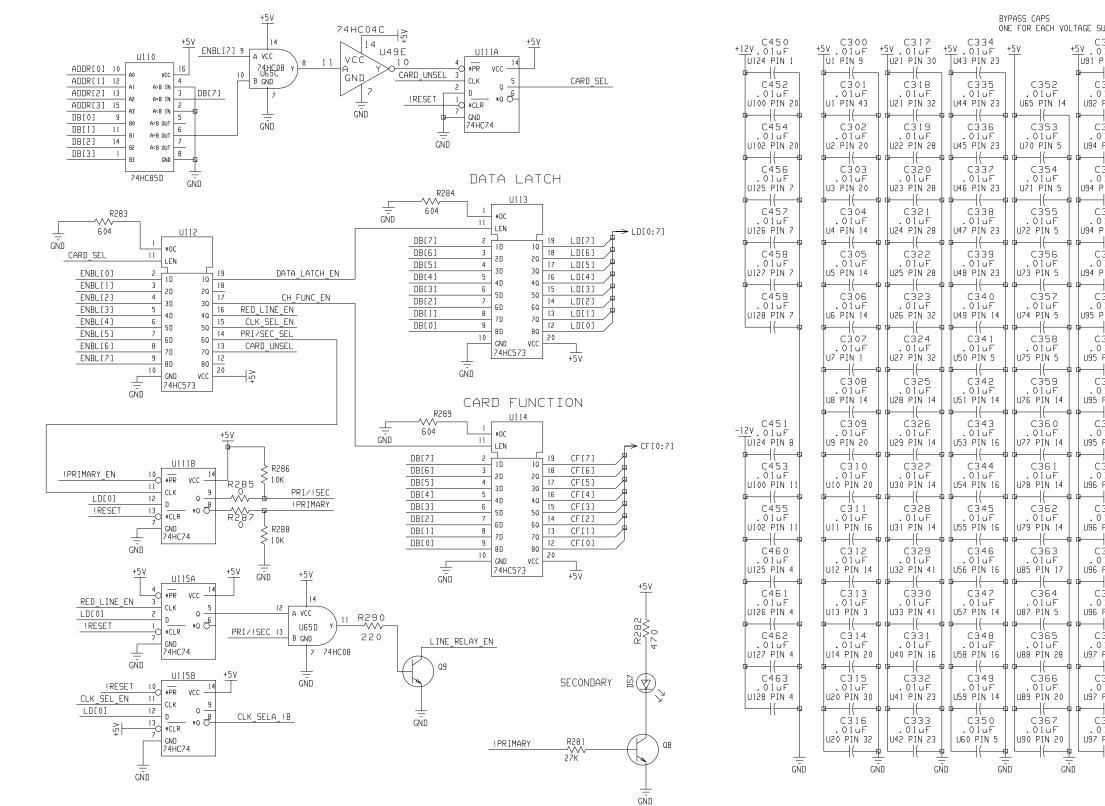

| PARALLEL I/O CONTROL                                    | 33   |

| Primary/Secondary Mode Selection                        | 34   |

| Redundant Line Relay Control                            | 36   |

| System (A/B) Clock Selection                            | 36   |

| Futurebus Drivers Master Enable/Disable Control         | 36   |

| POWER SUPPLY                                            | 37   |

| EXTENDED POWER PINS                                     | 38   |

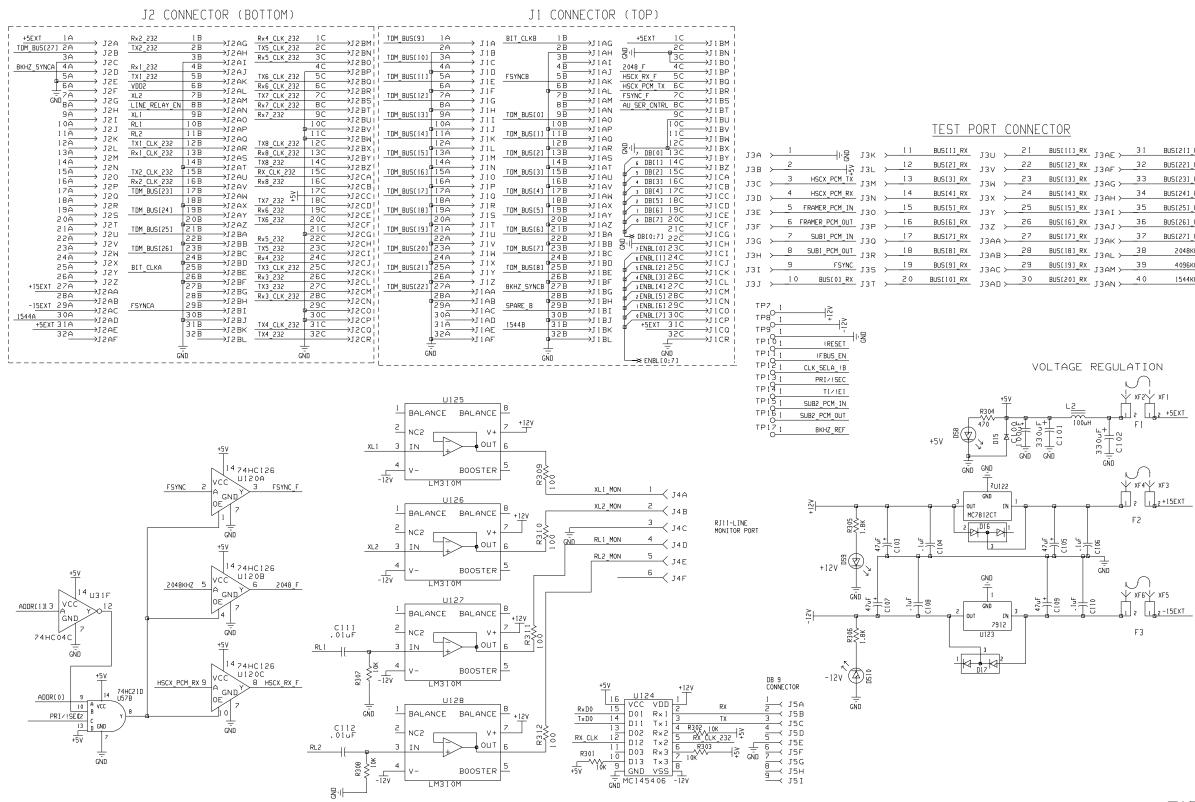

| TEST CONNECTOR                                          | 38   |

| T1/E1 LINE MONITOR PORT                                 | 38   |

| CONFIGURATION                                           | 38   |

| DIP SWITCH SW1                                          |      |

| CEC/IMC MANAGER                                         | 38   |

| PARTS LIST                                              | 39   |

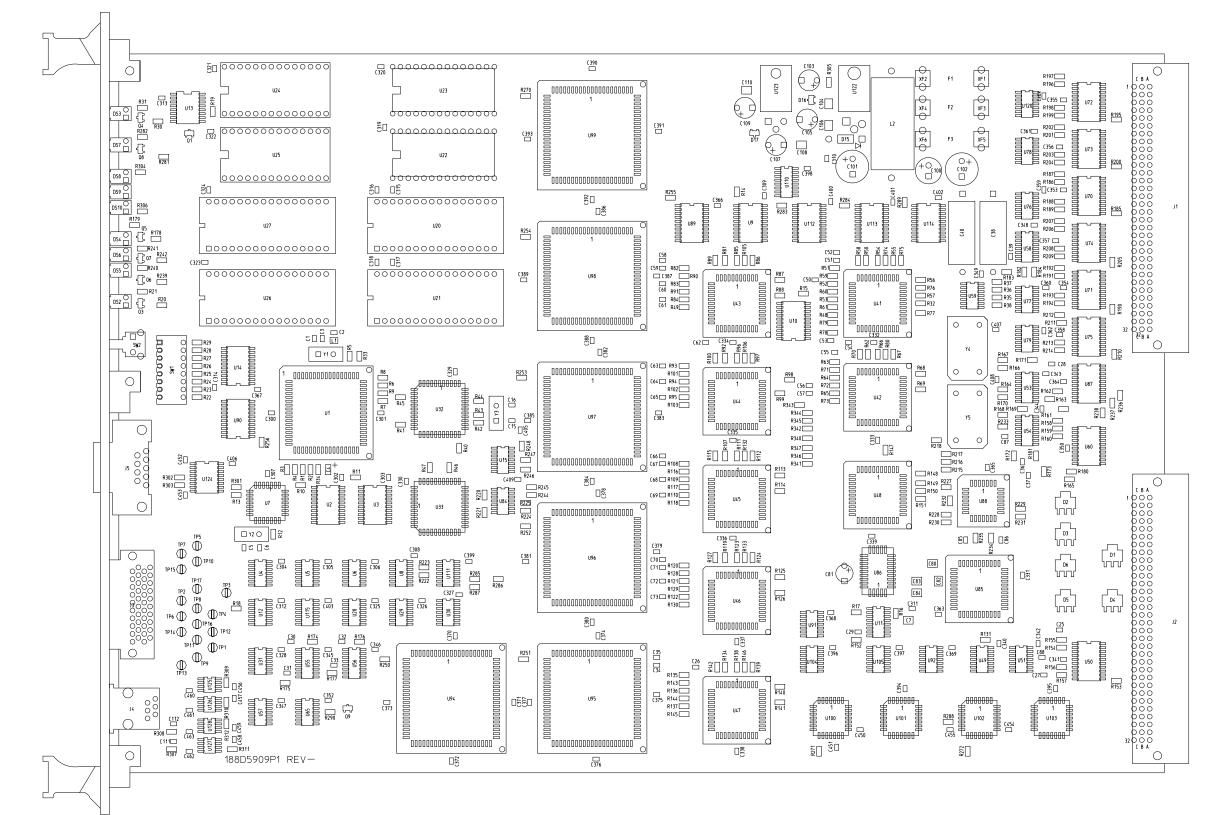

| OUTLINE DIAGRAM                                         | 43   |

| SCHEMATIC DIAGRAM                                       | 44   |

# **SPECIFICATIONS**\*

# FEATURES/CAPABILITY

T1/E1 Line Interface **Total Channels T**1 E1 (CEPT) Frame Formats T1 (1.544 Mbps full-duplex TDM) E1 (CEPT; 2.048 Mbps full-duplex TDM) Line Codes T1 E1 (CEPT) Line/Channel Signaling T1 E1 (CEPT) **T1/E1 Subrate Ports** Total Number Synchronous Ports

Asynchronous Ports

Synchronous/Asynchronous Selection

#### PCM Signal Format on CEC/IMC TDM Network

T1 Applications E1 Applications

Redundancy System Clocks

Diagnostics

Line Interfacing

# T1/E1-to-CEC/IMC Clock Synchronization

External (slave mode) Internal (master mode)

#### **CEC/IMC MANAGER (MOM PC) FUNCTIONS**

#### **User Configurable Parameters**

Subrate Port Configuration Monitoring Functions 24 full-duplex 31 full-duplex

4-Frame Multiframe (F4), 12-Frame Multiframe (F12, D3/4), Extended Superframe (ESF) and Remote Switch Mode (F72) Double-frame and CRC multi-frame

B8ZS and AMI with ZCS HDB3

CAS-BR (Bit Robbing) CAS-CC (channel 16 signalling)

8 available if T1/E1 channels free Industry-standard DS0B subrate multiplexing across T1/E1 link at 9600 baud; Intraplex Inc. proprietary multiplexing method across CEC/IMC TDM network Proprietary signalling across T1/E1 link at rates between 0 and 19,200 baud (inclusive) Auto-configured by CEC/IMC Manager based on card mode, available T1/E1 channels, etc.

µ-Law A-Law

Provided by CEC/IMC Clock Board and on-card clock monitoring and selection circuits

T1/E1 signal active and frame sync acquired status indicators on front panel (See CEC/IMC Manager for detailed stats.)

Direct T1/E1 connection to PBX (Private Branch eXchange) telephone interconnect systems such as EDACS Jessica PBX Gateway equipment; CSU required for telephone company interface

CEC/IMC clocks frequency-locked to received T1/E1signal T1/E1 transmit signals frequency-locked to CEC/IMC clocks; external T1/E1 devices must be slaved to T1/E1 signal from CEC/IMC

CEC/IMC interface module mode, line type, frame format, line code, line length, signaling type, site channels' disbursements, slave clock mode.

Auto-configured per user-configured parameters' settings

T1/E1 signal active status, frame sync acquired status, frame error status, channel appropriations (logical/site channel(s), HSCX or subrate port(s)), subrate port sync/async configuration, detailed alarm and sync status, accumulated statistics

# SPECIFICATIONS

#### REGULATORY

Radio Frequency Interference Line Interface

#### GENERAL

**Card Physical Characteristics**

#### **Operating Temperature**

Power Supply Requirements +5-Volt Supply +15-Volt Supply & -15-Volt Supply

Microprocessor Type Clock Rate Reset Circuit

#### Memory Size (16-bit) ROM

PEROM (flash) EPROM RAM Static Non-volatile

Clock Inputs System Clock Mode

Required Stability for System Clock Inputs On-Card Clock Generation for T1/E1 Support

# Clock Selection High-Speed Serial Link (HDLC) T1/E1 Interface Card-to-Controller Board

Meets FCC Part 15 and EN 55022 for Class A equipment Meets CCITT G.703, G.732 and G.733

Compatible with existing 6-rack unit CEC/IMC boards/cards (VME-like backplane) with two 96-pin DIN connectors  $0-70^{\circ}$  Celsius ( $32^{\circ} - 158^{\circ}$  Fahrenheit)

1100 mA maximum 60 mA maximum each supply

16-bit 80C186 25 MHz Power-up, manual and watch-dog reset circuits included

128K (socketed) 32K (socketed; not installed)

32K 128K (socketed)

Receives A/B 8 kHz frame sync clocks, A/B 2.048 MHz bit clocks and A/B 1.544 MHz T1 clocks generated by CEC/IMC Clock Board 19D903305P1 Rev. E (or later) ±50 ppm for 2.048 and 1.544 MHz clocks Generates a 4.096 MHz clock phase-locked to selected 2.048 MHz bit clock Selected per currently selected redundant system clock (A/B)

One 360 kbps half-duplex serial channel transfers control and diagnostic messages between the T1/E1 Interface Card(s) and the Controller Board within a CEC/IMC interface module

\* These specifications are intended primarily for the use of the serviceman. See the appropriate Specifications Sheet for complete specifications.

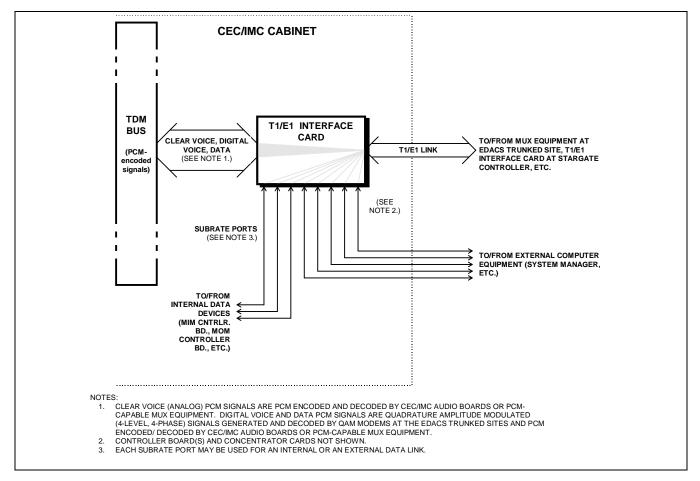

# DESCRIPTION

#### T1/E1 PORT

T1/E1 Interface Card 188D5909P1 provides a built-in T1 or E1 port for site-type CEC/IMC Digital Audio Switch interface modules (MIMs, NIMs, PIMs, etc.). This port allows direct interfacing to T1/E1 microwave, fiber-optic, or leased lines facilities. Consequently, co-located T1/E1 multiplexing (mux) equipment at the CEC/IMC is eliminated when the T1/E1 Interface Card is employed. In addition, CEC/IMC Audio Boards are also eliminated within the particular interface module.

Circuitry on the T1/E1 Interface Card can transfer PCM-encoded analog voice audio (clear voice) and PCMencoded modem data signals on the CEC/IMC TDM network to and from the T1/E1 line. Examples of modem data signals include Aegis encrypted voice data and mobile data to/from an EDACS trunked site which has modemequipped working channels.

Site-type CEC/IMC interface modules in which the T1/E1 Interface Card can be employed include MIMs (MASTR II/III Interface Modules), NIMs (Network Interface Modules) and PIMs (PBX Interface Modules). Within each of these CEC/IMC interface modules, one or more T1/E1 Interface Cards replace all Audio Boards.

The T1/E1 Interface Card furnishes twenty-four (24) full-duplex T1 channels in T1 mode and thirty-one (31) full-duplex E1 channels in E1 mode. T1/E1 mode selection is configurable at the CEC/IMC Manager (MOM PC) on a CEC/IMC-wide basis.

All CEC/IMC-related hardware is identical between T1 and E1 applications with the exception of unique Concentrator Cards which support T1/E1 connections into and out of the CEC/IMC cabinet; one Concentrator Card is required for T1 hook-ups and a different Concentrator Card is required for E1 hook-ups.

## SUBRATE PORTS

In addition to its T1/E1 port, the T1/E1 Interface Card also contains eight (8) subrate ports which can provide modem-less data links over spare T1/E1 channels. Some, all, or none of these ports can be utilized depending upon card configuration. Five (5) of the subrate ports support synchronous or asynchronous data links and the remaining three (3) are synchronous-only ports. Subrate port available/not available and sync/async settings are autoconfigured by the CEC/IMC Manager in accordance with the user-entered CEC/IMC Manager settings. These settings include T1 or E1 selection, card operating mode and the number of site channels required over the T1/E1 link.

The synchronous subrate data protocol conforms to the industry-standard DS0B subrate data multiplexing scheme. This standard allows multiplexing of five (5) 9600 baud synchronous ports on to a single T1/E1 channel. Any multiplexer conforming to this standard can transfer data to/from the synchronous subrate ports via the T1/E1 link. Only 9600 baud is supported on synchronous subrate ports. Port assignments are shown in Table 1 below.

Table 1 – Synchronous Subrate Port DS0B Assignments

| ← one DS0 (one T1/E1 channel; DS0B formatted) $\rightarrow$ |                         |                   |                   |                   |  |

|-------------------------------------------------------------|-------------------------|-------------------|-------------------|-------------------|--|

| sub-<br>channel 1                                           | sub-<br>channel 2       | sub-<br>channel 3 | sub-<br>channel 4 | sub-<br>channel 5 |  |

|                                                             | If subrate ports 1 – 5: |                   |                   |                   |  |

| port 1                                                      | port 2                  | port 3            | port 4            | port 5            |  |

| If subrate ports 6 – 8:                                     |                         |                   |                   |                   |  |

| (not used)                                                  | port 6                  | port 7            | port 8            | (not used)        |  |

The asynchronous subrate data protocol conforms to an Intraplex Inc. proprietary encoding/decoding format. Therefore, only an Intraplex mux or a second T1/E1 Interface Card can decode/encode asynchronous subrate data on the T1/E1 link. Each asynchronous subrate port requires one T1/E1 channel (DS0). Standard and non-standard baud rates up to 19,200 baud are supported. A typical example of data which may be transferred utilizing an asynchronous subrate port is System Manager-to-Site Controller data.

#### **OPERATING MODE**

In addition to T1 or E1 selection, T1/E1 Interface Card configuration includes the determination of a primary card operating mode referred to as "analog/modem mode". Other primary card modes not discussed within this introductory text will be supported in subsequent software/firmware releases.

#### Analog/Modem Mode

In the analog/modem mode, the T1/E1 Interface Card transfers PCM-encoded signals between the CEC/IMC TDM network and the T1/E1 line. PCM-encoded signals transferred by this mode include analog (clear) voice signals, modem-encoded digital voice signals (for example, Aegis encrypted voice to/from a modem-equipped trunked site working channel), and/or modem-encoded data signals (for example, mobile data to/from a modem-equipped trunked site). In this mode each site channel is assigned to a T1/E1 channel. In addition, as described later, this mode

# LBI-39107

allows use of the T1/E1 Interface Card's subrate ports if T1/E1 channels are available after site channel assignments. See Figure 1. This mode is designated "Analog or Digital Voice using Modems" at the CEC/IMC Manager (MOM PC).

#### NOTE

Modems used throughout EDACS networks for digital voice (Aegis, Voice Guard, etc.), data (mobile data, etc.) and uplink/downlink data transfers employ Quadrature Amplitude Modulation (QAM) techniques. QAM modems use 4-level 4-phase signals to transfer data over twisted pairs.

Two (2) CEC/IMC TDM bus slots coincide to one fullduplex T1/E1 channel. This is exactly analogous to a CEC/IMC Audio Board channel where two TDM bus slots coincide to one full-duplex 4-wire 600-ohm audio channel provided by the Audio Board. The T1/E1 Interface Card extracts a signal from one bus slot and sends it out on a T1/E1 channel. Accordingly, signals received on this same T1/E1 channel are applied to a different CEC/IMC TDM bus slot.

For example, a clear voice individual call originating from a console is placed on TDM bus 8, time slot 10 via the console's CIM as a PCM-encoded audio signal. Simultaneously, the T1/E1 Interface Card within a MIM extracts the call from bus 8, time slot 10 and sends it out over T1/E1 channel 5 (for example) to mux equipment at the respective EDACS trunked site. The PCM-capable mux equipment at the site then performs T1/E1 to audio conversions and the audio is then applied to the EDACS station. In this example, T1/E1 channel 5 also transfers radio-originated audio from the EDACS trunked site to a different TDM bus and/or slot in the CEC/IMC. The CIM within the CEC/IMC extracts this radio-originated individual call audio from the TDM bus and slot and it applies the extracted audio (after PCM decoding) to the console. This completes the full-duplex audio link.

When compared to Audio Board-equipped CEC/IMC interface modules, T1/E1 Interface Card-equipped CEC/IMC interface modules require fewer Card Cage slots. For example, a 24-channel non-redundant Audio Board-equipped MIM requires seven (7) Card Cage slots – one for

Figure 1 – Analog/Modem Mode

the Controller Board and six for the 4-channel Audio Boards whereas a 24-channel non-redundant T1/E1 Interface Card-equipped MIM operating in the analog/modem mode requires only two (2) Card Cage slots – one for the Controller Board and one for the T1/E1 Interface Card. This represents a savings of five (5) Card Cage slots.

As previously stated, free channels on each card's T1/E1 link are available for user data to/from the subrate ports. Subrate ports are auto-configured by the CEC/IMC Manager as shown in Table 2 in accordance with the number of free T1/E1 channels.

Table 2 – Subrate Port Assignments For

Analog/Modem Mode

| FREE CHANNELS<br>(PER CARD) | SUBRATE PORT AUTO-<br>CONFIGURATION *                                           |

|-----------------------------|---------------------------------------------------------------------------------|

| 0                           | no subrate ports available                                                      |

| 1                           | port $1 = async$<br>ports $2 - 8 = not available$                               |

| 2                           | port 1 = async<br>ports $2-5$ = sync<br>ports $6-8$ = not available             |

| 3                           | ports 1 & 2 = async<br>ports $3 - 5 =$ sync<br>ports $6 - 8 =$ not available    |

| 4                           | ports $1 - 3 = async$<br>ports $4 \& 5 = not available$<br>ports $6 - 8 = sync$ |

| 5                           | ports $1 - 4 = async$<br>port $5 = not available$<br>ports $6 - 8 = sync$       |

| greater than 5              | ports $1 - 5 = async$<br>ports $6 - 8 = sync$                                   |

"sync" = subrate port set for synchronous operation; "async" = subrate port set for asynchronous operation.

# **CEC/IMC SYSTEM CLOCKS**

# **A/B Redundant System Clocks**

Redundant clocking for the CEC/IMC's TDM network and T1/E1 circuits is provided by separate system clock circuits identified "A" and "B" throughout the CEC/IMC. These redundant clocks, generated by the CEC/IMC Clock Board(s), are applied to all T1/E1 Interface Cards and all Audio Boards within the CEC/IMC via the CEC/IMC Backplane. Normally, a CEC/IMC is factory-equipped with two (2) Clock Boards so if one fails the other can provide clocking (with A/B redundancy) while the failed board is removed for service.

# NOTE -

T1/E1 Interface Card applications require Clock Board 19D903305P1 Rev. E (or later).

Redundant CEC/IMC system clock selection within a T1/E1 Interface Card-equipped interface module is accomplished identically to redundant system clock selection within an Audio Board-equipped interface module. Clock A/B selection is dictated by the CEC/IMC MOM Controller Board in accordance with the start-up default and any following clock A/B fail messages received from other CEC/IMC interface modules (MIM, CIM, NIM, LRIM, etc.) The initial start-up or default clock is B. Refer the circuit analysis section entitled "CLOCK SELECTION AND GENERATION" (page 21) for additional details.

All T1/E1 Interface Card firmware/software releases support system clock redundancy. Assuming the redundant clock feature has been enabled at the CEC/IMC Manager, redundant clock switching (B to A or A to B) will occur if several interface modules sense and report clock failures to the MOM Controller Board. Refer to the Circuit Analysis section of this manual for detailed circuit descriptions and additional high-level system clock redundancy information. System clock A/B redundancy *is not* available when the T1/E1 Interface Card operates in the stand-alone mode. This mode is not supported in the initial firmware/software release(s).

# **Network Synchronization Design**

Within a given CEC/IMC network, all T1/E1-connected nodes utilizing T1/E1 Interface Cards must remain frequency-locked at all times. Therefore, the system design allows for total network synchronization by offering the following clock synchronization options. The term "node" in this text refers to equipment external to the CEC/IMC with T1/E1 line interfacing provided by a T1/E1 Interface Card at the CEC/IMC, or another CEC/IMC:

Master – The CEC/IMC is the master source of network clock synchronization and all other nodes – for example, muxes at EDACS trunked sites – are slaved (synchronized) to it. A CEC/IMC Clock Board generates the master clocking for the CEC/IMC and for all of the nodes. Installed Clock Boards within the CEC/IMC basically "free run" since they are not synchronized to any external source. Redundant clocking within the CEC/IMC is provided by the A and B system clocks.

Within a CEC/IMC, this clock sync option is selected by setting all Clock Board DIP switches to "master mode" and, via the CEC/IMC Manager, setting all T1/E1 Interface Cards' "slave clock mode" to "none".

# LBI-39107

Slaved To T1/E1 Line - CEC/IMC redundant A/B system clocks generated on the installed Clock Board(s) are synchronized to one T1/E1 line from a node - for example, the telephone company. Redundant line synchronization may be provided by a second T1/E1 line interfaced via a second card. CEC/IMC system clocks are slaved to the (in use) line's external node. The T1/E1 Interface Card passes synchronization from its T1/E1 line to the installed Clock Boards via a set of redundant slave A and slave B sync lines on the CEC/IMC Backplane. These slave sync lines should not be confused with the redundant A/B system clock lines on the Backplane; they have similar designations but they are not directly related. For example, a CEC/IMC using this option may be operating off of its B system clocks but using the slave A sync line.

Within the CEC/IMC, this option is selected by setting all Clock Board DIP switches to "slave to 8 kHz mode". Also, to set-up the driver source for each of the two sync lines, one T1/E1 Interface Card's "slave clock mode" must be set to "A" and another card must be set to "B" for sync redundancy, *or* for no sync redundancy, one card's "slave clock mode" can be set to "A & B". The "slave clock mode" setting is accomplished via the CEC/IMC Manager.

If configured for sync redundancy with two T1/E1 Interface Cards the two T1/E1 Interface Cards must be connected to nodes which are *frequencylocked together*. For example: two EDACS trunked sites linked to the CEC/IMC via *a telephone company's T1/E1 lines*.

Slaved to External 1.544 MHz Clock -CEC/IMC redundant A/B clocks generated on a Clock Board are synchronized to one external 1.544 MHz clock source from external equipment. Typical external equipment examples include a T1 multiplexer, microwave link equipment, or fiberoptic network equipment. In these equipment examples, the equipment's timing or clock output is utilized. Each Clock Board in the CEC/IMC must be supplied with an external 1.544 MHz clock either from the same piece of external equipment if no redundancy is required, or from different external equipment (one per Clock Board) for redundant slaving. 1.544 MHz clocking is applied to a Clock Board via RS-422 or RS-232 input connections at the board's 24-pin dual-inline Backplane Card Cage slot connector.

This option is entered by setting each installed Clock Board's DIP switches to "slave to external 1544 kHz mode" and, via the CEC/IMC Manager, setting all installed T1/E1 Interface Boards' "slave clock mode" to "none".

• Slaved to External 2.048 MHz Clock (E1 only) – This option is identical to the previously described option except a 2.048 MHz clock frequency is utilized. Also, this option is only available if CEC/IMC T1/E1 Interface Cards operate in E1 mode.

This option is entered by setting each installed Clock Board's DIP switches to "slave to external 2048 kHz mode" and, via the CEC/IMC Manager, setting all installed T1/E1 Interface Boards' "slave clock mode" to "none".

The following guidelines must be followed for network synchronization. Here, the term "node" refers to any equipment interfaced to the CEC/IMC via a T1/E1 line using a T1/E1 Interface Card, the CEC/IMC itself, and/or any equipment supplying source clock timing to the CEC/IMC:

- One node in the system must be the MASTER source of network timing "the MASTER node". The CEC/IMC will support a primary and a redundant (back-up) MASTER node source of timing as described in the preceding text.

- Examples of MASTER nodes include a CEC/IMC, an EDACS trunked site interfaced to the CEC/IMC via a T1/E1 Interface Card-equipped MIM, and EDACS Jessica PBX Gateway equipment interfaced to the CEC/IMC via a T1/E1 Interface Card-equipped PIM. Again, there can be only one MASTER node in a system (plus a redundant MASTER node).

- All leased T1/E1 line facilities from a telephone company are frequency-locked by the telephone company. If any phone company T1/E1 line connections exist in the network, one of the connections must be the MASTER node source of timing. Any other phone company T1/E1 line connection may be the redundant MASTER node source of timing. Leased line-interfaced node examples may include MIM-to-EDACS trunked site T1/E1 links, NIM-to-NIM T1/E1 links, and T1/E1 connections through an MD110 (Jessica).

- Any node using analog interfaces (including analog connections to/from an MD110 to the phone company) may be disregarded for synchronization purposes.

- If a node is not the MASTER node, it must be slaved to the T1/E1 line to/from the MASTER node.

# **CIRCUIT ANALYSIS**

## NOTE

This circuit analysis contains descriptions of hardware features which may not be available in the initial firmware/software release(s) of the T1/E1 Interface Card and CEC/IMC Manager.

# MICROPROCESSOR CIRCUITS

## **Microprocessor**

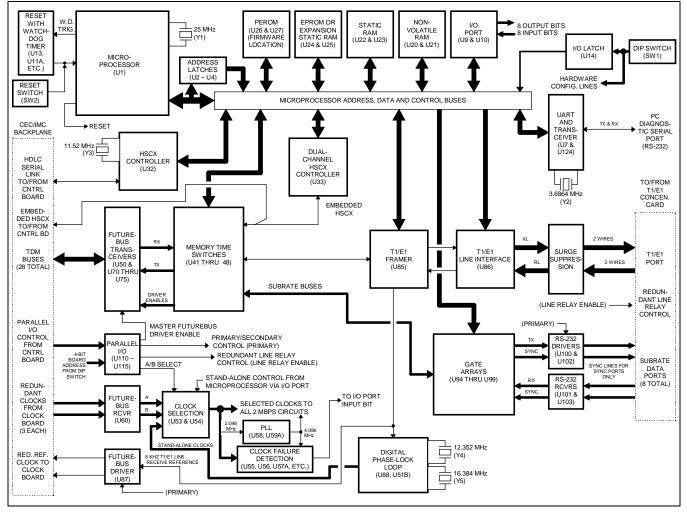

Control processing for the T1/E1 Interface Card is provided by U1, an Intel 80C186 (or equivalent) 16-bit microprocessor. It runs at 25 MHz as set by crystal Y1. DC operating power is provided by the +5 Vdc power received from the card's +5V power supply line. Support circuits include:

• reset circuit with watchdog timer

- address latches

- memory ROM, RAM and non-volatile RAM

- a single-channel UART which provides a PC serial port for diagnostic operations

- two dual-channel high-speed serial controllers (HSCX)

- DIP switch interface

- an input/output (I/O) port

# **Reset Circuit With Watchdog Timer**

Reset circuitry on the T1/E1 Interface Card consists of a microprocessor supervisory chip, a monostable multivibrator, several logic gates and an NPN transistor. This circuitry resets the microprocessor and the entire card at power-up, or if the 5 Vdc power supply falls below approximately 4.65 Vdc, or if the microprocessor fails to periodically write to the reset circuit. This last case is a

"watchdog" timer function. The watchdog timer may be disabled by a DIP switch setting [schematic diagram sheet 1].

Integrated circuit U13 is a microprocessor supervisory chip that performs the power-up reset and most watchdog timer functions for the reset circuit. Microprocessor U1 is in the reset or inactive state whenever its reset input at pin 24 is low. !RES from U13 pin 15 drives this active-low processor input.

Manual resets may be performed by push-button switch SW2 which is mounted on the card's front panel. When pressed, SW2 simply grounds the !RES line. Switch contact debouncing is provided by C4 and R34.

#### **Power-Up Reset**

At power-up, U13 holds its active-low reset output at pin 15 (!RES line) low until approximately 50 milliseconds *after* the +5V power supply line stabilizes. The T1/E1 Interface Card is in a reset (non-operating) state during this time.

#### **Unregulated +5V Reset**

As previously stated, U13 will also reset U1 if the +5V supply line falls below approximately 4.65 Vdc. This resets the card and thus prevents unpredictable operating errors during unstable power supply conditions. Reset will be released approximately 50 milliseconds after the +5V line raises above 4.75 Vdc.

## Watchdog Timer Reset

During normal card operation U1 periodically pulses (at least every 1.5 seconds) the watchdog timer circuit by writing to address 40000H. This causes active-low pulses to simultaneously appear at the micro's active-low !WR line (U1 pin 63) and at its active-low output identified !WDOG\_TRIG (U1 pin 25). These logic lines are applied to the inputs of OR gate U6C. When !WR and !WDOG\_TRIG transition low, U6C's output triggers monostable multivibrator U11A. This monostable is utilized to ensure valid triggering of U13's watchdog input; it extends the very narrow watchdog trigger pulse from U1.

The monostable's active-low output and a logic line from the watchdog enable/disable DIP switch are logically ANDed by U12A. The output of this gate drives transistor Q1 which in turn, drives U13's watchdog trigger input.

If watchdog enable/disable switch SW1 position 1 is in the "CLOSED" or "ON" position (watchdog disabled), the !WDOG\_DIS line at U12A pin 2 remains low. This prevents the monostable's pulse from passing through the AND gate and thus Q1 remains off at all times. In this case, U13's watchdog input always floats. Circuitry inside U13 disables the watchdog reset function when the watchdog trigger input floats.

If watchdog enable/disable switch SW1 position 1 is in the "OPEN" or "OFF" position (watchdog enabled), the !WDOG\_DIS line at U12A pin 2 remains high per pull-up resistor R29. This allows the pulse from monostable U11A to pass through the AND gate and Q1 and pulse U13's watchdog trigger input. Thus, the watchdog circuit is active and it will reset U1 if U1 does not periodically trigger it.

#### **Microprocessor Reset Output**

When microprocessor U1 is reset by U13, U1 pulls its reset output at U1 pin 57 high. This logic level is applied to the succeeding gates, U6A, U31E and U120D, which drive the RESET (active high) and !RESET (active low) lines. These two reset lines are used to reset all other logic circuitry on the card such as the HSCX controller chips.

#### **NOVRAM Disable**

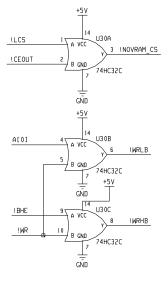

U13 also outputs a logic signal at pin 12 (!CEOUT). This output is used to insure the NOVRAM (non-volatile RAM) chips on the card are not accessed during unstable power supply conditions. U13 pin 12 transitions low only when the +5V supply line is above the reset threshold voltage of approximately 4.65 Vdc. OR gate U30A gates !LCS on to the !NOVRAM\_CS line only when !CEOUT is low [schematic diagram sheets 1 and 2].

# Address Latches

The 80C186 microprocessor employs a multiplexed 16bit address and data bus which is identified AD0 thru AD15. It uses this bus to transfer data to and from memory and I/O devices *and* it outputs the lower sixteen bits of the address to address latches U2 and U3. Two nonmultiplexed address bits, A16/S3 and A17/S4, are also utilized. These bits are latched by dual flip-flop U4 [schematic diagram sheet 1].

During an external memory or I/O read or write, microprocessor U1 first applies the 18-bit address to its AD0 thru AD15, A16/S3 and A17/S4 outputs. Next, it latches the 18-bit address into the address latches on the falling edge of the ALE pulse (from U1 pin 61). Latched address lines are identified A[0] thru A[17] and the complete address bus is labeled A[0:17]. These lines are applied to memory and I/O chips on the card. The bidirectional data bus is identified D[0:15].

# **Memory**

The T1/E1 Interface Card's memory map includes 128K x 16 bits of PEROM, 32K x 16 bits of EPROM (not normally used), 128K x 16 bits of non-volatile RAM

(NOVRAM), and  $32K \times 16$  bits of static RAM. The PEROM chips store the operating firmware code. With the exception of the static RAM chips, all memory chips are socketed. A detailed memory map chart is included on the schematic diagram [schematic diagram sheet 2].

#### PEROM and EPROM

Currently, as noted on the schematic, no EPROM chips are installed and all operating firmware code is stored in two PEROM (Programmable Erasable ROM) chips, U26 and U27. PEROMs are very similar in functionality to 5-volt flash ROMs. Future upgrades of this card will support flash firmware programming. The EPROM sockets can be loaded with static RAM chips if volatile memory expansion is required.

U26 and U27 are each 128K x 8-bit PEROM chips which together provide the total 128K x 16 bits of firmware storage space. U26 handles the lower byte, D[0] thru D[7], and U27 handles the upper byte, D[8] thru D[15]. Chip selection is accomplished via the !UCS from U1 pin 34. This active-low chip select line is applied to pin 22 of both PEROMs. Therefore, both chips are selected simultaneously when a 16-bit op-code fetch occurs. Read/write control is provided by the active-low !RD and !WR lines from U1. The !WR line is only utilized during PEROM reprogramming.

#### **NOVRAM and Static RAM**

A two megabit sector of non-volatile RAM is used to store data which must be retained through a power loss cycle. U20 and U21, each a 128K x 8-bit device, provide the 128K x 16-bit NOVRAM sector. U20 stores low bytes and U21 stores high bytes.

As previously described, U13 in the reset circuit outputs a logic signal at pin 12 (!CEOUT) which is used to insure the NOVRAM chips on the card are not accessed during unstable power supply conditions. NOVRAM chip selection is generated by gating the !LCS line from U1 pin 33 through OR gate U30A using the !CEOUT line from U13 pin 12. !CEOUT normally remains low but it transitions high if the +5V supply becomes unstable. This prevents NOVRAM write errors.

Static RAMs U22 and U23 provide 32K x 16-bits of volatile RAM for the T1/E1 Interface Card. U22 stores lower bytes and U23 stores upper bytes. Chip selection is provided by the active-low !MCS0 line from U1 pin 38. !MCS0 is applied to the chip-select input at pin 20 of each static RAM chip.

Read/write control for the NOVRAM and static RAM is provided by the active-low !RD (read), !WRLB (write low byte), and !WRHB (write high byte) lines. !RD from U1 pin 62 is applied to the active-low output-enable inputs

of all four RAM chips. During 8-bit RAM reads, U1 actually enables and reads both the upper and lower byte RAM chips – just like a 16-bit read – but it uses only the upper byte or the lower byte, as required. !WRLB and !WRHB are generated from A[0], !BHE and !WR by OR gates U30B and U30C. These two byte-oriented active-low write enable lines are also used for HSCX controller and gate array 8-bit writes. This design allows 8-bit or 16-bit writes in the 16-bit bus system.

# PC Diagnostic Serial Port

DB-9 connector J5 [schematic diagram sheet 10], mounted on the front panel of the T1/E1 Interface Card, provides a serial port hook-up for a Personal Computer (PC) type interface. Using this port and custom software executing on a PC, diagnostic tests may be performed on the card.

Two (2) integrated circuits support the port, U7 and U124 [schematic diagram sheets 1 and 10]. U7 is a singlechannel 8-bit UART which communicates with microprocessor U1 via the lower data bus byte, D[0] thru D[7]. U124 is an RS-232 (EIA-232-D) transceiver chip which contains three TTL-to-RS-232 drivers and three RS-232-to-TTL receivers; however, only one of each is utilized for the diagnostic port. Serial data from the PC is applied to J5 pin 2 (RX) and serial data is sent to the PC via J5 pin 3 (TX). A common ground for both signals is located at J5 pin 5.

RS-232-level serial data on J5 pin 2 is converted to TTL levels by the receiver. The receiver's converted output at U124 pin 15 drives the UART's TTL-level receive data input via RxD0. Similarly, TTL-level transmit data from the UART (U7 pin 4) is applied to U124 pin 14 via TxD0. The driver within U124 converts this TTL-level serial data to RS-232 levels and drives J5 pin 3 via the TX line.

As previously stated, UART U7 communicates with microprocessor U1 via the lower data bus byte. Control lines from U1 include the active-high RESET line, and the active-low !RD (read), !WR (write), and !SER\_EN (serial enable) lines. U7's active-low interrupt output at pin 16 is inverted by U5A and applied to a U1's active-high interrupt input at pin 44 via the UARTXINT line.

## **Dual-Channel HSCX Controllers**

Two Siemems 82525 (or equivalent) dual-channel HSCX controller chips, U32 and U33, furnish advanced high-speed serial communications links for the T1/E1 Interface Card. These channels are identified A and B at each HSCX controller chip. Channel A of U32 is not currently used [schematic diagram sheet 2].

#### U32 Channel B – Controller Board HDLC Link

Using an HDLC protocol, channel B of U32 links the T1/E1 Interface Card to the Controller Board via the AU\_SER\_CNTRL line. Within a CEC/IMC interface module (MIM, NIM, etc.) equipped with T1/E1 Interface Card(s), this 360 kbps single-wire half-duplex serial channel transfers control and diagnostic messages between the active Controller Board and the T1/E1 Interface Card(s) within the interface module. With the exception of the parallel I/O control lines from the Controller Board, all Controller Board-to-T1/E1 Interface Card control messaging occurs over this link.

Like the parallel I/O control lines, AU\_SER\_CNTRL is routed between the Controller Board and the T1/E1 Interface Card(s) via the CEC/IMC Backplane and the interface module's Local Bus Cable(s). If the interface module contains more than one T1/E1 Interface Card, a Controller Board polling scheme individually communicates with each T1/E1 Interface Card as needed.

Channel B of U32 is normally in a listening or slave mode and it only transmits to the Controller Board when specifically polled by it. This serial link configuration is the 82525's point-to-multipoint configuration mode. The Controller Board's HSCX port is the master and T1/E1 Interface Cards' ports are slaved to it. Serial baud rate is determined by 11.52 MHz crystal Y3 and U32 HSCX setup programming from microprocessor U1.

Serial connections are located at U32 pins 13, 14 and 16. AU\_SER\_CNTRL line is applied to the CEC/IMC Backplane via 96-pin DIN connector J1 pin 8C. J1 is the top DIN connector at the rear of the card [schematic diagram sheet 10].

#### U33 Channels A & B – Embedded HSCX Links

| NOTE        |          |         |        |          |      |      |  |  |

|-------------|----------|---------|--------|----------|------|------|--|--|

| NOTE        |          |         |        |          |      |      |  |  |

| U33 circuit | ry descr | ibed in | n this | section  | is   | not  |  |  |

| functional  | with     | initia  | 1 fi   | rmware/s | oftv | vare |  |  |

| release(s). |          |         |        |          |      |      |  |  |

Channels A and B of U33 are utilized to synchronize 64 kbps data channels on a slotted two megabit bus. These proprietary-protocol channels can independently route data to/from the T1/E1 line or to/from the CEC/IMC TDM network.

Data from the CEC/IMC TDM network or the T1/E1 line is applied to U33 via HSCX\_PCM\_RX at U33 pin 9 (channel A input) and pin 16 (channel B input). Correspondingly, data is sent to the TDM network or the T1/E1 line via HSCX\_PCM\_TX from U33 pin 12 (channel A output) and pin 13 (channel B output). Switching or signal routing to and from U33 is accomplished via CMOS memory time switch (MTSC) chips which are described in detail later in this document. Basically, U33 HSXC channels A and B can be routed to/from TDM bus/slot channels or T1/E1 channels via the MTSC chips. One MTSC chip (U48) is used to route HSCX\_PCM\_TX data from U33 to the T1/E1 framer chip (U85). Also, one MTSC chip (U41) routes data from the framer chip to U33 via HSCX\_PCM\_RX.

The HSCX\_PCM\_TX and HSCX\_PCM\_RX signals are also present on the CEC/IMC Backplane so the interface module's Controller Board can directly access the HSCX TDM buses. In future software/firmware releases, this will allow direct embedded Controller Board 64 kbps HSCX channels over the T1/E1 line or over the CEC/IMC TDM network.

To provide redundant T1/E1 Interface Card pairing capability, HSCX\_PCM\_RX and two related clock signals, FSYNC and 20048KHZ, are buffered and gated by drivers U120A thru U120C before application to the CEC/IMC Backplane [schematic diagram sheet 10]. The buffered and gated signals, HSCX\_RX\_F, FSYNC\_F and 2048\_F are present at 96-pin DIN connector J1 pins 5C, 7C and 4C respectively. HSCX\_PCM\_TX is present on J1 pin 6C. Drivers U120A thru U120C are enabled by AND gate U57B. Inputs to U57B include card address bits ADDR[0], !ADDR[1] (inverted ADDR[1] via inverter U31F), and PRI/!SEC. These logic controls guarantee the drivers are not enabled unless the card address is 1 or 5 and it is in primary mode (PRI/!SEC = high). Cards 1 and 5 are configured as redundant paired cards. The active Controller Board's HSCX chip can transmit directly to the MTSC chips via HSC\_PCM\_TX.

#### **Microprocessor Interface**

As shown by the D[0] thru D[7] connections at U32 and the D[8] thru D[15] connections at U33, U32 is mapped into the lower byte of the microprocessor's data bus and U33 is mapped into the upper byte. Both chips are simultaneously selected, read, and written to by U1. This is accomplished by activating the active-low !PCS5 or !PCS6 (peripheral chip selects) signals from U1 pins 31 and 32 respectively. The OR function is provided by AND gate U12B and these active-low logic lines; if !PCS5 or !PCS6 transition low (active) the AND gate's output transitions low (active). The resultant active-low !HSCX\_CS line is applied to the chip-select input at each HSCX controller chip (U32 and U33 pin 8). Two !PCS lines are required since the HSCX controller chips require more address space than one !PCS line can provide.

Each HSCX controller is equipped with an interrupt output which is used to signal U1 when HSCX service is

required. This active-low open-drain output at pin 28 of each HSCX chip is logically ORed by joining the two outputs together. The inverted and buffered signal from U31D is applied to U1's interrupt input at pin 41 via the HSCX\_INT connection. When U1 is interrupted by HSCX\_INT, it services the HSCX chip(s) as required via the data bus.

# **Configuration DIP Switch**

SW1 is an 8-position DIP switch used to configure certain card parameters [schematic diagram sheet 1]. Although the entire switch is read by the microprocessor via U14 at card power-up or reset, current firmware only recognizes positions 5 thru 8 – the card address setting. Therefore, a card reset is not necessary after a position 1, 2 or 3 change; hardware connections to these three switches bypass the microprocessor circuits. Currently, SW1 position 4 is not used. Each switch position has a pull-up resistor which pulls the respective U14 logic input high when the switch position is "OPEN" or "OFF".

Microprocessor U1 reads the 8-position DIP switch via octal transceiver U14 and OR gate U6D. Chip selection for U14 is mapped to the same address as the watchdog timer circuit – 40000H – the !WDOG\_TRIG line. U1 writes to address 40000H to trigger the watchdog timer circuit but it reads 40000H to enable U14 and read the DIP switch settings. OR gate U6D enables U14 when !RD and !WDOG\_TRIG are both low via U14's active-low enable input at pin 19. As previously stated, current firmware only recognizes SW1 positions 5 thru 8 – the card address setting.

#### **Positions 1 Thru 3**

Positions 1 thru 3 enable/disable certain hardware functions. All three of these switches should remain in the "OPEN" or "OFF" (enabled) position during normal operation; they are provided for testing and troubleshooting procedures only.

SW1 position 1 enables/disables the watchdog timer via the !WDOG\_DIS connection to AND gate U12A [schematic diagram sheet 1]. This gate is located in the reset circuit. When the switch is "OPEN" or "OFF", !WDOG\_DIS is high and the watchdog timer is enabled. See previous circuit analysis descriptions on the watchdog timer reset circuit for additional details (page 10).

SW1 position 2 controls the !PRIMARY\_EN line. When this line is low (test state), the card is forced into primary operation mode. !PRIMARY\_EN is applied to the preset input of data flip-flop U111B [schematic diagram sheet 9]. This flip-flop generates the PRI/!SEC and !PRIMARY primary/secondary control lines which are distributed throughout the card to control primary/secondary operation. When !PRIMARY\_EN is high (normal state), the parallel I/O control circuits can control the primary/secondary lines. See the section entitled "PARALLEL I/O CONTROL", subsection "Primary/Secondary Mode Selection" (page 34) for additional details.

SW1 position 3 controls the Futurebus driver enable line, !FBUS\_DRV\_EN. When "OPEN" or "OFF" this line is high (normal state) and the parallel I/O control lines from the Controller Board can enable and disabled the Futurebus drivers on the T1/E1 Interface Card. When "CLOSED" or "ON", !FBUS\_DRV\_EN is pulled low (test state) and the Futurebus drivers are always enabled. !FBUS\_DRV\_EN is applied to the preset input of data flipflop U51A [schematic diagram sheet 4]. This flip-flop generates the !FBUS\_EN line which controls (enables/disables) Futurebus transceivers U50 and U70 thru U75 [schematic diagram sheets 4 and 5]. Again, this switch should be left "OPEN" or "OFF" at all times.

#### Positions 5 Thru 8 – Card Address Setting

As shown in Table 3, positions 5 thru 8 specify the card address in a binary form. Only address 1 is valid with current firmware. Like the CEC/IMC Audio Boards, each T1/E1 Interface Card within a particular CEC/IMC interface module (MIM, NIM, etc.) must have a unique card address setting. ADDR[0] thru ADDR[3] at U14's inputs are also applied to 4-bit comparator U110 in the parallel I/O control circuit [schematic diagram sheet 9].

Table 3 – SW1 Positions 5 Thru 8; Card Address Setting

| CARD<br>ADDRESS | 5<br>(MSB) | 6 | 7 | 8<br>(LSB) * |

|-----------------|------------|---|---|--------------|

| 1               | 0          | 0 | 0 | 1            |

| 2 **            | 0          | 0 | 1 | 0            |

| 3 **            | 0          | 0 | 1 | 1            |

| 4 **            | 0          | 1 | 0 | 0            |

| 5 **            | 0          | 1 | 0 | 1            |

| 6 **            | 0          | 1 | 1 | 0            |

| 7 **            | 0          | 1 | 1 | 1            |

| 8 **            | 1          | 0 | 0 | 0            |

\* "0" = CLOSED/ON; "1" = OPEN/OFF

\*\* Card addresses 2 thru 8 are not valid with initial software/firmware release(s). See SRN-1000-xx for specific details.

# **Input/Output Port**

A 16-bit I/O port allows microprocessor U1 to monitor and control several card functions. Octal latch U10 and OR gate U6B form the 8-bit input side and octal latch U9 and OR gate U8A form the 8-bit output side [schematic diagram sheet 1].

Microprocessor U1 reads the eight input bits by reading address 40180H. The input bits are defined in Table 4. A read of this address activates !I0\_EN (U1 pin 29) and !RD (U1 pin 62). These two active-low logic signals are ORed by U6B and the resultant low-going pulse is applied to the output enable input of U10. As a result, logic levels on U10's data inputs (pins 2 thru 9) are applied to the lower byte of the microprocessor's data bus, D[0] thru D[7]. U10's 3-state outputs to the data bus return to a high-impedance state when its enable input (U10 pin 1) returns high.

#### Table 4 – I/O Port Input Bits

| U10 INPUT<br>LABELING                     | MONITORED PARAMETER *                                                                         |

|-------------------------------------------|-----------------------------------------------------------------------------------------------|

| PRI/!SEC<br>(U10 pin 2)                   | Primary/secondary card mode:<br>0 = secondary mode<br>1 = primary mode                        |

| CLOCKS_OK<br>(U10 pin 3)                  | Clock monitor:<br>0 = one or more clocks has failed<br>1 = all selected clocks operating      |

| CLK_SELA_!B<br>(U10 pin 4)                | Selected CEC/IMC clocks:<br>0 = B clocks selected<br>1 = A clocks selected                    |

| CARD_SEL<br>(U10 pin 5)                   | Parallel I/O card select:<br>0 = not selected by parallel I/O<br>1 = selected by parallel I/O |

| none (U10 pin 6)                          |                                                                                               |

| none (U10 pin 7)                          | By adding/removing pull-down resistors, these bits are used to set a                          |

| none (U10 pin 8)                          | hardware revision number (in binary) which the processor can read.                            |

| none (U10 pin 9) $* 0 = \log \log \log 1$ |                                                                                               |

\* 0 = logic low; 1 = logic high

Microprocessor U1 writes to the eight output bits by writing a byte to address 40180H, the same address as the input port. A write to this address activates !I0\_EN (U1 pin 29) and !WR (U1 pin 63). These two active-low logic lines are NORed by U8A and the resultant low-going pulse is applied to U9's latch enable input at pin 11. Consequently, the written data byte placed on D[0] thru D[7] by U1

latches at U9's outputs (pins 12 thru 19). Each output bit is defined in Table 5.

Table 5 – I/O Port Output Bits

| U9 OUTPUT<br>LABELING          | CONTROLLED PARAMETER *                                                                                                                          |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| T1/!E1<br>(U9 pin 19)          | T1/E1 mode select:<br>0 = E1 mode<br>1 = T1 mode                                                                                                |

| MASTER<br>(U9 pin 18)          | Stand-alone clock mode mstr/slave select:<br>0 = slave mode<br>1 = master mode                                                                  |

| STAND_<br>ALONE<br>(U9 pin 17) | Stand-alone clock mode enable/disable:<br>0 = disabled (uses Backplane clocks)<br>1 = enabled (uses clocks from on-card<br>digital PLL circuit) |

| SYNCA_EN<br>(U9 pin 16)        | 8KHZ_SYNCA clock line enable/disable:<br>0 = disabled<br>1 = enabled                                                                            |

| SYNCB_EN<br>(U9 pin 15)        | 8KHZ_SYNCB clock line enable/disable:<br>0 = disabled<br>1 = enabled                                                                            |

| !LOS<br>(U9 pin 14)            | Controls SIGNAL ACTIVE indicator DS5:<br>0 = LED  off<br>1 = LED  on                                                                            |

| FRAME_<br>SYNC<br>(U9 pin 13)  | Controls FRAME SYNC indicator DS6:<br>0 = LED  off<br>1 = LED  on                                                                               |

| ID_LED_ON<br>(U9 pin 12)       | Controls ID indicator DS3:<br>0 = LED off<br>1 = LED on                                                                                         |

\* 0 = logic low; 1 = logic high

## **Status Indicators**

The T1/E1 Interface Card is equipped with several LED (light-emitting diode) indicators on its front panel which display the status of various card operating conditions. See Table 6 for details.

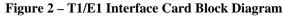

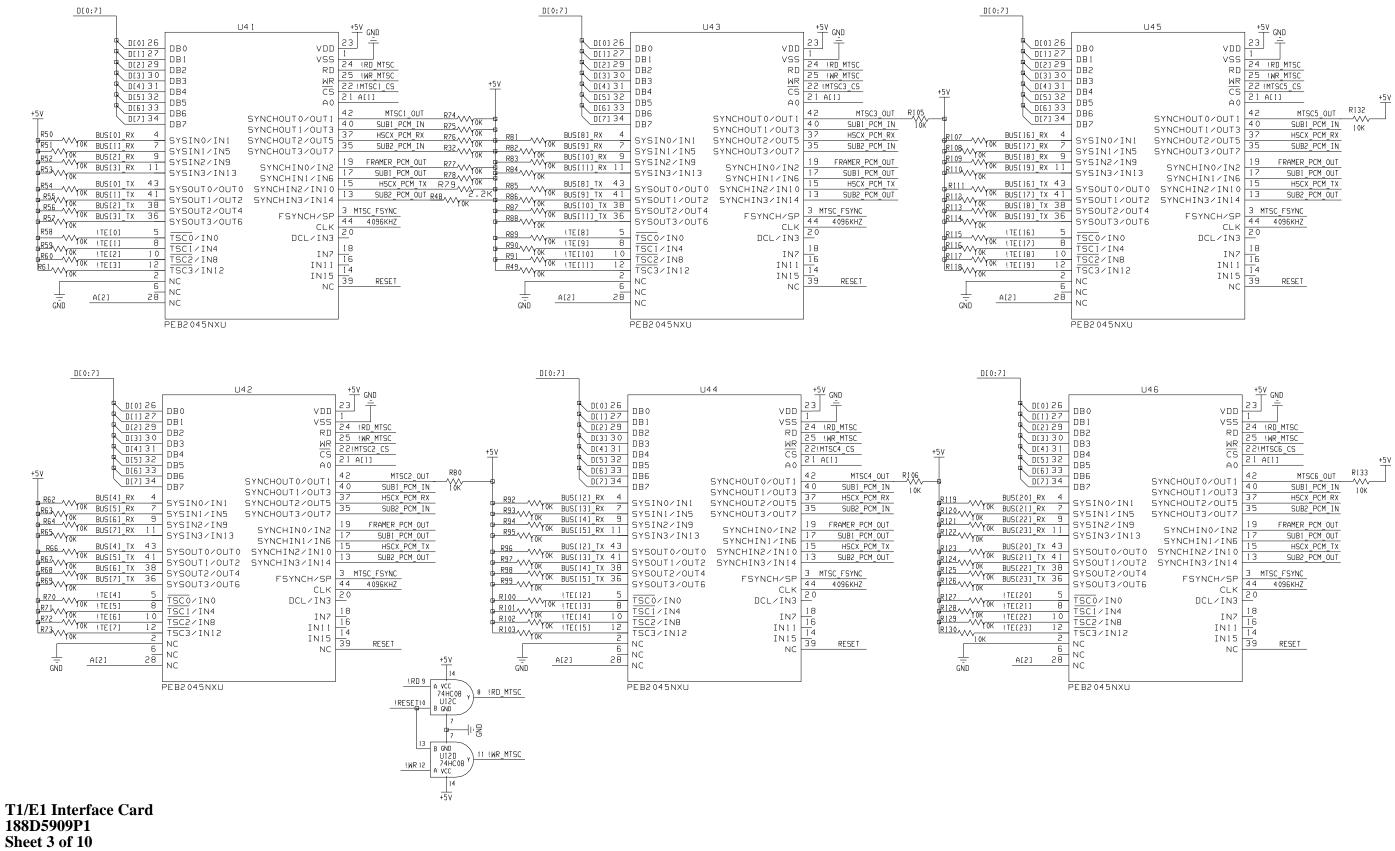

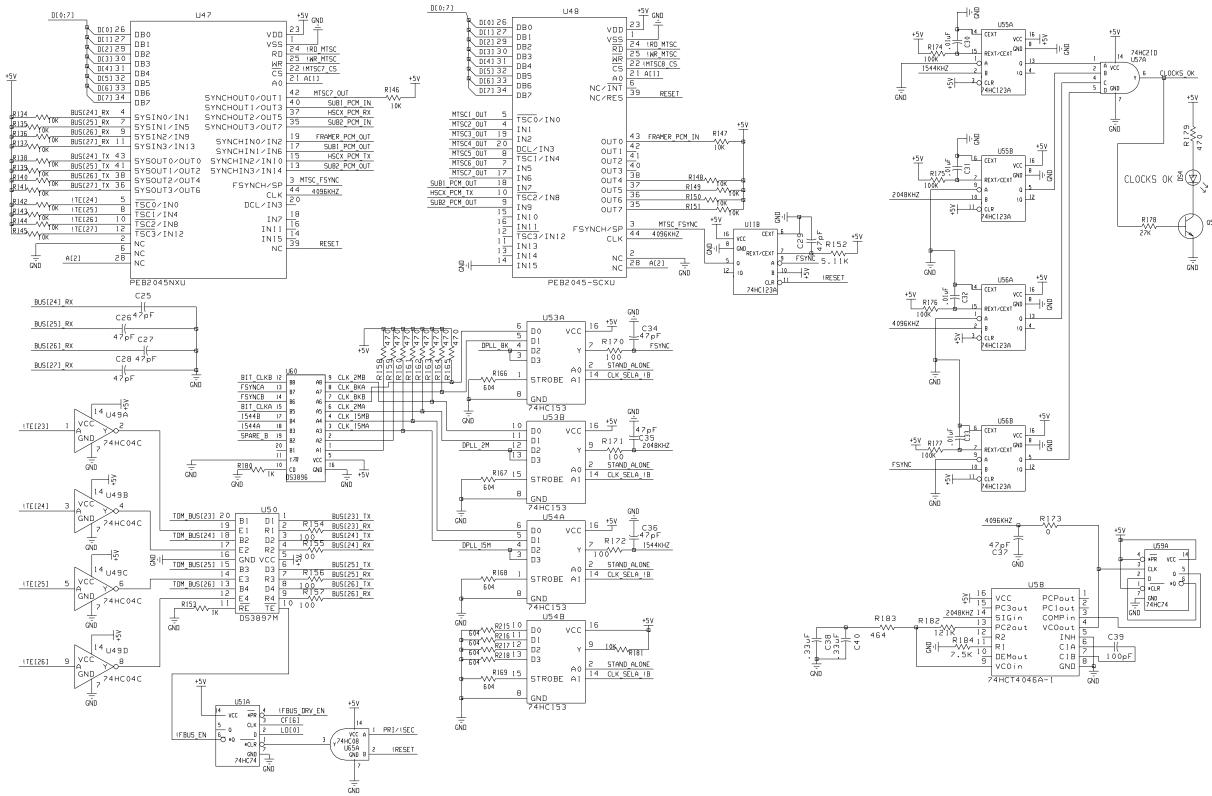

## **MEMORY TIME SWITCHES**

A group of Siemens PEB 2045 (or equivalent) CMOS memory time switch (MTSC) integrated circuits are utilized on the T1/E1 Interface Card to route PCM audio, subrate data, and embedded HSCX data as needed. These MTSC chips are basically 64 kbps channel exchanges. A number of two megabit buses (2.048 Mbps) are routed to and from each MTSC. Each two megabit bus contains

# **CIRCUIT ANALYSIS**

thirty-two (32), 64 kbps channels. The MTSC circuits can take any input channel/slot and route it to any output channel/slot. "Speech memory" within each MTSC chip stores incoming PCM audio or data during a frame and sends it out during the next frame. "Connection memory" stores input-to-output routing maps.

As shown in Figure 3, the MTSC chips establish channels between the T1/E1 framer and the TDM network, between the gate arrays and the T1/E1 framer, and between the gate arrays and the TDM network. Also, embedded HSCX support is provided by the channels between the HSCX controller (U33) and the TDM network, and between the HSCX controllers and the T1/E1 framer. The T1/E1 framer, not shown in the figure, is a part of the T1/E1 line interface which synchronizes signals to/from the T1/E1 line. The gate arrays provide the interfaces for the subrate ports.

The first stage of MTSC chips consists of U41 thru U47 [schematic diagram sheets 3 and 4]. As shown in Figure 3, these MTSC chips are designated MTSC 1 thru MTSC 7 respectively. All seven operate in a "primary access configuration" mode. In this mode, the each MTSC provides a 4 x 4 non-blocking switch. A primary access MTSC is broken into two interfaces, the system side and the synchronous side. The system sides of U41 thru U47 are used to interface to the CEC/IMC TDM network. The synchronous sides are used to interface to on-card

peripherals including the HSCX controllers, the T1/E1 framer (via U48), and the gate arrays chips (U94 thru U99). The gate array chips interface the subrate ports to the MTSC chips. Refer to Table 7 for MTSC 1 thru 7 (U41 thru U47) I/O mapping.

The second stage consists of a single MTSC chip, U48 [schematic diagram sheet 4]. This MTSC, designated MTSC 8, operates in "standard configuration" mode to provide a unidirectional 16 x 8 switch – 16 inputs and 8 outputs; however, as shown in Figure 3, only ten (10) inputs and a single (1) output are utilized. U48's sole purpose is to consolidate traffic *to* the T1/E1 framer. Refer to Table 8 for MTSC 8 (U48) I/O mapping.

As shown in Figure 3 and Table 7, each MTSC in the first stage connects to four (4) TDM buses on its system side and each has access to on-card peripheral buses on its synchronous side. This provides each on-card peripheral (framer, HSCX controller, and gate arrays) connections to/from the four (4) backplane TDM buses interfaced by the particular MTSC. Therefore each peripheral may access any of the twenty-eight (28) TDM buses using MTSC 1 thru MTSC 7 (U41 thru U47 respectively). As shown in Figure 3 and Table 8, a single output from each first stage MTSC is applied to an MTSC 8 (U48) input so TDM bus data may be selectively transferred to the T1/E1 framer under microprocessor U1 control.

| LED  | FRONT<br>PANEL<br>LABELING | SCHEMATIC<br>DIAGRAM<br>SHEET | FUNCTION                                                                          |

|------|----------------------------|-------------------------------|-----------------------------------------------------------------------------------|

| DS2  | RUN                        | 1                             | on = microprocessor is running (card not in reset)                                |

| DS3  | ID                         | 1                             | blinking = card ID (identify) has been enabled from<br>CEC/IMC Manager (MOM PC) * |

| DS4  | CLKS                       | 4                             | on = all selected clocks are operational                                          |

| DS5  | SIG                        | 6                             | on = a T1/E1 line signal is being received                                        |

| DS6  | SYNC                       | 6                             | on = $T1/E1$ line frame sync is established                                       |

| DS7  | SEC                        | 9                             | on = card in secondary mode                                                       |

| DS8  | +5V                        | 10                            | on = $+5V$ power supply is present                                                |

| DS9  | +12V                       | 10                            | on = $+12V$ power supply is present                                               |

| DS10 | -12V                       | 10                            | on = $-12V$ power supply is present                                               |

Table 6 – Status Indicators

\* ID status indicator is also used to indicate proper board initialization at power-up.

# LBI-39107

| MTSC        | SCHEMATIC<br>IC            | MTSC CHIP                  |                            |                            |                            |                            |                            |                            |

|-------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| SIDE        | LABELING<br>(Sheets 3 & 4) | 1<br>(U41)                 | 2<br>(U42)                 | 3<br>(U43)                 | 4<br>(U44)                 | 5<br>(U45)                 | 6<br>(U46)                 | 7<br>(U47)                 |

| System      | SYSIN0                     | bus 0 in                   | bus 4 in                   | bus 8 in                   | bus 12 in                  | bus 16 in                  | bus 20 in                  | bus 24 in                  |

| System      | SYSIN1                     | bus 1 in                   | bus 5 in                   | bus 9 in                   | bus 13 in                  | bus 17 in                  | bus 21 in                  | bus 25 in                  |

| System      | SYSIN2                     | bus 2 in                   | bus 6 in                   | bus 10 in                  | bus 14 in                  | bus 18 in                  | bus 22 in                  | bus 26 in                  |

| System      | SYSIN3                     | bus 3 in                   | bus 7 in                   | bus 11 in                  | bus 15 in                  | bus 19 in                  | bus 23 in                  | bus 27 in                  |

| System      | SYSOUT0                    | bus 0 out                  | bus 4 out                  | bus 8 out                  | bus 12 out                 | bus 16 out                 | bus 20 out                 | bus 24 out                 |

| System      | SYSOUT1                    | bus 1 out                  | bus 5 out                  | bus 9 out                  | bus 13 out                 | bus 17 out                 | bus 21 out                 | bus 25 out                 |

| System      | SYSOUT2                    | bus 2 out                  | bus 6 out                  | bus 10 out                 | bus 14 out                 | bus 18 out                 | bus 22 out                 | bus 26 out                 |

| System      | SYSOUT3                    | bus 3 out                  | bus 7 out                  | bus 11 out                 | bus 15 out                 | bus 19 out                 | bus 23 out                 | bus 27 out                 |

| Synchronous | SYNCHIN0                   | from<br>framer             |

| Synchronous | SYNCHIN1                   | from gate<br>arrays 1 – 5  |

| Synchronous | SYNCHIN2                   | from<br>HSCX<br>controller |

| Synchronous | SYNCHIN3                   | from gate<br>array 6       |

| Synchronous | SYNCHOUT0                  | to MTSC 8<br>(U48)         |

| Synchronous | SYNCHOUT1                  | to gate<br>arrays 1 – 5    |

| Synchronous | SYNCHOUT2                  | to HSCX controller         |

| Synchronous | SYNCHOUT3                  | to gate<br>array 6         | to gate<br>array б         | to gate<br>array 6         |

Table 7 – MTSC 1 Thru 7 I/O Mapping (First Stage)

\* Gate arrays 1 thru 5 = U94 thru U98 respectively. Gate array 6 = U99.

# CIRCUIT ANALYSIS

| MTSC<br>SIDE | SCHEMATIC<br>U48 LABELING<br>(Sheet 4) | SOURCE/DESTINATION<br>OF SIGNAL    |

|--------------|----------------------------------------|------------------------------------|

| Input        | IN0                                    | from MTSC 1 (U41)                  |

| Input        | IN1                                    | from MTSC 2 (U42)                  |

| Input        | IN2                                    | from MTSC 3 (U43)                  |

| Input        | IN3                                    | from MTSC 4 (U44)                  |

| Input        | IN4                                    | from MTSC 5 (U45)                  |

| Input        | IN5                                    | from MTSC 6 (U46)                  |

| Input        | IN6                                    | from MTSC 7 (U47)                  |

| Input        | IN7                                    | from gate arrays 1 – 5 (U94 – U98) |

| Input        | IN8                                    | from HSCX controller (U33)         |

| Input        | IN9                                    | from gate array 6 (U99)            |

| Input        | IN10                                   | *                                  |

| Input        | IN11                                   | *                                  |

| Input        | IN12                                   | *                                  |

| Input        | IN13                                   | *                                  |

| Input        | IN14                                   | *                                  |

| Input        | IN15                                   | *                                  |

| Output       | OUT0                                   | to framer (FRAMER_PCM_IN)          |

| Output       | OUT1                                   | *                                  |

| Output       | OUT2                                   | *                                  |

| Output       | OUT3                                   | *                                  |

| Output       | OUT4                                   | *                                  |

| Output       | OUT5                                   | *                                  |

| Output       | OUT6                                   | *                                  |

| Output       | OUT7                                   | *                                  |

| * not used   |                                        | u]                                 |

#### Table 8 – MTSC 8 I/O Mapping (Second Stage)

In addition to TDM bus I/O on the MTSC system side, the first stage MTSC chips (U41 thru U47) provide transmit enables (!TE[0:27]) for the Futurebus drivers. These Futurebus drivers, located in the Futurebus transceiver chips, drive the CEC/IMC TDM buses on the Backplane. The enable lines are not indicated in Figure 3. Each enable line enables a driver when the respective MTSC system side output is valid and must be applied to the CEC/IMC TDM bus. Each system side output has a corresponding active-low transmit enable output. See the section entitled "**FUTUREBUS TRANSCEIVERS**", subsection "**TDM Bus Interfacing**" (page 20) for additional details.

For example, the BUS[0]\_TX output from U41 pin 43 (SYSOUT0) [schematic diagram sheet 3] is applied to the input of a driver in U73 (at U73 pin 3) [schematic diagram

sheet 5]. The transmit enable line for bus 0 is !TE[0] from U41 pin 5. !TE[0] is applied to bus 0 driver enable input at U73 pin 17 (via inverter U78B). The driver's output is U73 pin 18, identified TDM\_BUS[0]. It drives TDM bus 0 when !TE[0] is low. TDM\_BUS[0] is applied to the CEC/IMC Backplane via 96-pin DIN connector J1 pin 9B [schematic diagram sheet 10].

# **MTSC Connection Examples**

The following example connections through the MTSC chips are presented. Refer to Figure 3 and the schematic diagram as necessary [schematic diagram sheets 3 thru 5]:

- Connect T1/E1 channel 1 (receive line) to CEC/IMC Backplane TDM bus 5, slot 3 Since MTSC 2 (U42) has physical access to TDM bus 5, U42 is utilized:

- Connect: synchronous side SYNCHINO at U42 pin 19 (from T1/E1 framer via FRAMER\_PCM\_OUT) during slot 1 (slot 1 = T1/E1 channel 1). Buffer in "speech memory" within MTSC 2 and send

- to: system side SYSOUT1 at U42 pin 41 (to TDM bus 5 transceiver U74 via BUS[5]\_TX) during slot 3. During this connection, !TE(5) from U42 pin 8 will produce a low pulse for the TDM bus 5 driver in transceiver U74.

- Connect TDM bus 13, slot 4 to T1/E1 channel 1 (transmit line) – Since MTSC 4 (U44) has physical access to TDM bus 13, U44 is utilized:

- Connect: system side SYSIN1 at U44 pin 7 (from TDM bus 13 via BUS[13]\_RX and Futurebus transceiver U73) during slot 4. Buffer in "speech memory" within MTSC 4 and send

- to: synchronous side SYNCHOUT0 at U44 pin 42 (to MTSC 8 via MTSC4\_OUT) during slot 1 of the next frame (slot 1 = T1/E1 channel 1).

MTSC 8 (U48) must also be involved in the connection to route the data to the T1/E1 framer (U85):

- Connect: IN3 at U48 pin 20 (from MTSC 4 via MTSC4\_OUT) during slot 1

- to: OUT0 at U48 pin 43 (to T1/E1 framer via FRAMER\_PCM\_IN) during slot 1.

#### Microprocessor Interface

Each memory time switch is connected to the lower eight bits of the data bus, D[1] thru D7]. Via this bus, microprocessor U1 sends both configuration data and switch memory connection data to each MTSC chip.

All MTSC chips are located in microprocessor U1's address space selected by the active-low !MCS3 chip select line from U1 pin 35 [schematic diagram sheet 1]. All OR gates within U28 & U29 and inverters within U5 & U31 [schematic diagram sheet 2] gate !MCS3 with address lines A[4] thru A[11]. The resultant active-low !MTSC1\_CS thru !MTSC8\_CS chip selects are applied to MTSC 1 (U41) thru MTSC 8 (U48) respectively, at pin 22 of each MTSC chip.

Before application to the MTSC chips, the active-low read (!RD) and write (!WR) lines from microprocessor U1 are each gated with the active-low !RESET line via AND gates U12C and U12D [schematic diagram sheet 3]. This gating provides a hardware reset to all MTSC chips by simultaneously pulling the read and write inputs of each MTSC low during a card reset (when !RESET = low). The resultant gated active-low read (!RD\_MTSC) and write (!WR\_MTSC) lines are applied to MTSC chips U41 thru U48 at pins 24 and 25 of each MTSC chip [schematic diagram sheets 3 and 4].

# **Clock Inputs**

The MTSC chips require two (2) system clock input signals. MTSC\_FSYNC at pin 3 of each MTSC is an 8 kHz frame sync clock derived from the selected frame sync clock source – either the CEC/IMC Clock Board A or B frame sync clock. 4096KHZ at pin 44 of each MTSC is a 4.096 MHz clock from a PLL circuit locked to the selected bit clock (2.048 MHz). Clock source selection is dependent upon current card clock operating mode. See the clock generation section of this manual for additional details [schematic diagram sheets 3 and 4].

Monostable multivibrator U11B provides a frame sync clock pulse to the all of the memory time switches [schematic diagram sheet 4]. The falling-edge of the selected FSYNC clock pulses triggers U11B's active-low trigger input (U11 pin 9) every 125 microseconds (8 kHz). The monostable's output at U11 pin 5 is set to approximately 110 nanoseconds by the RC network at pin 7. This active-high output pulse is applied to pin 3 of each MTSC chip via MTSC\_FSYNC. Basically, this circuit supplies a slightly modified frame sync pulse to the MTSC chips.

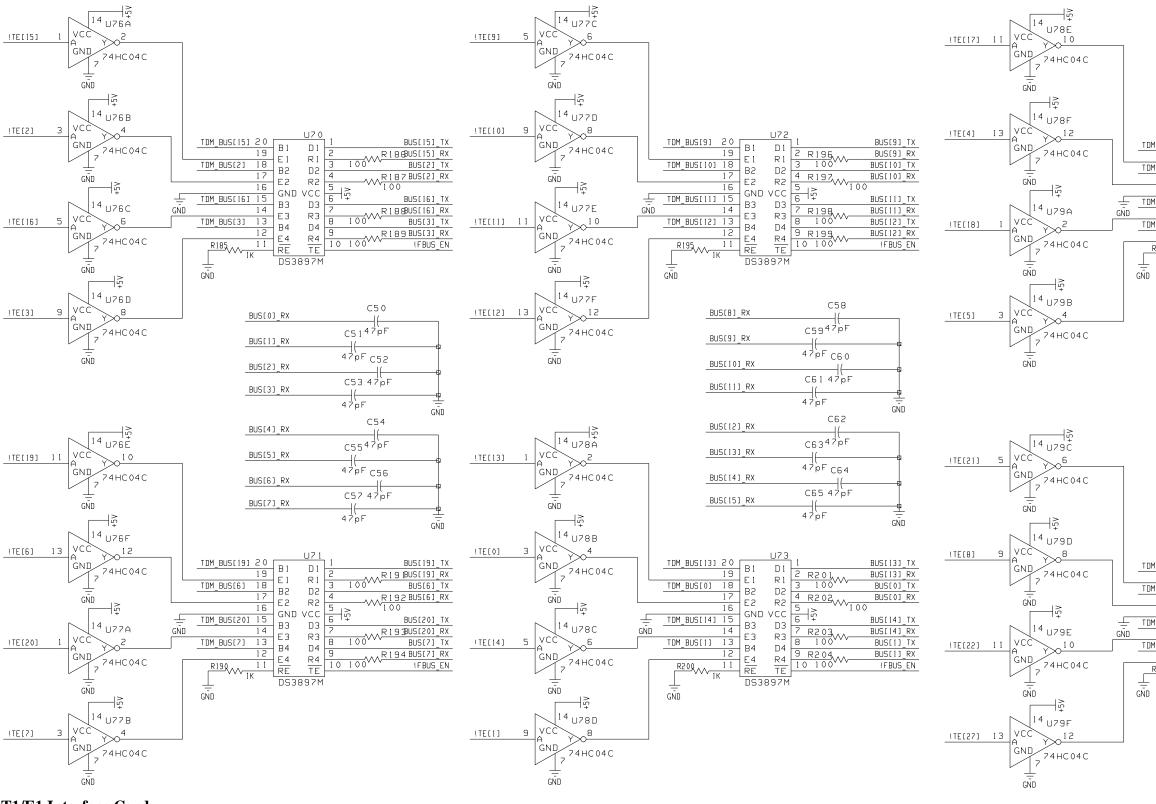

#### **FUTUREBUS TRANSCEIVERS**

All TDM bus and clock lines on the CEC/IMC Backplane utilize IEEE-896 Futurebus-compatible logic lines. This interface defines a logic high state at (or near) +2 volts and a logic low state at (or near) +1 volt. On the Futurebus side, drivers within the Futurebus transceiver chips have open-collector outputs. Individual pull-up resistors on the CEC/IMC Terminator Boards pull each respective Futurebus line to an approximate +2-volt level when the line is high (driver off).

The primary purpose of the Futurebus transceivers is to perform Futurebus-to-TTL level conversions between the CEC/IMC Backplane and the TTL-level chips on the T1/E1 Interface Card. The transceivers used for TDM bus interfacing also split the Backplane TDM buses into separate receive (RX) and transmit (TX) TDM bus lines on the T1/E1 Interface Card. These separated buses operate at TTL levels.

## **TDM Bus Interfacing**

Integrated circuits U50 and U70 thru U75 are National Semiconductor DS3897M (or equivalent) quad Futurebus transceivers – four (4) transceivers are in each IC package [schematic diagram sheets 4 and 5]. These transceivers interface the Futurebus-level TDM buses on the CEC/IMC Backplane to the T1/E1 Interface Card's MTSC chips. The MTSC chips operate at TTL levels.

On the Futurebus transceiver's Backplane-side, bus lines TDM\_BUS[0] thru TDM\_BUS[27] correspond to TDM buses 0 thru 27 on the CEC/IMC Backplane. Connections are made via 96-pin DIN connectors J1 and J2 at the rear of the card [schematic diagram sheet 10].

#### - NOTE -

CEC/IMC Audio Boards utilize buses 0 thru 7 only. Initial T1/E1 Interface Card firmware/software will comply with this temporary limitation.

TTL-level TDM bus signals are transferred *from* the MTSC chips *to* the Futurebus transceivers' drivers via the BUS[0]\_TX thru BUS[27]\_TX bus lines. Likewise, TTL-level TDM bus signals are transferred *from* the Futurebus transceivers *to* the MTSC chips via the BUS[0]\_RX thru BUS[27]\_RX lines. Each RX line is equipped with a small low-pass RC network between the transceiver and the MTSC chip's input [schematic diagram sheets 3, 4 and 5].

Transmit/receive mode of each individual transceiver is controlled by the active-low transmit-enable outputs from

the MTSC chips. These enables are identified !TE[0] thru !TE[27]. A transceiver drives its TDM Futurebus line when the respective !TE[x] enable is low and its logic input is high. These active-low transmit-enable outputs are inverted before application to the transceivers' active-high transmit-enable inputs.

For example, when !TE[3] from U41 pin 12 is low [schematic diagram sheet 3], the transceiver within U70 for bus 3 [schematic diagram sheet 5] drives TDM\_BUS[3] (U70 pin 13 and J1 pin 15B) at the inverse BUS\_TX[3] logic state. Inverter U76D inverts the !TE[3] transmitenable [schematic diagram sheet 5].

A master Futurebus driver enable/disable control line, !FBUS\_EN from data flip-flop U51A [schematic diagram sheet 4], is applied to the master transmit-enable input at each TDM Futurebus transceiver (pin 10 at U50 and U70 thru U75). When !FBUS\_EN is high, all drivers within the TDM Futurebus transceivers are disabled. The drivers are disabled at power-up and they remain disabled until an enable command is received via a parallel I/O control sequence from the Controller Board.

Flip-flop U51A controls the state of !FBUS\_EN via its active-low output at U51A pin 6. LD[0] and CF[6] from parallel I/O data latches U113 and U114 [schematic diagram sheet 9] provide the data and clock inputs to the flip-flop at U51A pins 2 and 3 respectively. The interface module's active Controller Board has direct control of LD[0] and CF[6] via the parallel I/O control connections between it and the T1/E1 Interface Card. See the section entitled "**PARALLEL I/O CONTROL**" (page 33) for complete details on the parallel I/O control lines and specific parallel I/O control sequences.

If the T1/E1 Interface Card enters a secondary or reset state (PRI/!SEC from U111B = low or !RESET from U120D = low), AND gate U65A drives U51A's clear input low. As a result, !FBUS\_EN transitions high and all TDM bus-related Futurebus transceivers' drivers are disabled. This prevents the card from interfering with the Backplane's TDM buses when it is in a secondary or a reset state. Also, the !RESET input to the AND gate insures the flip-flop initializes correctly at power-up so the drivers are disabled.

During card testing, the transceivers' drivers may be manually enabled by setting DIP switch SW1 position 3 "CLOSED" or "ON". This setting pulls the flip-flop's active-low preset input low via the !FBUS\_DRV\_EN line from the DIP switch [schematic diagram sheets 1 and 4]. Thus, as long as the card is in primary mode (PRI/!SEC = high) and not reset (!RESET = high), !FBUS\_EN is in its active state – logic low – and the drivers are master enabled. This control (manual enabling) should only be exercised during troubleshooting procedures.

# **Clock Inputs**

Clock pulses on the CEC/IMC Backplane generated by the Clock Board are applied to Futurebus transceiver U60 via 96-pin DIN connectors J1 and J2 [schematic diagram sheets 4 and 10]. Transceiver U60 is a National Semiconductor DS3896M (or equivalent) octal Futurebus transceiver hard-wired for receive mode operation only; its transmit/receive control input  $(T/\overline{R})$  at U60 pin 11 is tied to ground. The B-side pins (driver outputs/receiver inputs) are the Futurebus-level clock inputs from the Backplane. Pull-up resistors R158 thru R165, located on the TTL-level side (output) of U60, insure these clock pulses drive the CMOS inputs of U53 and U54 properly.

See the section entitled "CLOCK SELECTION AND GENERATION" for additional details on the clocks and the clock selection circuitry following U60.

# **Clock Outputs**

Transceiver U87 is a quad Futurebus transceiver identical to the transceivers used for TDM bus interfacing. Only the driver portion of two (2) transceivers in this chip are utilized [schematic diagram sheet 6].

The 8 kHz reference clock pulses from framer U85 pin 7 (8KHZ\_REF) feed inverter U15C. This inverter's output clocks both drivers' inputs – U87 pins 1 and 3. When enabled by an active-low !PRIMARY from data flip-flop U111B [schematic diagram sheet 9] *and* an active-high SYNCx\_EN line (x = A or B) from octal latch U9 [schematic diagram sheet 1], each Futurebus driver clocks its respective 8KHZ\_SYNCx Futurebus output to the CEC/IMC Backplane. The 8KHZ\_SYNCA clock is applied to the Backplane via 96-pin DIN connector J2 (bottom DIN connector) pin 4A and the redundant 8KHZ\_SYNCB clock is applied to the Backplane via J1 (top DIN connector) pin 27B [schematic diagram sheet 10]. Additional details on this circuitry are contained the section entitled "T1/E1 LINE FRAMER AND LINE INTERFACE" (page 25).

# **CLOCK SELECTION AND GENERATION**

To provide redundant clocking for the TDM bus and T1/E1 circuits, the CEC/IMC is equipped two (2) identical but completely separate clock circuits. These redundant system clocks, generated by the CEC/IMC Clock Board(s), are identified "A" and "B" throughout the system. Clock A/B selection is dictated by the CEC/IMC MOM Controller Board in accordance with clock A/B fail messages received from other CEC/IMC interface modules (MIM, CIM, NIM, LRIM, etc.) The initial start-up or default clock is B.

For example, if the CEC/IMC is operating off the B clock circuits and one or more of the B clock pulses on the

Backplane fail, the MOM Controller Board will receive clock B fail messages from most or all CEC/IMC interface modules within the CEC/IMC. The MOM Controller Board will then command all CEC/IMC interface modules to switch to the A clock circuit by sending an A clock-select message to all other Controller Boards in the CEC/IMC. Each Controller Board then switches its Audio Board(s) or its T1/E1 Interface Card(s) to the A clock circuits via parallel I/O control connections. Refer to LBI-38938 for additional information.

Redundant clocks originating from a CEC/IMC Clock Board and utilized by the T1/E1 Interface Card include the 8 kHz frame sync clock (FSYNCA and FSYNCB), the 2.048 MHz bit clock (BIT\_CLKA and BIT\_CLKB), and the 1.544 MHz T1 clock (1544A and 1544B). Two (2) other system clocks *not* utilized by the T1/E1 Interface Card but required by the CEC/IMC Audio Boards include a 256 kHz slot sync clock and a 2174/2175 Hz function tone clock. The 1.544 MHz clock is not used by the Audio Boards but it is required for T1 operation. All clocks are transferred over the Backplane at Futurebus levels. Table 9 summarizes clock usage by the T1/E1 Interface Card and an Audio Board.

Table 9 – Clock Utilization (System Clock Mode)

| FREQ.<br>FROM<br>CLOCK<br>BOARD | CLOCK<br>LINE<br>NAME<br>* | USED BY<br>T1/E1<br>INTERFACE<br>CARD | USED<br>BY<br>AUDIO<br>BOARD |

|---------------------------------|----------------------------|---------------------------------------|------------------------------|