### STATION CONTROL MODULE

MODEL TLN2423 A

#### 1. GENERAL DESCRIPTION

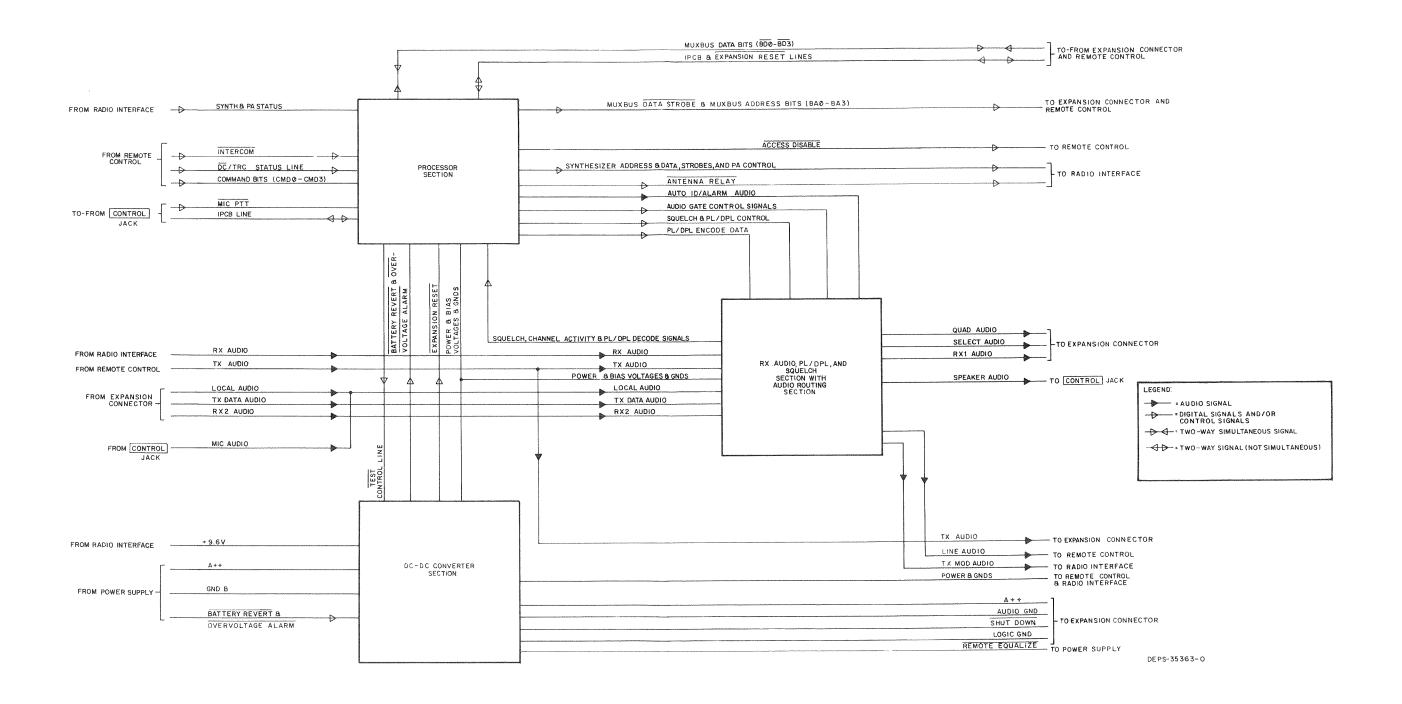

The TLN2423A Station Control Module directly controls most major functional blocks of the station. The module consists of the following items:

- TFN6045A PL Filter Hybrid

- TRN4372A Analog-to-Digital Hybrid

- TRN5195A PL/DPL Station Control Board

- TRN5196A PL/DPL Station Program EPROM

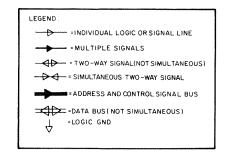

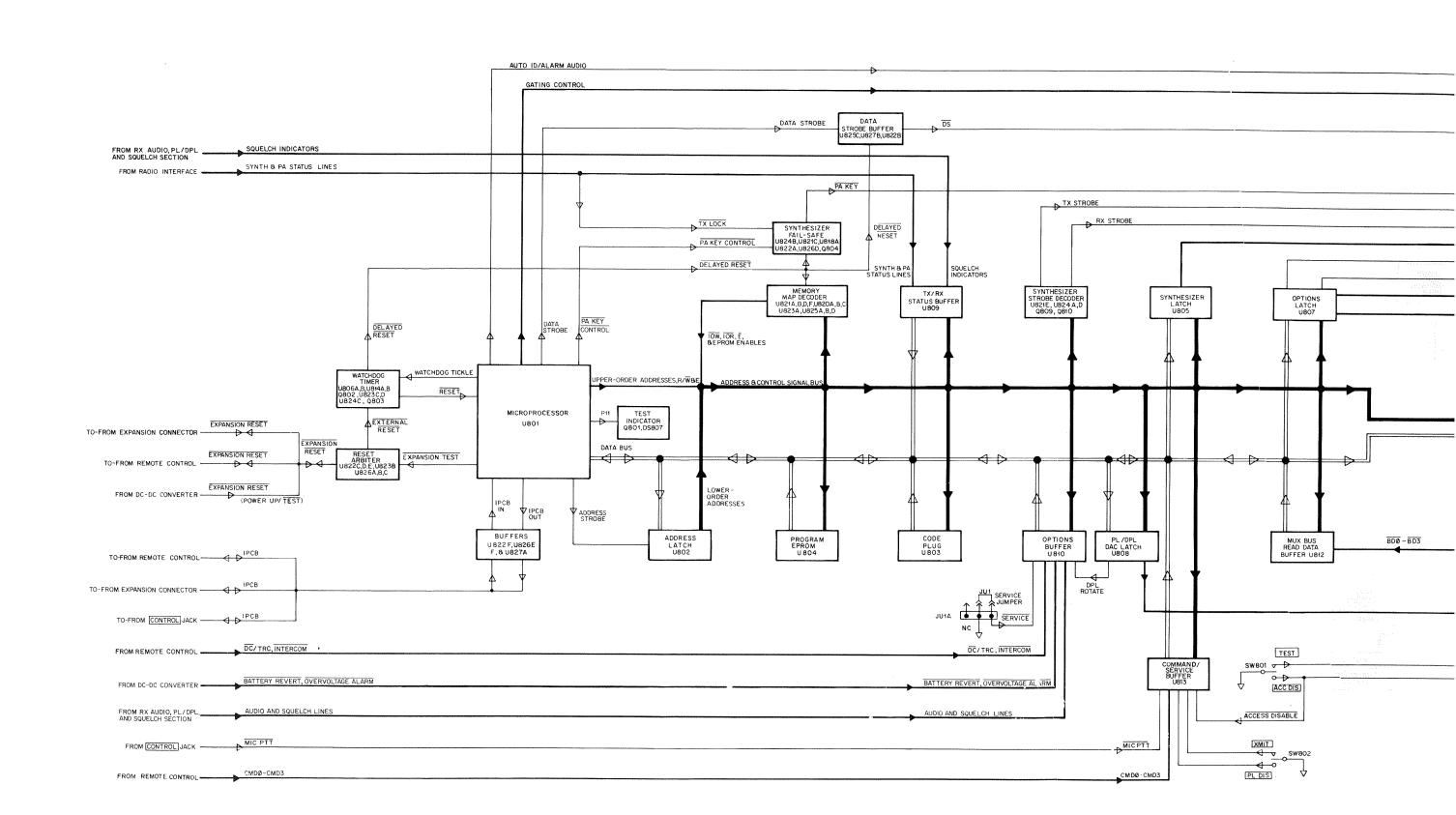

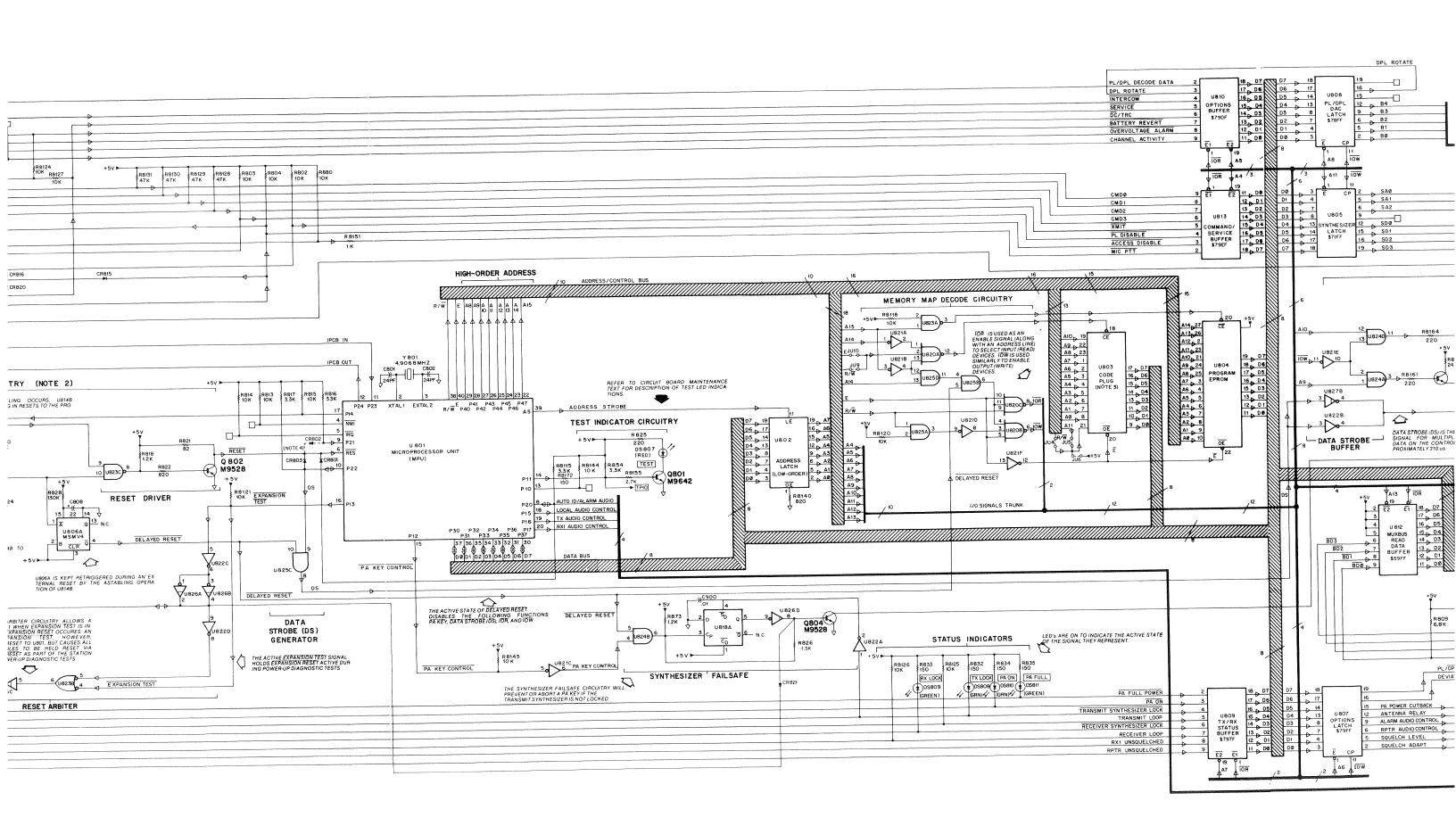

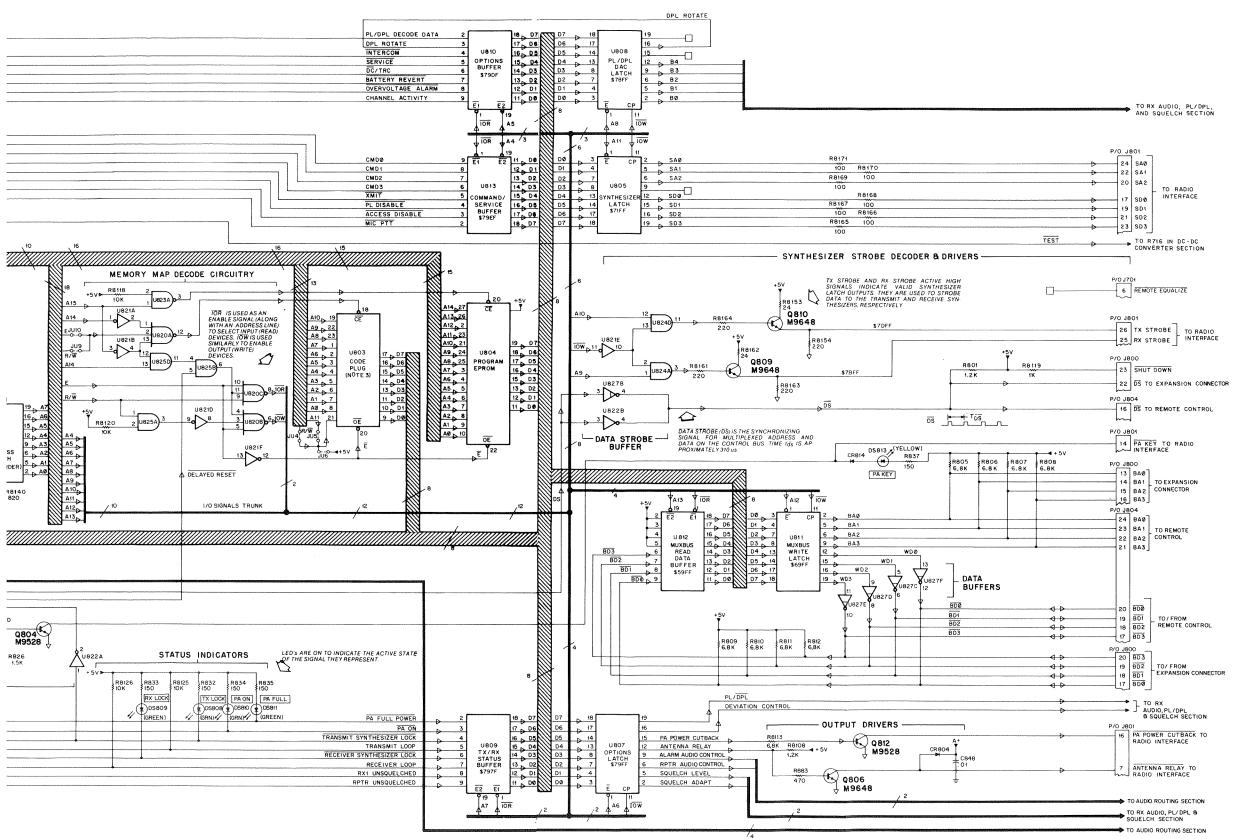

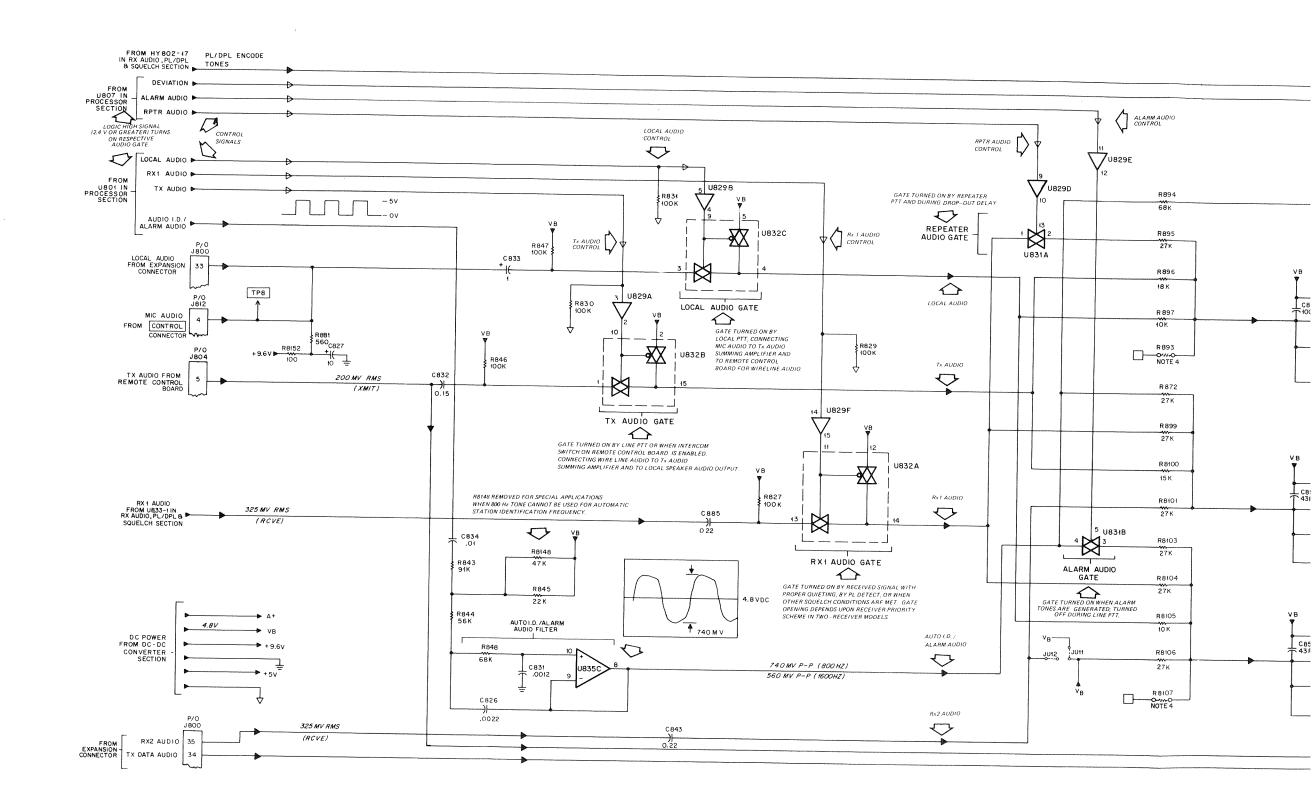

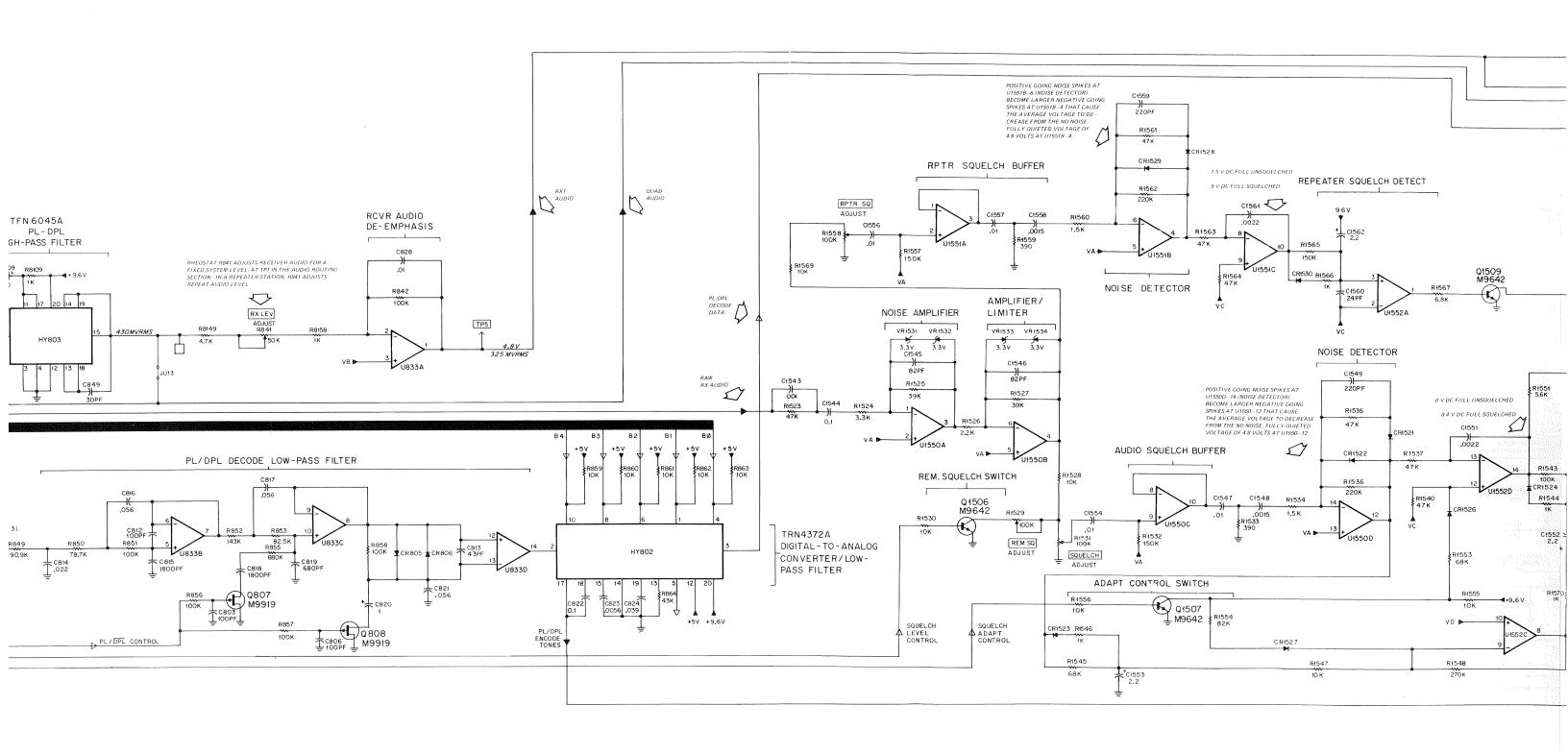

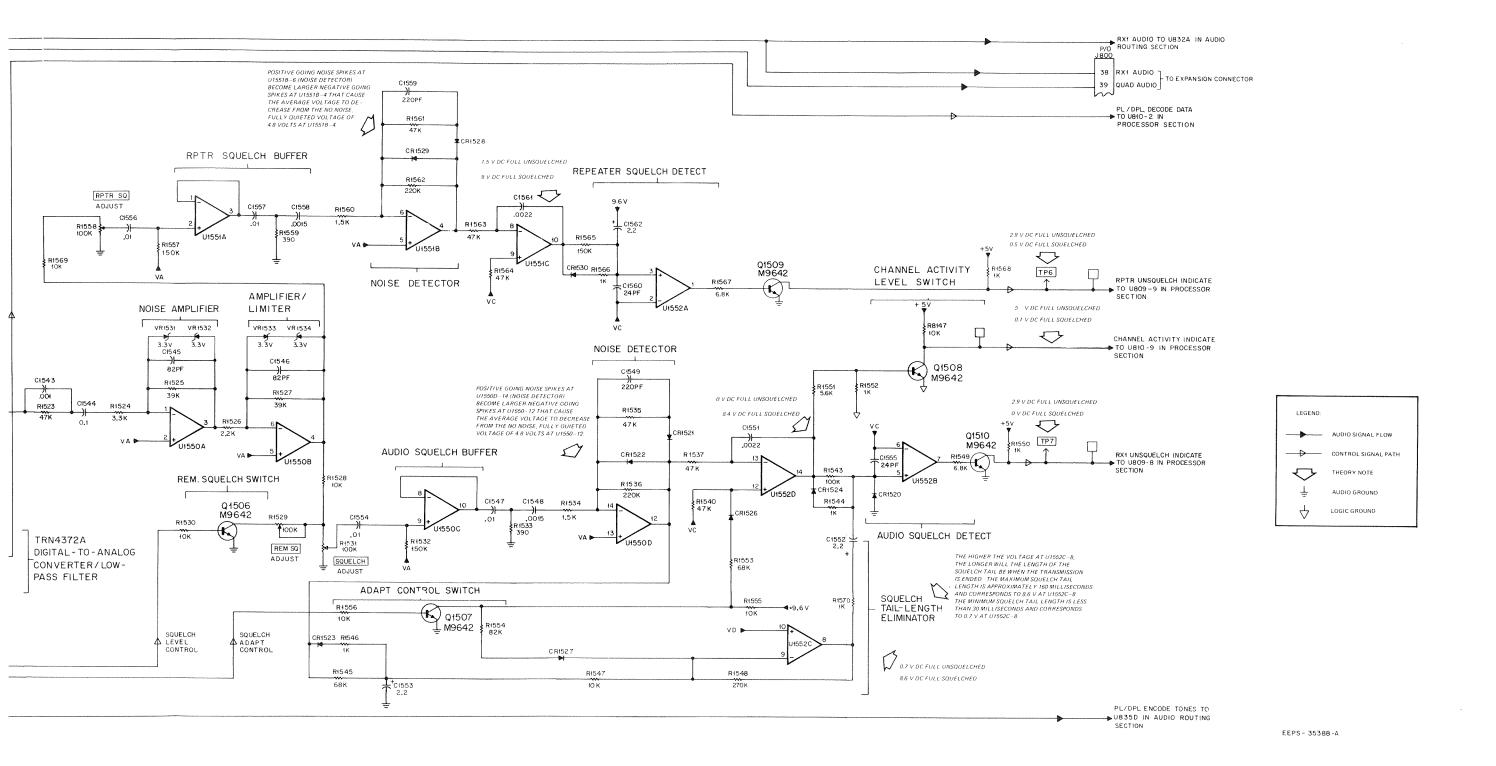

The station control board (see overall block diagram at end of this section) can be functionally divided into four sections:

- DC-DC Converter section.

- Processor section.

- Receiver Audio, PL/DPL, and Squelch section.

- Audio Routing/Control section.

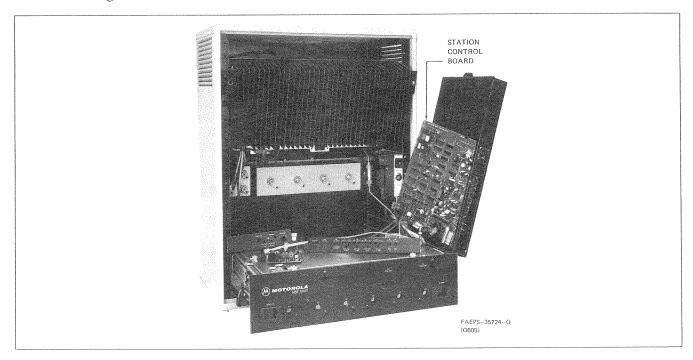

The dc-dc converter section essentially functions alone. That is, it is the source of the regulated +5 V used within the station plus the bias voltages required by the audio/squelch circuits. Other than these voltages, its only functional operation is to provide the power-up RESET signal, which is used to initialize the entire station during initial turn-on, or during a reset turn-on after loss of any of the three station operating voltages (+5 V, +9.6 V, or A+). The receiver audio, PL/DPL, and squelch section together with the audio/routing control section process all audio and provide all squelching used within the station. The processor section controls operation of the complete station, properly sequencing operations in a timely manner so that both transmission and reception is performed with the specified parameters. As shown in Figure 1, the station control board is located within (fastened to the underside of) the Control Tray which is mounted above the RF Trav.

Figuere 1. Location of TRN5195A Station Control Board

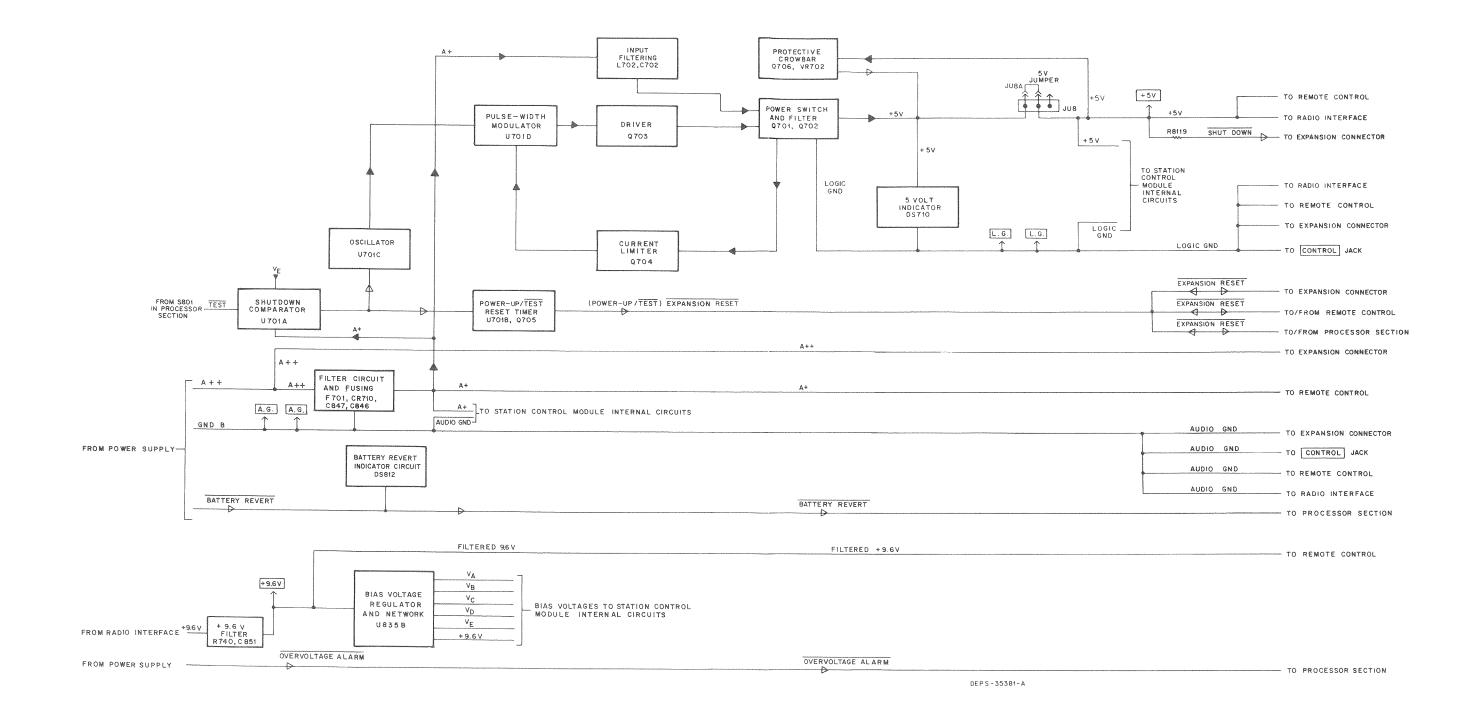

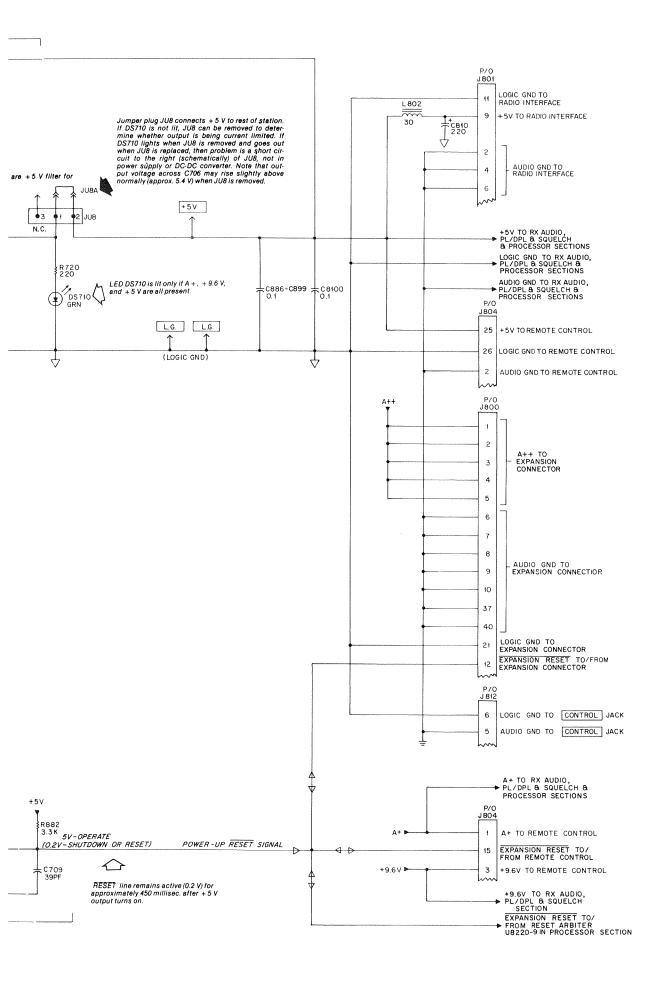

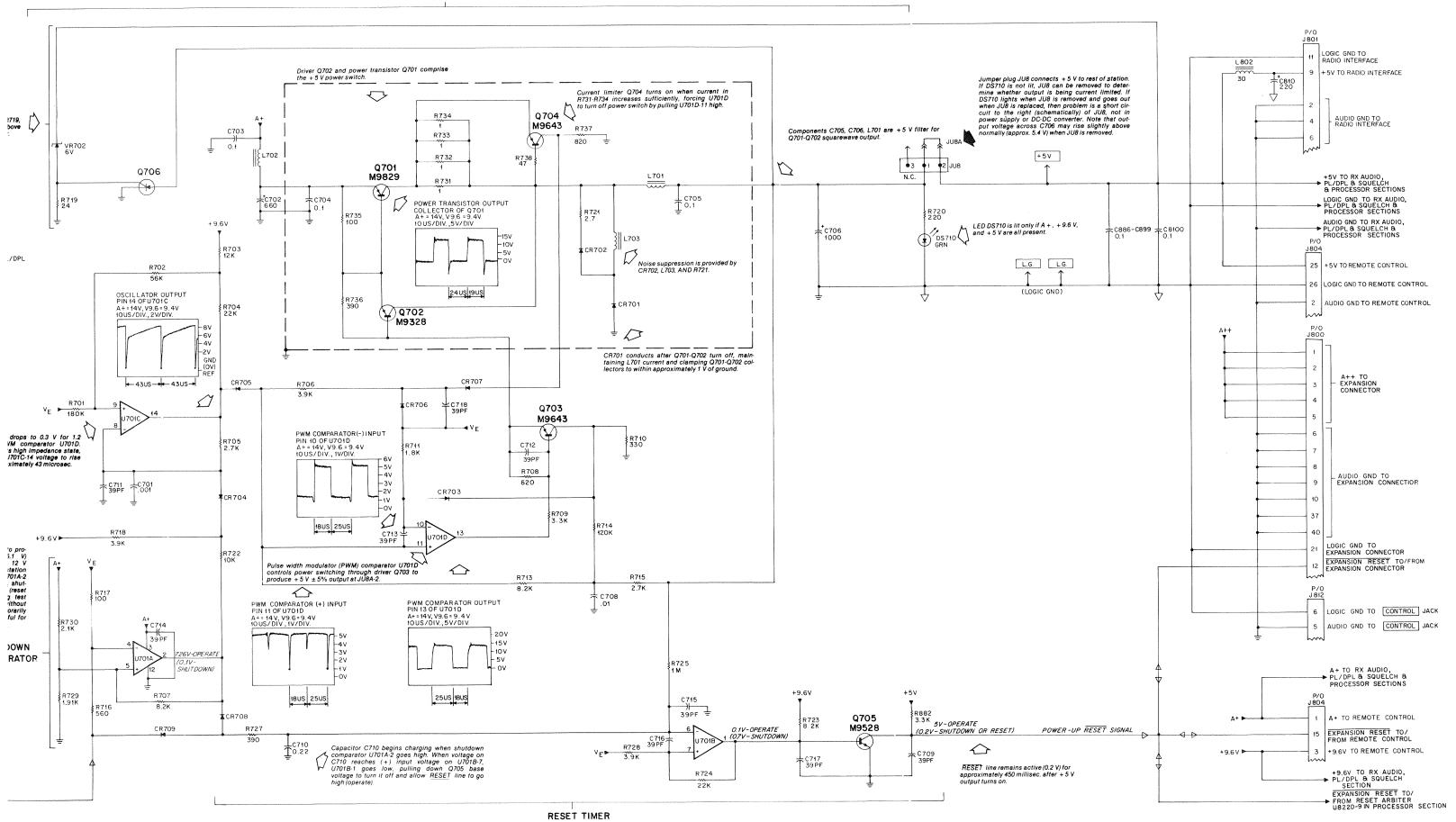

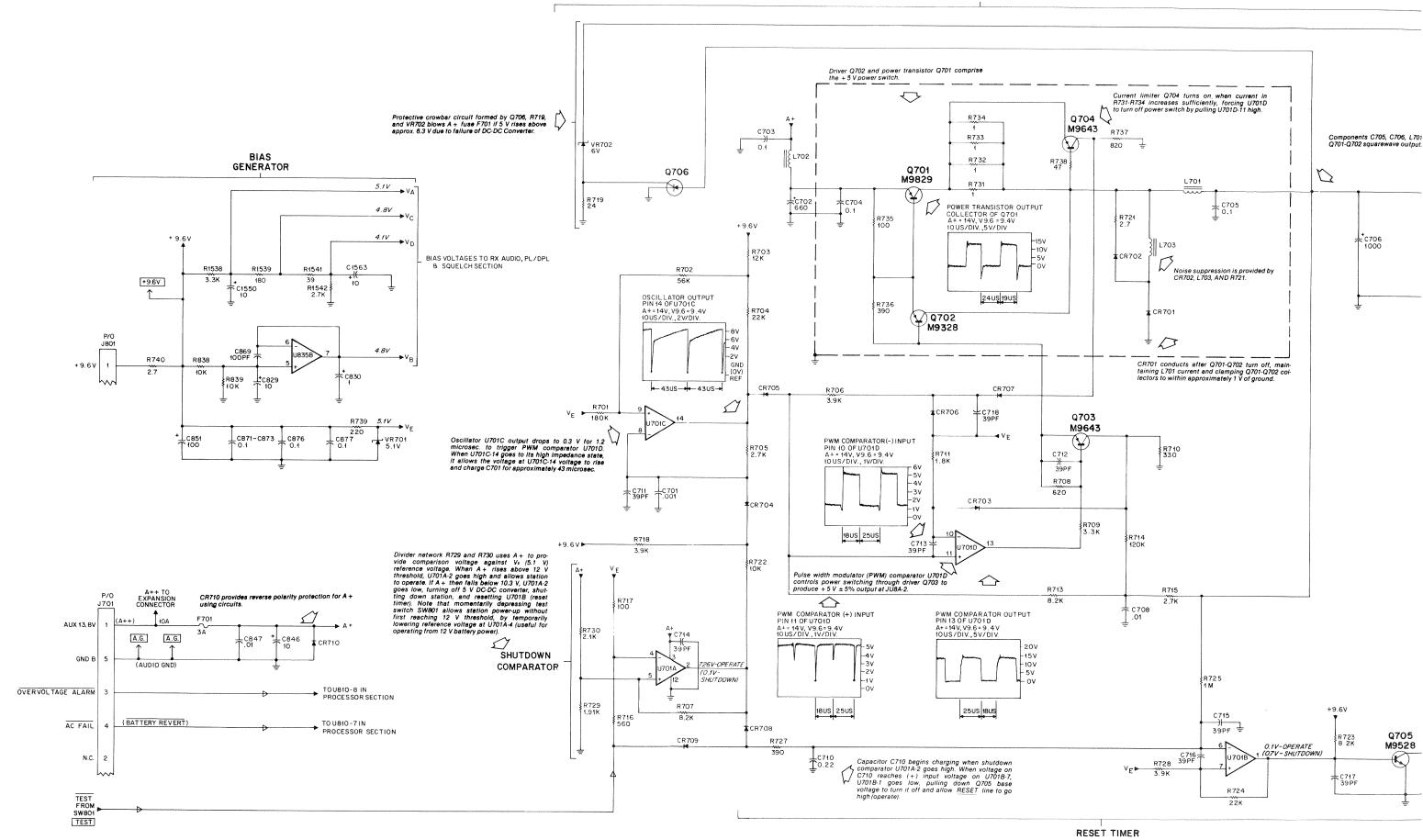

#### 1.1 DC-DC CONVERTER SECTION

The dc-dc converter section (see block diagram at the end of this section) of the station control board provides the bias voltages for the various audio and squelch circuits on the station control module, and produces the filtered and regulated +5 V used within the station. The dc-dc converter also provides routing, fusing, and some filtering for the A + from the power supply, internally routing A + to the processor section and the audio and squelch control sections and externally routing A + to the remote control board and expansion connector. The dc-dc converter additionally contains a power-up  $\overline{\text{RESET}}$  circuit that provides a system initialization reset signal to the station.

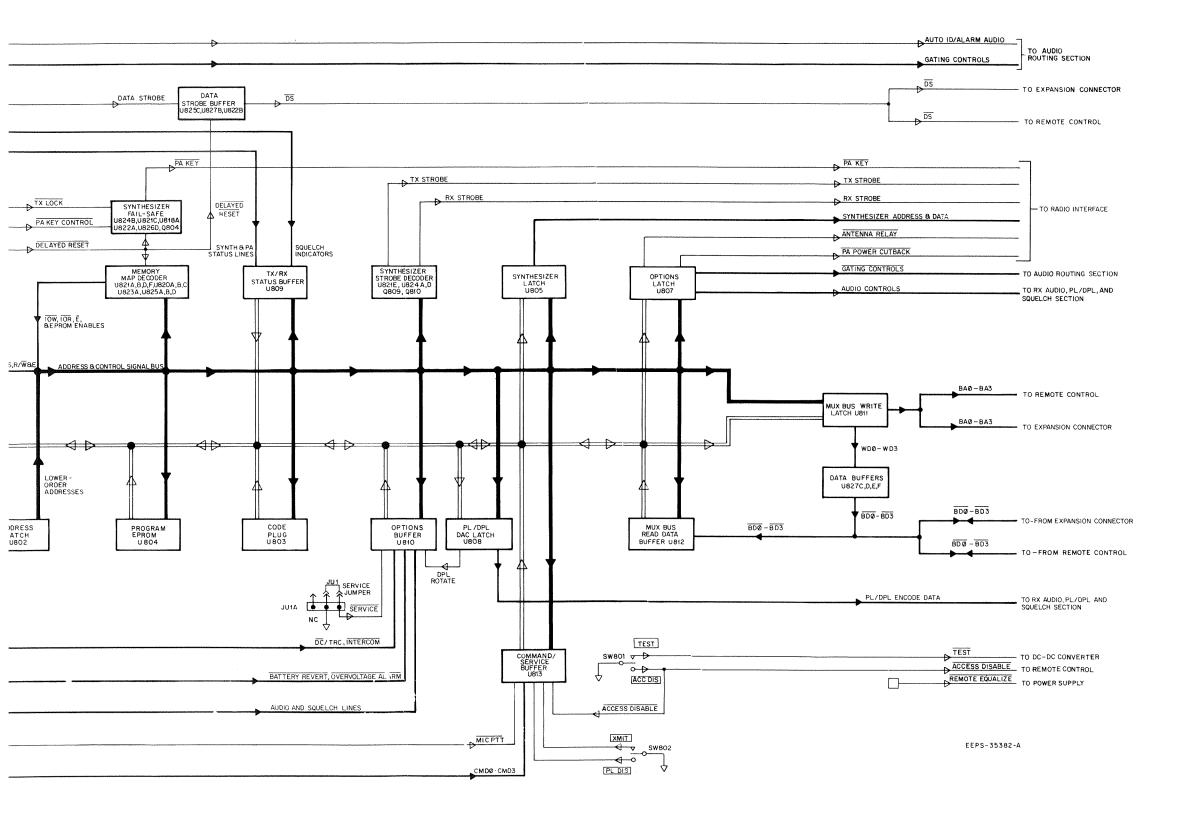

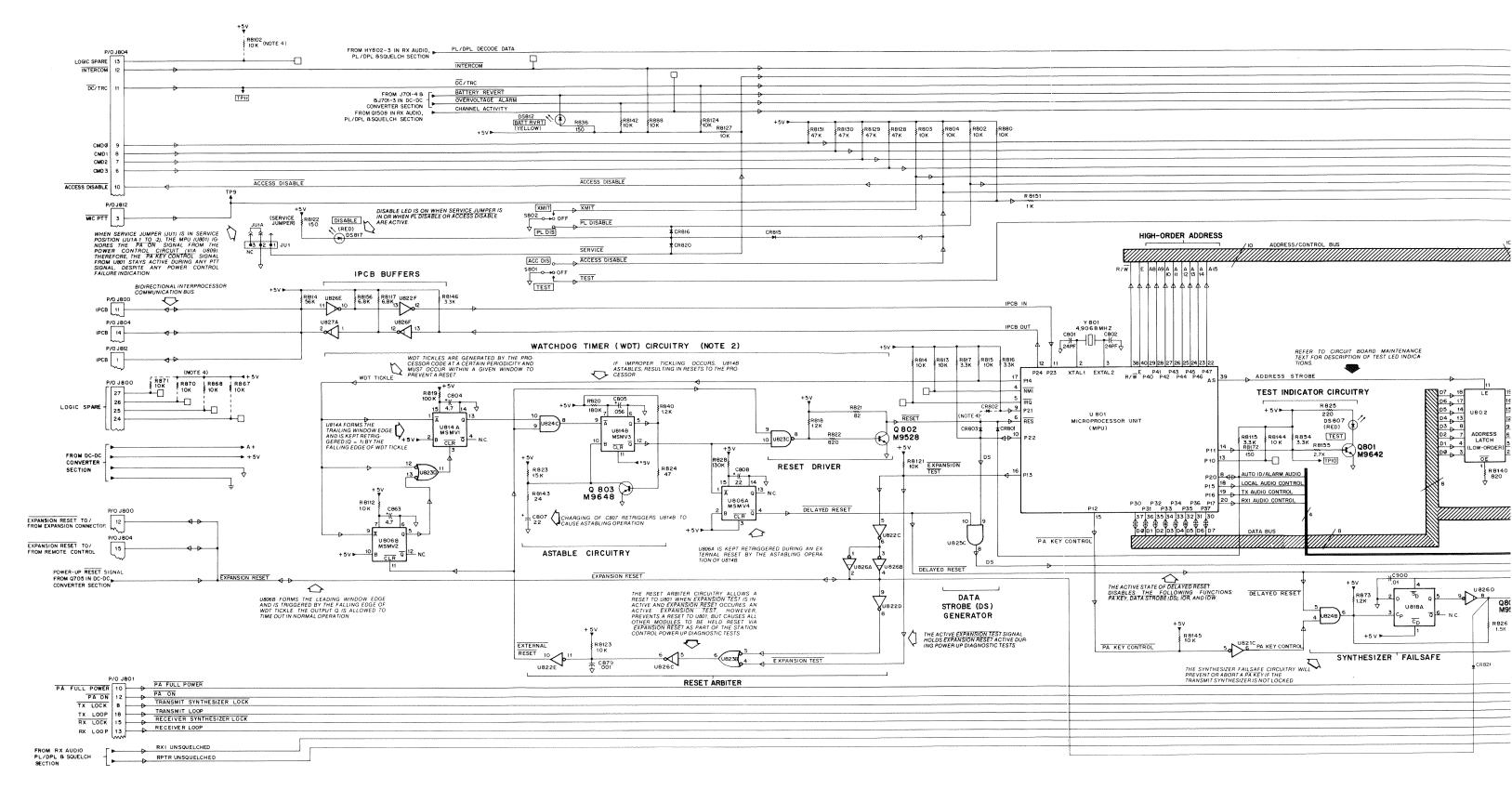

#### 1.2 PROCESSOR SECTION

The processor section (see block diagram at the end of this section) of the station control board controls all major radio functions of a station on a per-channel basis, including transmit and receive frequencies and switching, PL/DPL encode and decode, time-out timers, dropout and push-to-talk delays, automatic station identification (auto ID), alarm monitoring and generating, and squelch gating/repeater key-up conditions. The heart of the control function is a Motorola MC6803 Microprocessor Unit (MPU) that uses a preprogrammed erasable, programmable memory (EPROM) and a personality code plug, both of which combine to provide the exact operating program and parameters for a particular station. Proper sequencing of the various controlling operations from the MPU is supervised by the watchdog timer circuitry, which resets the MPU if its timing should falter (either too early or too late). The various latches and buffers within the processor section route status and control signals to the MPU, and command and control signals to the other portions of the station, or to external optional equipment.

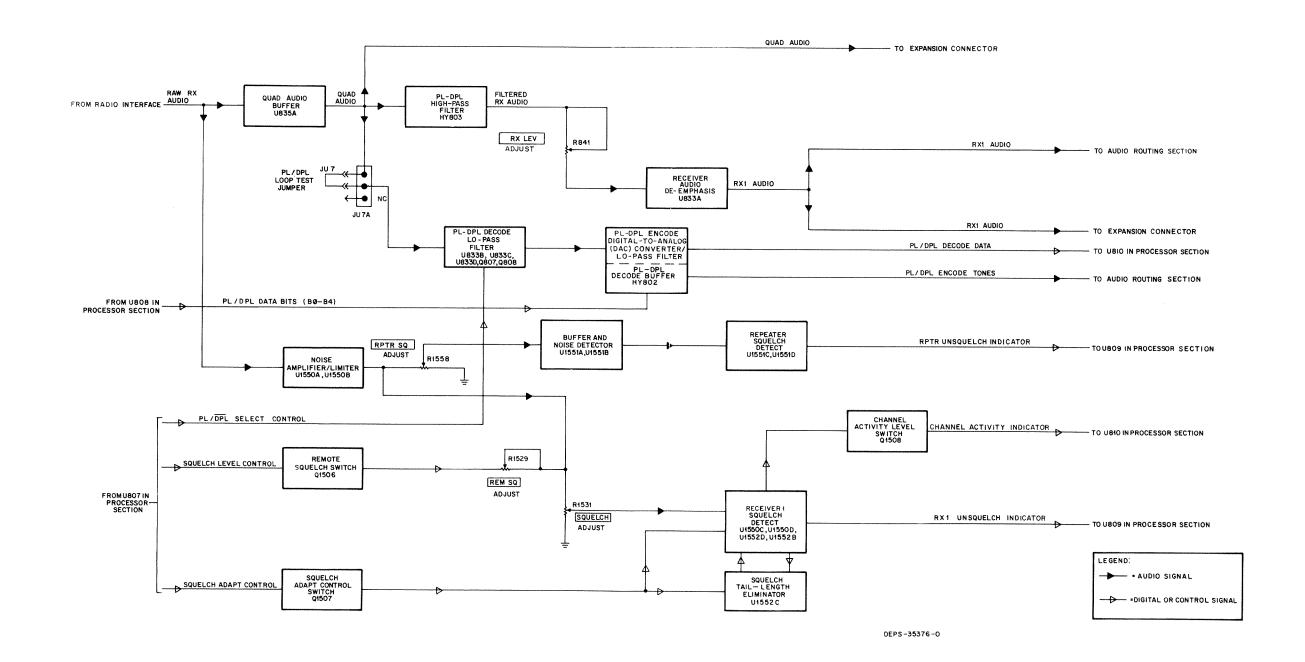

### 1.3 RECEIVER AUDIO, PL/DPL, AND SQUELCH SECTION

The Receiver Audio, *Private-Line/Digital Private-Line* (PL/DPL), and Squelch section (see block diagram at the end of this section) of the station control board processes the detected raw receiver audio from the i-f amplifier section of the uniboard. The processing includes separation and detection of received PL-DPL data, filtering and de-emphasis of receiver audio, and detection of both repeater (if used) and receiver 1 squelch. When used, the remote squelch control option is also located in this section. The PL-DPL portion of this section is also capable of accepting commands from the processor section to produce PL or DPL encoding tones (or codes) for encryption of the selected *Private-Line* tone (or code) during transmission.

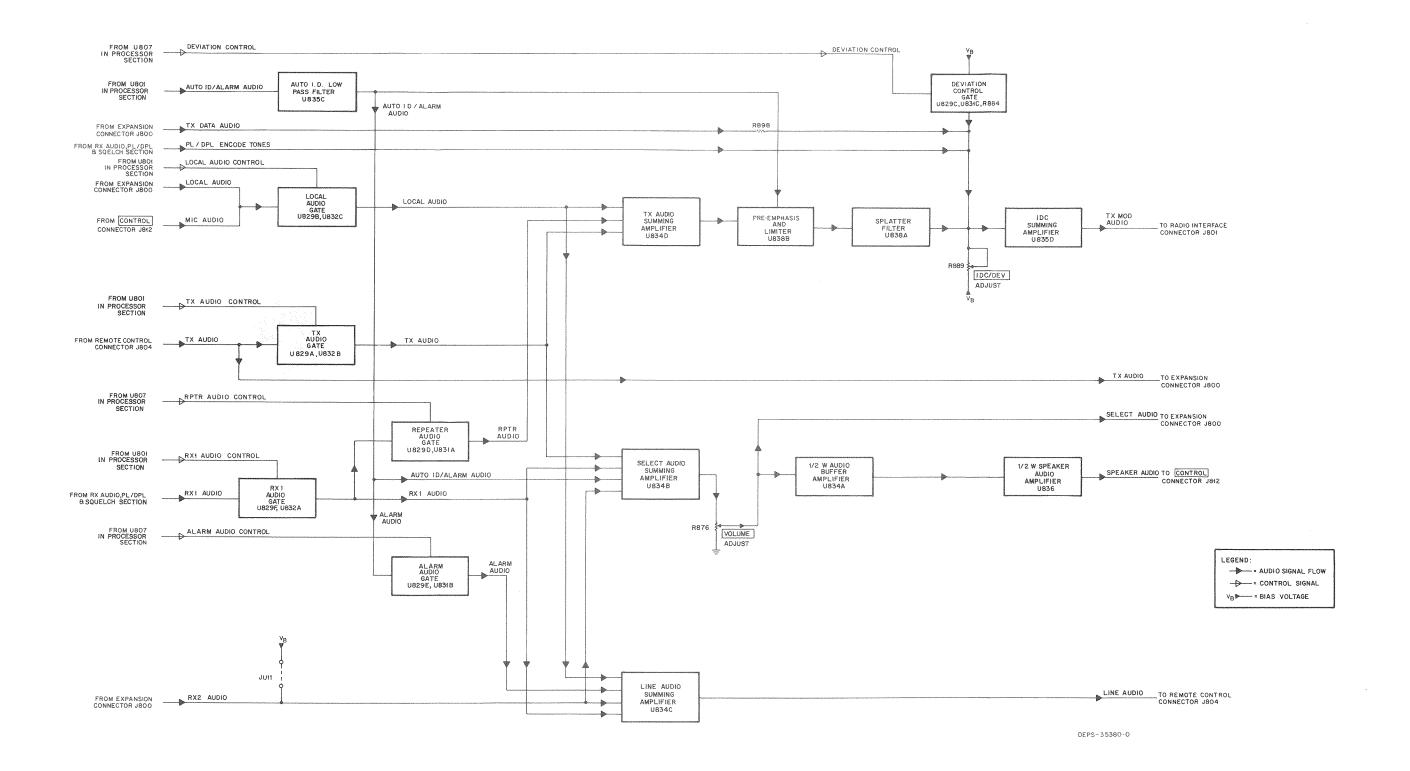

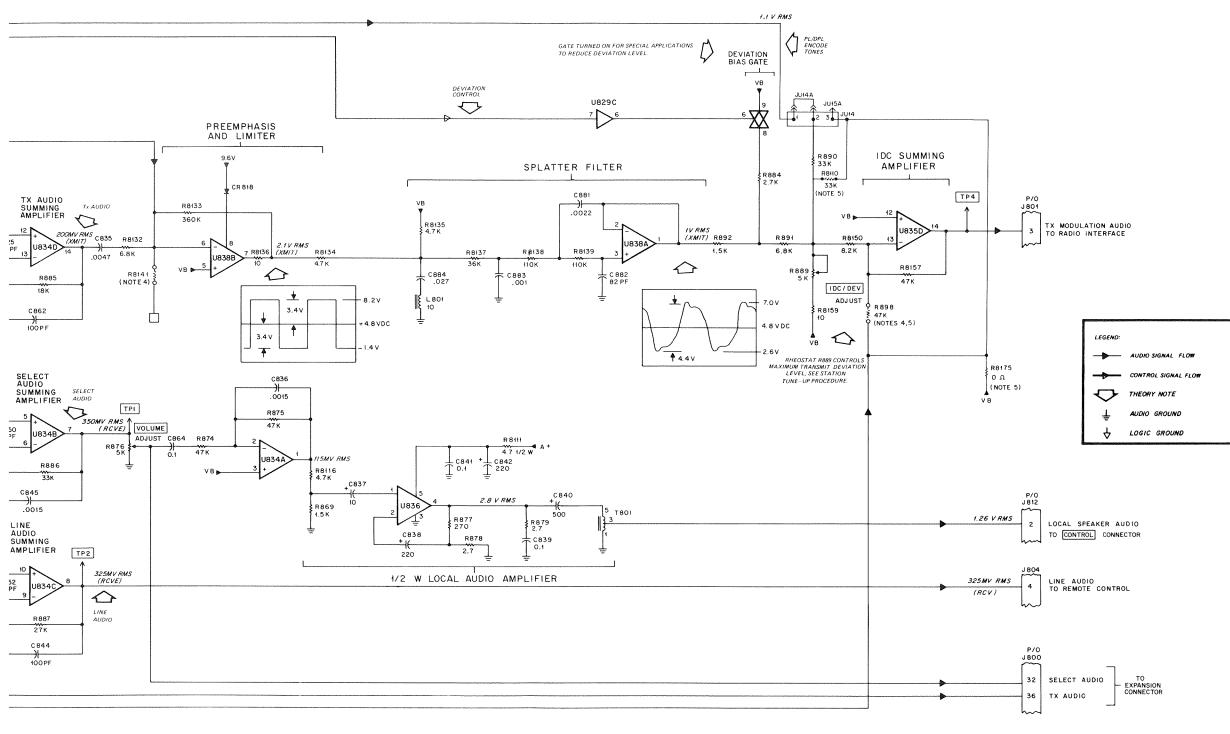

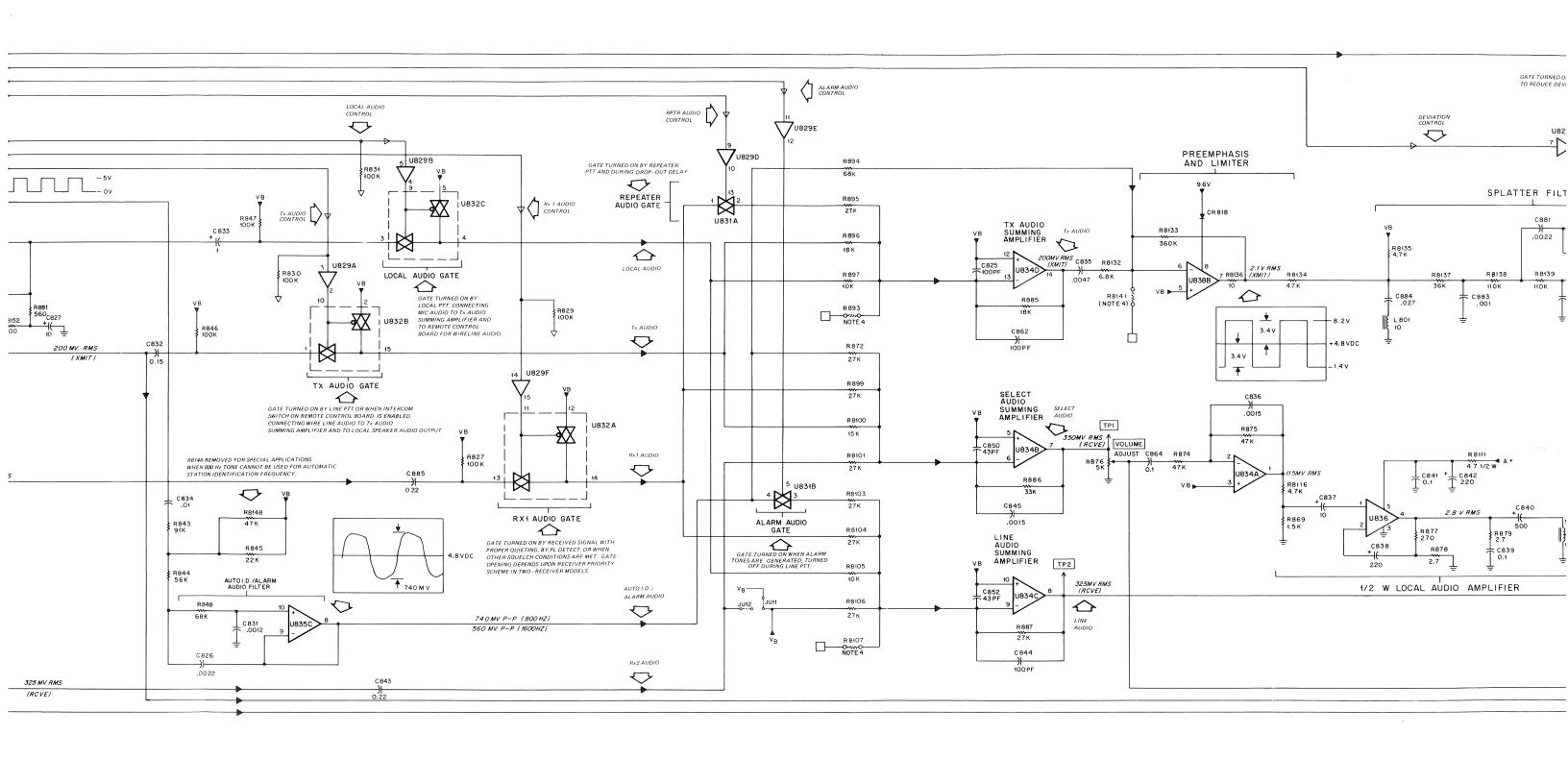

#### 1.4 AUDIO ROUTING/CONTROL SECTION

The audio routing/control section (see block diagram at the end of this section) of the station control

board provides routing for all audio within a station. This includes pre-emphasis and deviation control limitation for transmitter modulation audio, summing and amplification for local speaker audio (including a 1/2 watt audio driver), and summing and amplification for line audio. Summation of audio inputs for the three audio outputs is controlled via analog gate switches, except for the second receiver audio (if used) from the expansion connector.

### 2. DC-DC CONVERTER SECTION THEORY OF OPERATION

#### 2.1 GENERAL

The dc-dc converter section (see schematic at the end of this section) converts the auxiliary 13.8 V input into the filtered and regulated +5 V required by the station by using a controlled pulse-width modulator (PWM). The bias voltages used by the audio/squelch circuits and by the dc-dc converter are produced through a resistive divider network and through an operational amplifier used as a voltage follower. The circuits of the dc-dc converter section are generally grouped into one area of the station control module and may be located by referring to the circuit board detail at the end of this section.

### 2.2 BIAS VOLTAGE GENERATION DESCRIPTION

The five bias voltages (VA through VE) are produced by three circuits shown on the left side of the schematic at the end of this section. The 5.1-volt VE is derived from Zener VR701 and resistor R739 connected to the +9.6 V input regulator. The 4.8-volt VB is developed from the +9.6 V input to divider network R838-R839 used as the (+) input to operational amplifier U835B, which is configured as a voltage follower circuit. A divider network, comprised of R1538-R1539 and R1541-R1542, is used to produce the 5.1-volt VA, 4.8-volt VC, and 4.1-volt VD. Bias voltage VE is used in the dc-dc converter circuits while VA through VD are used in the audio and squelch circuits.

#### 2.3 +5 V POWER SUPPLY CIRCUIT

- 2.3.1 The majority of the dc-dc converter section comprises the +5 V power supply, as shown on the schematic diagram at the end of this section. Further details of operation are also included on the schematic diagram.

- 2.3.2 When the auxiliary 13.8 V supply comes up, the +9.6 V regulator also begins operation. Bias voltage VE provides a reference voltage to shutdown comparator U701A. Thus, when A + rises above 12 V, U701A output goes high and turns on oscillator U701C, allowing the station to begin operation after the +5 V supply stablizes. The station is kept in a reset condition, for at least 100 milliseconds after the +5 V output

comes on, by the RESET signal generated from U701B and Q705. This provides sufficient time for all transients to settle out before the MPU in the processor section begins its initialization/turn-on routine. The +5 V supply includes a current limiting circuit, consisting of Q704 and R731-R734, which reduces the +5 V supply output voltage if the output current exceeds approximately 2 amperes. The +5 V supply also includes an over-voltage protection circuit to prevent damage to the digital integrated circuits. If the +5 V supply output exceeds approximately 6 V, Q706 turns on causing the A + fuse, F701, to blow.

### 3. PROCESSOR SECTION THEORY OF OPERATION

#### 3.1 MC6803 MPU DESCRIPTION

3.1.1 The control center for the processor section is a Motorola MC6803 MPU, programmed to operate in Mode 2, which has multiplexed data/addresses (lower order), external interrupt vectors, internal random-access memory (RAM), and a 4.9068 MHz crystal-controlled clock source, but no internal readonly memory (ROM). The MPU operating mode is determined by the inputs at ports P20 through P22 (pins 8 through 10 of U801). With a diode in the circuit for a

particular port, its input bit is configured as a logic 0 on the trailing edge of the RESET pulse at U801-6. Without a diode and by using a pull-up resistor to +5 V, a mode input bit is figured as a logic 1 by the RESET pulse trailing edge. Therefore, with diodes in for P22 and P20, but out for P21, the MPU is configured for mode 2 operation. Refer to MC6801 8-Bit Single-Chip Microcomputer Reference Manual MC6801RM(AD) for more detailed information.

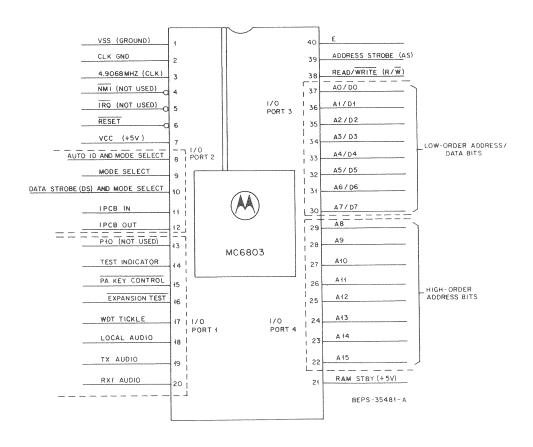

3.1.2 Ports 1 and 2 of the MPU are used for various input and output (I/O) signals. Port 3 is dedicated to multiplexed data and low-order address bits. Port 4 is dedicated to the high-order address bits. All I/O, control signals, and power/ground input pins are shown in Figure 2. Key control signals are described in the following paragraphs. The particular applications of the MPU's I/O lines are shown on the schematic diagrams at the end of this section. More detailed electrical specifications for these lines are available in the MC6801 Microcomputer Reference Manual MC6801RM(AD).

#### 3.1.2.1 Control Input/Output Pins

#### 3.1.2.1.1 READ/WRITE $(R/\overline{W})$ , pin 38

The  $R/\overline{W}$  output strobe is an active low pulse that is generated for an MPU read or write to the

Figure 2.

Motorola MC6803 MPU Pin Configuration

Port 3 data register in the MPU, depending upon the MPU's control configuration. The  $R/\overline{W}$  pulse, approximately one E-cycle wide (that cannot be varied), is used for memory map decoding and as a strobe input to the code plug.

#### 3.1.2.1.2 ADDRESS STROBE (AS), pin 39

The AS output strobe is used as a Latch Enable (LE) input for Address Latch (Low-Order) U802. It latches the addresses on its falling edge.

#### 3.1.2.1.3 ENABLE (E), pin 40

The E signal is the primary MPU system timing signal and synchronizes all DATA bus transfers. An MPU E-cycle (or bus cycle) consists of a negative half-cycle of E followed by a positive half-cycle. The data bus is active only while E is high or, equivalently, "during E".

#### 3.1.2.1.4 PA Key, pin 15

Port 12 (pin 15) outputs PA Key, a control signal that is gated to the station transmitter power control circuit.

#### 3.1.2.1.5 DATA STROBE (DS), pin 10

The DS signal is used to strobe multiplexed address and data (MUXBUS signals) to EXPANSION connector J800 for intermodule operations. The signal is buffered and inverted by U822B and U827B before it is applied to the EXPANSION connector as  $\overline{DS}$ . The signal edges indicate the status of the address and data on the MUXBUS lines. The falling edge of  $\overline{DS}$  indicates that the station control MPU has written a new address to the MUXBUS. The rising edge of  $\overline{DS}$  indicates that all modules have written the appropriate data to the MUXBUS.

#### 3.1.2.1.6 IPCB Out, pin 12, IPCB In, Pin 11

These pins provide the serial communication transmit and receive lines of the MPU. They are connected to the bidirectional Interprocessor Communications Bus (IPCB), on EXPANSION connector J800, via buffer/invertes U826F, U827A, U826E, and U822F.

#### 3.1.2.2 Microprocessor Control Bus Signals

Port 3 consists of P30 through P37 (pins 37 to 30 of U801) and is used for the multiplexed low-order address bits/data. Thus, depending upon the internal MPU programming control, port 3 will output the eight low-order address bits or port 3 will provide or accept eight bits of data via the DATA bus. Port 4 consists of P40 through P47 (pins 29 to 22 of U801) and is dedicated to the high-order address bits. That is, port 4 will not accept inputs, being used only to output the eight higher order bits of any particular address.

#### 3.1.3 Watchdog Timer Description

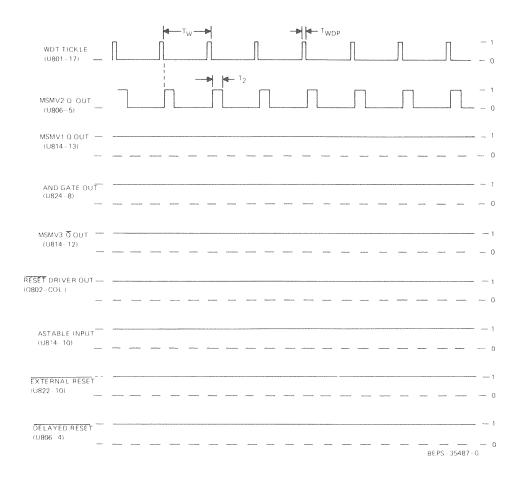

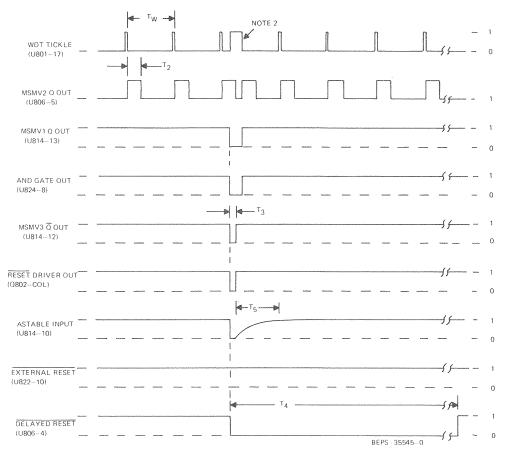

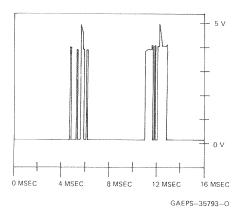

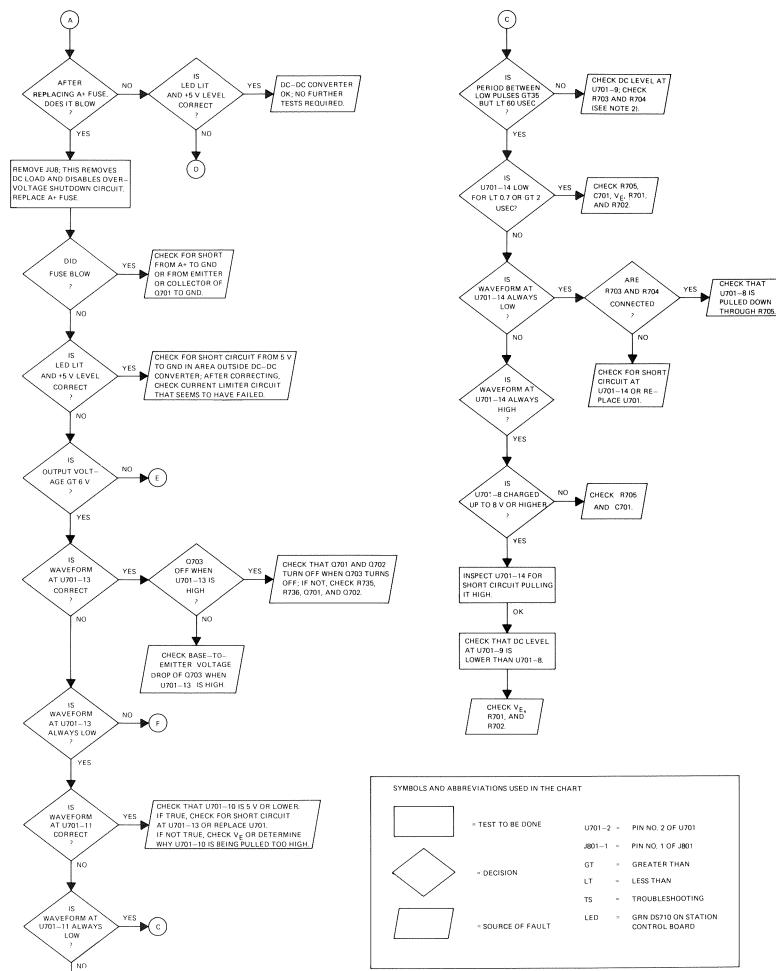

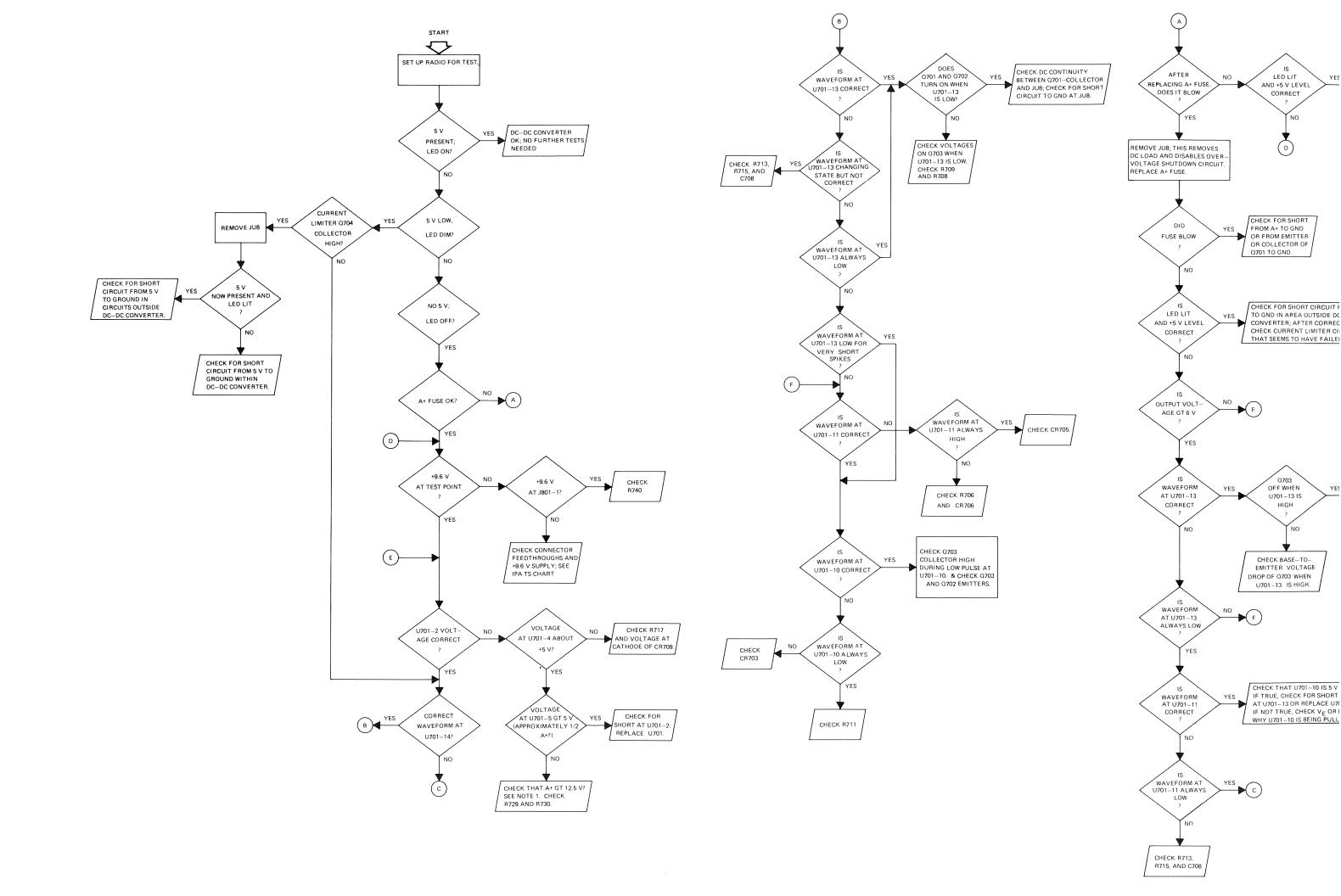

3.1.3.1 When the MPU is operating properly, it outputs the WDT TICKLE pulses (on U801-17) that are characterized by a given periodicity, as shown on the timing diagram for normal operation in Figure 3 and listed in Table 1. The watchdog timer circuit monitors this period and, if the pulses are not within a predetermined range (i.e., timing "window"), the watchdog timer circuit resets the MPU. At the same time, it prevents other circuits from experiencing any ill effects of a MPU control section malfunction by holding them reset until the MPU is again operating properly.

3.1.3.2 Monostable multivibrators (MSMV) U814A and U806B are used to set the tickle-pulse period range by forming a window in which the pulse must occur. In normal operation, U814A is kept retriggered by the negative-going edge of the MPU tickle pulse (Figure 3). The U814A time constant determines the maximum allowable tickle period. If tickle pulses occur too far apart, U814A times out, and generates a reset pulse through U814B and Q802. The U806B time constant determines the minimum allowable tickle period. If tickle pulses occur too close together, the normal output from U806B allows the "too-early" tickle pulse through NAND gate U823D to clear MSMV U814A, which again causes a reset pulse to be generated by U814B and Q802.

Table 1. Timing Parameter Chart

| Parameter        | Description Timing Range                  | Average | Units |

|------------------|-------------------------------------------|---------|-------|

| tw .             | Watchdog Timer Tickle Period 35-71        | 53      | ms    |

| t <sub>WDP</sub> | Watchdog Timer Tickle Pulse Width 40-300  | 170     | uS    |

| t1               | MSMV U814A Time Constant 89-214           | 151     | ms    |

| t2               | MSMV U806B Time Constant 9-21             | 15      | ms    |

| t <sub>WND</sub> | Window Width (t1-t2) 68-205               | 136     | ms    |

| t3               | MSMV U814B Time Constant 2.5-4.5          | 3.5     | ms    |

| ţ4               | MSMV U806A Time Constant 490-1389         | 935     | ms    |

| t5               | Astable Time Constant (C807, R823) 14-230 | 122     | ms    |

1. All timing is approximate, due to component variation.

Figure 3.

Normal Operation Timing Diagram

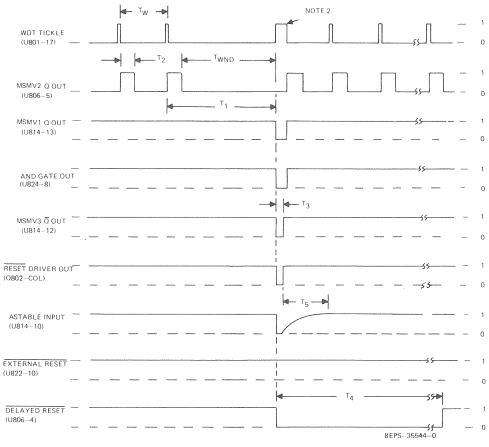

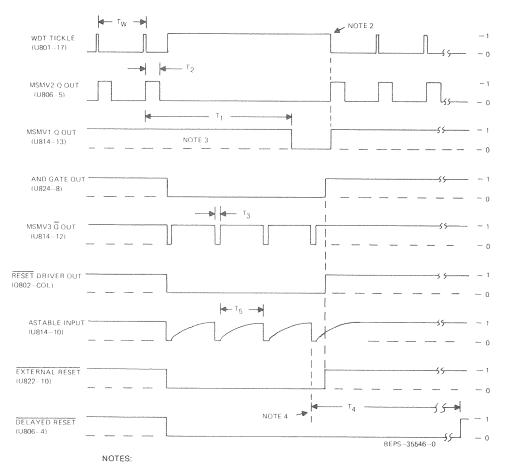

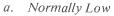

3.1.3.3 The MPU reset occurs in the following manner. Retriggerable MSMV U814B generates a reset pulse whose duration is determined by its time constant (established by C805 and R820). This occurs when the A input at pin U814-9 goes active (low) as a result of improper tickling (see timing diagrams for abnormal operations as shown in Figures 4 and 5). As part of the reset procedure, the B input (pin 10) of U814B goes inactive (low) through the action of Q803 being turned on by the Q output from U814B. With the B input of U814 inactive, the MPU has time to go through its startup routines and begin outputting tickle pulses; the first tickle pulse should occur about six milliseconds after the trailing edge of the RESET pulse (see Figure 4 and 5). However, if no tickle pulse occurs, the A input remains active and another RESET pulse is generated when the charging circuit C807-R823 reaches the MSMV triggering level at the B input of U814B. This astable operation will continuously attempt to reset the MPU as long as improper tickling occurs, as shown in Figure 7 for a MPU malfunction. When the MPU properly outputs a tickle pulse after being reset, the Ā input for U814B goes inactive (high) and prevents any additional RESET pulses from occuring due to the astable operation of U814B.

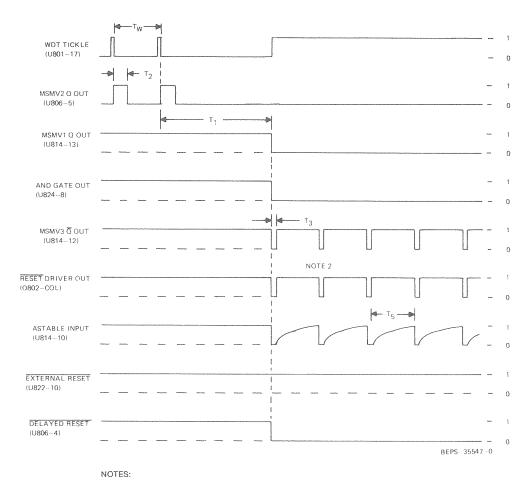

3.1.3.4 An external reset function for the Watchdog timer circuit is incorporated in the following manner. As long as the EXPANSION RESET signal is held active (low), U814B will astable as described previously. Furthermore, the MPU will be held in reset by the action of NAND gate U823C (see timing diagram for an external reset, as shown in Figure 6). In this case, the astable operation is not needed to reset the MPU, but instead is used to retrigger Delayed Reset MSMV U806A. The EXPANSION RESET signal is also used to clear MSMV U806B, so that when the WDT tickle signal is pulled high as a result of a reset, another reset does not occur due to a low output from U823D.

#### NOTES:

- 1. All timing is approximate, due to component variation.

- The <u>Watchdog</u> Timer (WDT) tickle signal is pulled low approximately 6 ms after the <u>RESET</u> signal to the processor goes inactive (high).

Figure 4.

Abnormal Operation Timing Diagram

(Tickle Pulse Late or Missing)

3.1.3.5 The DELAYED RESET output from U806A is used to hold other circuits of the processor section (e.g., PA Key, DS, IOR, and IOW) inactive until the MPU properly tickles the WDT circuit and astable operation has ceased. The time constant for U806A is such that the DELAYED RESET signal is active long enough to guarantee that two proper tickle pulses will occur after the final reset to the MPU (a single tickle pulse could be the result of a MPU malfunction). During an external reset, the astable operation of U814B keeps U806A retriggered so that it cannot time out early (as shown in Figure 6).

#### 3.1.4 Test/Reset Arbiter Description

The Test/Reset Arbiter circuit performs two functions. First, the MPU can generate an EXPAN-SION TEST signal without resetting itself. When the EXPANSION TEST signal at U801-16 switches low, the low is applied directly to U823B-4 before a high signal propagates to U823B-5 via U822C, U826B, and U822D.

Therefore, U823B-6 remains high and no EXPANSION RESET signal occurs. When the EXPANSION TEST signal switches high, U823B-6 switches momentarily low until a low signal propagates to U823B-5. This low signal is short enough, however, that capacitor C879 cannot charge up to a logic high level and therefore, no EXPANSION RESET signal occurs. Second, when a reset command, generated externally to the station control board, is received, the Test/Reset Arbiter circuit produces an MPU reset. This is accomplished since the inactive state of the EXPANSION TEST signal allows the EXPANSION RESET signal through NAND gate U823B to become the EXTERNAL RESET signal. The EXTERNAL RESET generates a MPU reset as described previously, and can occur due to:

- RESET from the expansion bus connector

- RESET from the DC-DC converter section

- RESET from the remote control connector

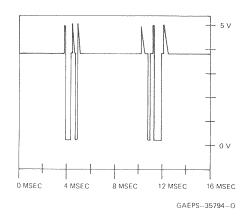

#### NOTES:

- 1. All timing is approximate, due to component variation.

- The <u>Watchdog</u> Timer (WDT) tickle signal is pulled low approximately 6 ms after the <u>RESET</u> signal to the processor goes inactive (high).

Figure 5. Abnormal Operation Timing Diagram (Tickle Pulse Early)

#### NOTE

Switch S801, when put to the TEST position, can also generate an external reset via the DC-DC Converter section.

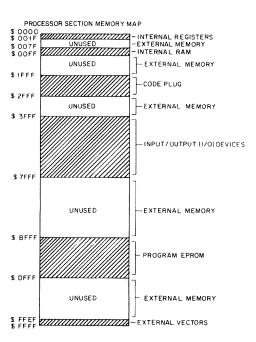

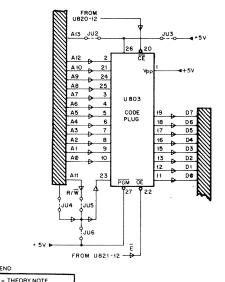

#### 3.1.5 Memory Devices Description

3.1.5.1 The main executable code for the processor section is stored in station program EPROM U804, (an 8k × 8 EPROM). U804 contains the operating program for the station. It, interacts with the personality data stored in code plug U803, and the changing

parameters of the station itself, to control station operation. The station program EPROM shipped in any station contains unique information which makes it compatible with that station hardware and code plug. Extreme care must be exercised when exchanging station program EPROM's between stations, or when replacing damaged parts. If a malfunction should be localized to U804, the device must be exchanged for an operational device with the same Motorola part number.

3.1.5.2 The other memory device for the processor section is code plug U803, which stores the station configuration ("personality") data. It is a  $4k \times 8$  EPROM device. Table 2 gives the memory locations of these devices and provides a memory map of all other station control functions. Table 3 gives proper jumper usage for the various operational characteristics.

Table 2. MSF 5000 Station Control Memory Map

| Name                   | Туре | Software<br>Address Used | Comments                                             |  |

|------------------------|------|--------------------------|------------------------------------------------------|--|

| Internal Registers     | R/W  | \$0000-\$001F            |                                                      |  |

| External Memory        |      | \$0020-\$007F            | Unused — See Code Plug                               |  |

| Internal RAM           | R/W  | \$0080-\$00FF            |                                                      |  |

| External Memory        |      | \$0100-\$1FFF            | Unused — See Code Plug                               |  |

| Code Plug              | R    | \$2000-\$2FFF            | Hardware Allows Use of \$0000-\$3FFF                 |  |

| 1/O Devices*           | R/W  | Defined as Follows       | Hardware Allows Use of \$4000-\$7FFF                 |  |

| Bus Read Data Buffer   | R    | \$59FF                   | AI3 • IOR (Note 2)                                   |  |

| MUX bus Latch          | W    | \$69FF                   | A12 • IOW (Note 3)                                   |  |

| Synthesizer Latch      | W    | \$71FF                   | AII • IOW                                            |  |

| TX Synth Strobe        | W    | \$7DFF                   | A10 • <del>IOW</del>                                 |  |

| RX Synth Strobe        | W    | \$7BFF                   | A9 • IOW                                             |  |

| PL/DPL DAC Latch       | W    | \$78FF                   | A8 • IOW                                             |  |

| TX/RX Status Buffer    | R    | \$797F                   | A7 • IOR                                             |  |

| Options Latch          | W    | \$79BF                   | A6 • TOW                                             |  |

| Options Buffer         | R    | \$79DF                   | A5 • IOR                                             |  |

| Command/Service Buffer | R    | \$79EF                   | A4 • IOR (Note 2)                                    |  |

| System ROM             | R    | \$C000-\$DFFF            | Hardware Allows Use of \$8000-\$FFFF                 |  |

| Internal ROM Space     |      | \$F800-\$FFEF            | Unused                                               |  |

| External Vectors       | R    | \$FFF0-\$FFFF            | \$DFF0-\$DFFF Used to Read Software<br>\$FFFF-\$FFFF |  |

| *Undefined I/O Devices | R/W  | \$79F0-\$79FF            | Address, as shown will not select a device           |  |

#### NOTES:

- 1. The symbol "\$" preceding any alphanumeric character(s) means that the character(s) are HEX coded.

- 2.  $IOR = E \cdot R / W$  (DEL RS) (A14 A15), where DEL RS = Delayed Reset, and is High.

3.  $IOW = E \cdot R/W (DEL RS) (A14 \cdot A15)$ .

Table 3. Diode and Jumper Usage

| Ref. Design | Normally | Description                                                        |

|-------------|----------|--------------------------------------------------------------------|

| CR801       | IN       | Out for MPU operation mode where program code (PC) $\emptyset = 1$ |

| CR802       | OUT      | In for MPU operation mode where program code (PC) $1 = \emptyset$  |

| CR803       | IN       | Out for MPU operation mode where program code (PC) 2 = 1           |

| JUI         | OUT      | In to disable software power control and enable PA fail alarm      |

| JU2         | OUT      | In for 8k × 8 EPROM                                                |

| JU3         | IN       | Out for 8k×8 EPROM                                                 |

| JU4         | OUT      | In for 2k × 8 RAM                                                  |

| JU5         | IN       | Out for 2k × 8 EPROM; out for 2k × 8 RAM                           |

| JU6         | OUT      | In for 2k×8 EPROM                                                  |

| JU9         | IN       | Out for 2k×8 RAM                                                   |

| JU10        | OUT      | In for 2k × 8 RAM                                                  |

| JU11        | IN       | Out for 2-RCVR station                                             |

#### 3.1.6 Address Latch Description

The address latch (U802) is used to hold the low-order address bits from the multiplexed address/data lines output at port 3 of the MPU. Latch U802 is transparent (i.e., passes a signal as if it were not there) while the Latch Enable (LE) input is high. The LE signal is the ADDRESS STROBE (AS) signal from the MPU, and when the AS signal goes low (inactive), the address bits are latched into U802. The address lines of U802 are

output to the ADDRESS/CONTROL bus, forming part of the total address used to control the various parts of the processor section.

#### 3.1.7 Memory Map Decoder Description

The Input/Output Read (IOR) and input/output write (IOW) are two control signals that are generated by the memory map decoder circuits to allow selection of I/O devices in the processor section. The IOR signal provides an enable for the group of I/O devices that the processor reads (i.e., obtains data from), while the IOW signal provides an enable for the group of I/O devices to which the processor writes (i.e., passes data to). For both groups, the control signal provides only one enable to the device. The second enable signal needed is an address line. Both types of enable or gating signals are carried on the CONTROL SIGNALS TRUNK (see schematic at the end of this section) to each device controlled by the processor section for input and output functions. The control signals and addresses used for I/O device selection are listed in the station control board memory map chart of Table 2.

#### 3.1.8 Synthesizer Latch Description

The data that the processor writes to the synthesizer latch (U805) are used to program the transmit and receive frequencies for the station. This information is configured as four data bits and three address bits for use by the synthesizers (one output is not used).

- 1. All timing is approximate, due to component variations.

- The <u>Watchdog</u> Timer (WDT) tickle pulse is pulled low approximately 6 ms after the <u>RESET</u> signal to the processor goes inactive (high).

- The MSMV1 Q Output will not change state (High to Low) if the EXTERNAL RESET signal is held active (low) for less than the remaining T<sub>1</sub> time.

- Since MSMV4 (U806A) is kept retriggered, the DELAYED RESET time T<sub>4</sub> begins with the falling edge of the last output from U814B-12.

Figure 6.

Timing Diagram Showing Effects of External Reset Signal

In order to program the synthesizers, seven sets of data are written to the latch for each synthesizer. This information is then strobed to the appropriate transmit or receive synthesizer circuits by means of the logic gates generating the transmit strobe (TX STROBE) and receive strobe (RX STROBE) signals.

#### 3.1.9 PL/DPL DAC Latch Description

The Private-Line/Digital Private-Line (PL/DPL) digital-to-analog converter (DAC) latch (U808) supplies the five bits necessary to encode PL or DPL control information. The outputs from U808 are routed to the DAC circuit in the audio section where they are used to generate the proper code for the transmit audio signal. The DPL rotate bit, another output of the latch, is routed to the options buffer and used to signal the processor to rotate the DPL encode word by one bit.

This rotation occurs every 7440 microseconds in order to supply a new encode bit to the DAC circuit. The remaining two latch outputs are unused.

#### 3.1.10 Options Latch Description

The MPU writes eight different control signals to the options latch (U807). The PL/DPL bit controls the configuration of the decode filters used to decode either PL or DPL in the receive audio signal. The deviation control bit allows reduction in the deviation of the transmit modulated audio signal. The PA power adjust signal is gated to the power control section and controls reduction in the PA power. The antenna switch output of latch U807 is gated to the interconnect board and controls switching of the antenna switch. The alarm audio control and repeater audio control bits control

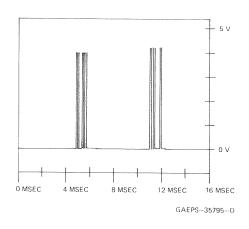

- 1. All timing is approximate, due to component variation.

- The astable operation of MSMV3 (U814B) generates pulses in an attempt to reset the processor.

Figure 7.

Timing Diagram Showing Effects of MPU Malfunction

gating in the audio circuits area. The alarm audio control allows the auto ID signal (and alarm tones) to be mixed onto the line audio signal. The repeater audio control bit controls mixing of the RX1 Audio signal with the TX Audio signal. The squelch level bit is used for remote control of receiver 1 squelch level, and the adapt bit allows the squelch circuit to clear its detect indication quickly for use with channel scan operation.

#### 3.1.11 TX/RX Status Buffer Description

Two inputs to buffer U809 are controlled by the power control circuit and are used as status signals. These signals, PA On and PA Full Power indicate whether the PA is on and whether it is operating under full power. Partial power (or power cutback) capabilities may be used with options (such as battery backup) and for minimizing damage in case of a PA or related failure. The following four signals are inputs to the buffer from the transmitter and receiver circuits. The Tx Lock and Rx Lock signals specify whether the

transmitter and receiver are locked on a frequency while Tx Loop and Rx Loop are synchronizing signals used to indicate when the processor can output new transmitter and receiver frequency data to the synthesizers. The loop signals are ignored during normal station operation but are available for synchronous synthesizer loading for special products such as channel scan stations that require fast synthesizer locking. The remaining two signals, RX1 Unsquelch and Repeater Unsquelch, indicate when the receiver 1 audio (RX Audio) is at a quieting level sufficient to activate the receiver 1 and repeater squelch circuits.

#### 3.1.12 Options Buffer Description

All eight inputs of buffer U810 are used for distinct functions. The PL/DPL Decode Data signal is the low-pass filtered and limited PL or DPL data to be decoded by the processor. The DPL Rotate bit signals the processor to rotate the DPL code. The Battery Revert and Overvoltage Alarm signals are inputs to the processor from the dc-dc converter circuits. These two

signals originate from the battery charger board of the power supply. The Battery Revert signal indicates that the station is operating under battery power. The Overvoltage Alarm bit signals that a charging circuit malfunction has occurred (such that the batteries are being overcharged). This results in the charging circuit being disabled and in the station operating on batteries (servicing is required to resume non-battery operation). The DC/TRC signal specifies which module type (tone or dc control) is in the remote control slot. The Intercom bit is activated by a dc remote or a tone remote control front panel switch and is used when servicing the station. This bit, along with a MIC PTT, results in gating the local or service audio signal outbound on the wireline and prevents the PA from keying. If the Intercom bit is active without a MIC PTT signal, the TX audio signal is gated to the local speaker. In both cases, the receiver audio is allowed to mix with the given signal. Note that these intercom functions are disabled if a RPTR PTT or a LINE PTT occurs. Channel Activity is a signal from the receiver 1 squelch circuit similar to RX1 Unsquelch and is to be used for special applications such as channel scan operation, resulting in a faster unsquelch. The Service input indicates that the service jumper is in place, causing software power control to be inhibited and a PA FAIL alarm to be activated.

#### 3.1.13 Command Service Buffer Description

Four inputs to buffer U813 are configured as a 4-bit word from the remote control connector. When a tone remote control board is used, this word consists of the current status of the channel select switch on the tone remote control board. When the dc remote control board is used, without the access disable switch activated, the word consists of the dc current information. When the dc remote control board is used, with the access disable switch activated, the word consists of the status of the channel select switch on the front panel of dc remote control. The MIC PTT input indicates that a Push-To-Talk (local) was generated by means of the CONTROL connector J812. The three remaining buffer connections are used to read three switch inputs, Access Disable, Transmit, and PL Disable. The Access Disable position of S801 (ACC DIS) inhibits several functions: auto ID, alarm tones, time-out timer, repeater PTT from the receiver, and some wireline commands including line PTT. The Transmit position of S802 (XMIT) results in a PA key without audio or the encoding of PL or DPL. This position of S802 also acts to strip PL or DPL from any signal currently being transmitted (i.e., carrier squelch operation). The PL Disable position of S802 (PL DIS) is used to locally monitor all receiver activity, regardless of the PL or DPL code. This position of S802 allows the opening of the receiver audio gate with only receiver activity (i.e., carrier squelch operation).

#### 3.1.14 MUX Bus Write Latch Description

This latch (U811) holds information that will be written to the EXPANSION connector (J800) by the processor section. Four bits (BA0 through BA3) are configured as the address and the four remaining bits (WD0 through WD3) are routed through open-collector inverter buffers as the multiplexed "write-data" corresponding to that address.

#### 3.1.15 MUX Bus Read Data Buffer Description

Four inputs to buffer U812 are unused while the remaining four are used to read the multiplexed "busdata" bits (BD0 through BD3) that are present at the EXPANSION connector. The data at J800 is inverted from that written to expansion bus latch U811.

#### 3.1.16 Synthesizer Failsafe Circuit Description

If the transmit synthesizer is not locked onto the selected frequency, the synthesizer failsafe circuit prevents or aborts power amplifier (PA) keying. Flipflop U818A is a D-type whose output (pin 5) is a logic high while the TRANSMIT SYNTHESIZER LOCK signal is inactive (high). After the transmit synthesizer locks onto its selected frequency, the TX LOCK signal is active (low), is inverted by U822A, and enables flipflop U818A to output a low signal. This occurs when the MPU outputs a PA key control signal and DELAYED RESET is inactive. The low Q-output from U818A is inverted by U826D to turn on transistor Q804, whose output is the PA KEY signal to the radio interface J801.

#### 3.1.17 Front Panel Indicators Description

3.1.17.1 The light-emitting diodes (LED's), used as indicators on the front panel of the station control board, are color-coded according to their function. The red LED's indicate a failure or servicing status.

#### **IMPORTANT**

Stations should not normally be returned to operation after service while any red LED is on.

3.1.17.2 The green LED's indicate active operation of the named signal. The yellow LED's indicate a request for action or a warning status. The functions of these front panel indicators are fully described in the Operation section of this manual.

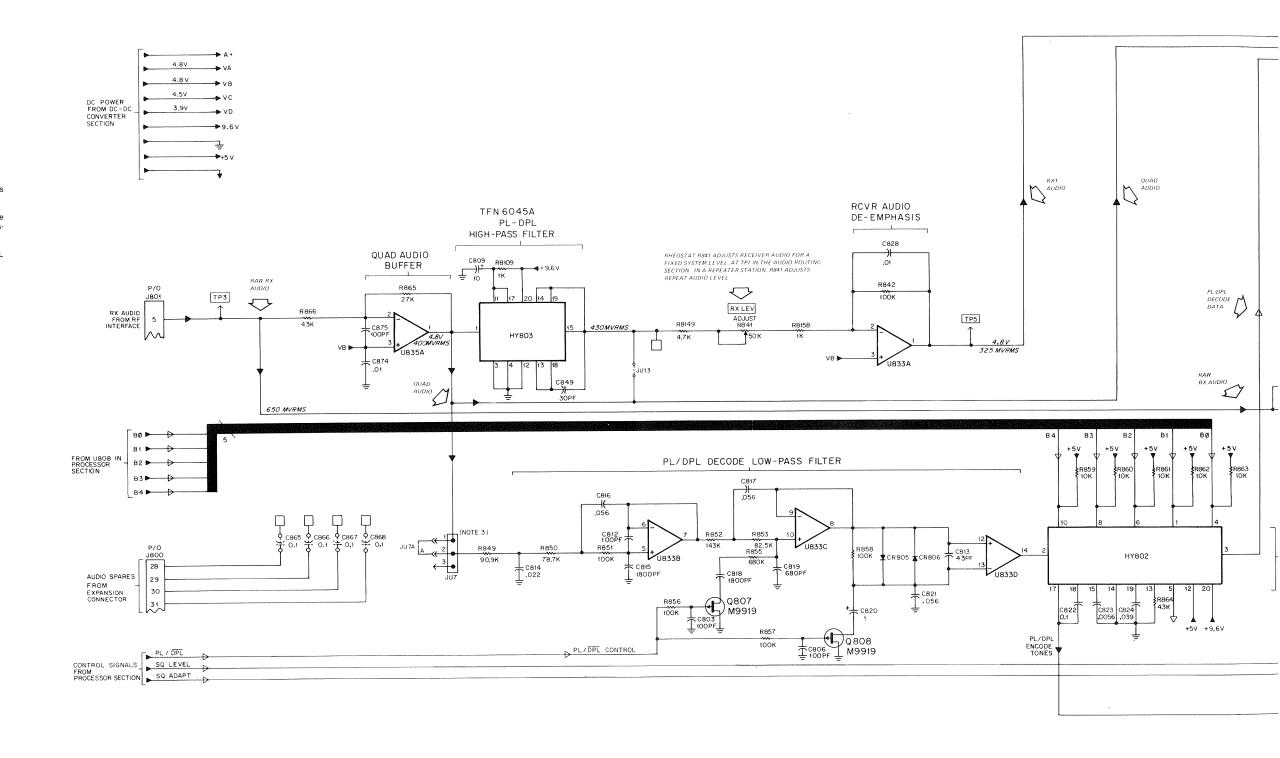

### 4. RECEIVER AUDIO, PL/DPL, AND SQUELCH SECTION THEORY OF OPERATION

#### 4.1 GENERAL

The receiver audio, PL/DPL, and squelch section of the station control board (see schematic diagram)

provides the primary processing for the receiver audio and squelch portions of the station. Raw receiver audio is split into two paths, one is used for squelch control and the other is used for audio processing. Audio from the Quad Audio Buffer (U835A) is routed through a PL/DPL low-pass filter (U833B, C, and D) to the PL/DPL Digital-to-Analog Converter (DAC) hybrid (HY802) for decoding of PL and DPL data. Quad audio is also routed to EXPANSION connector J800-39.

#### 4.2 RECEIVER AUDIO CIRCUITS DESCRIPTION

Receiver audio to be routed to the local speaker and wireline, or routed to the transmitter, is processed by this section of the station control board. Raw receiver audio is buffered by U835A, whose output (Quad audio) is supplied to PL/DPL high pass filter hybrid HY803 and through jumper JU7 to the PL/DPL decode low pass filter. Filter HY803 removes the coded squelch tones from the received audio and passes the filtered receiver audio to the RX LEV control R841, a front panel accessible potentiometer, which adjusts the internal system-level setting for audio (available at TP1. at U834B-7). The system level adjusted audio is deemphasized by amplifier stage U833A, whose output is then routed to the RX1 audio gate (U823A) in the audio routing/control section of the station control board. RX1 audio is also routed to EXPANSION connector J800-38.

#### NOTE

A plated through pad on the printed circuit board has been provided at HY803-15 for applications that require receiver audio with PL/DPL codes removed, but not de-emphasized.

#### 4.3 PL/DPL CIRCUITS DESCRIPTION

- 4.3.1 Receiver quad audio from U835A is routed to a 5-pole, low-pass filter consisting of amplifiers U833B and U833C. The filter separates the PL and DPL tones from voice audio and higher frequency noise signals that may be present in the received audio. When DPL tones are being decoded, FET switch Q807 is turned on, changing the filter to optimize DPL decoding. A low signal on the PL/DPL control line from the processor section turns FET Q807 on.

- 4.3.2 The filtered PL/DPL audio is applied to limiter stage U833D, which produces the zero-crossing data used for decoding purposes. The limiter is also optimized for DPL decoding by FET switch Q808 that is turned on by the same PL/DPL control line from the processor section that controls Q807. The zero-crossing data is buffered to TTL-voltage levels (i.e., HI greater than or equal to 2 V, and LO less than or equal to 0.8 V) by DAC/low-pass filter HY802. Hybrid HY802 then routes the PL/DPL decode data to options buffer U810 in the processor section of the station control board.

4.3.3 Hybrid HY802 also produces the PL/DPL encode tones. This is accomplished by using the data bits sent by PL/DPL DAC latch U808 in the processor section. The filtered tones for either PL or DPL are routed to the instantaneous deviation control (IDC) R889 adjustment circuit in the audio routing/control section of the station control board.

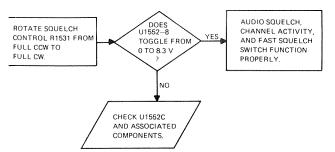

### 4.4 SQUELCH CONTROL CIRCUITS DESCRIPTION

#### 4.4.1 Squelch Input

The input to amplifier U1550A is a noise preemphasis network that boosts the noise content of the input signals above 5 kHz. For squelch processing, the first amplifier/limiter is driven into limiting to prevent audio signals from squelching the receiver. Amplifier/limiter U1550B again amplifies the noise signal and relimits audio signals to provide further protection against audio signals squelching the receiver. The output signal of U1550B is then used to drive both the audio and repeater squelch circuits.

#### 4.4.2 Audio Squelch Detector and Switching Circuits

- 4.4.2.1 The amplified noise output signal level is adjusted by SQUELCH control R1531 and sent to the noise detector (U1550D) via audio squelch buffer U1550C. The input network to the detector provides further attenuation of audio and any harmonics generated by audio limiting at the output of U1550B. Noise detector U1550D is a half-wave rectifier amplifier that produces negative going spikes at its output. The average dc value of these spikes is a function of received signal strength. The lowest average dc output voltage corresponds to a no-signal input (maximum noise) condition. As the received signal strength increases, the noise level decreases, and the average dc output voltage increases.

- 4.4.2.2 The squelch switching circuit operates in two modes. With a receive signal just above the opening sensitivity, squelch closing is slow (approximately 150 ms), which produces the squelch tail heard at the end of a received message. The 150 ms delay is present to prevent the received message from being chopped during a weak fluttering signal. With a strong signal (approximately 10 dB above opening sensitivity), squelch closing occurs immediately after the end of a received signal. This prevents the squelch tail from being heard.

- 4.4.2.3 Active integrator U1552D provides squelch opening and slow squelch closing. Comparator U1552B compares the detector's average dc output voltage with a reference voltage to determine the level for squelch opening and closing.

4.4.2.4 Fast squelch closing is provided by U1552C. A strong signal charges C1553 through R1545, driving U1552C low. At the end of a strong signal, any noise spikes from the detector are captured by CR1523. This immediately discharges C1553 and forces U1552C high. Then, capacitor C1552 forces U1552B to close the squelch.

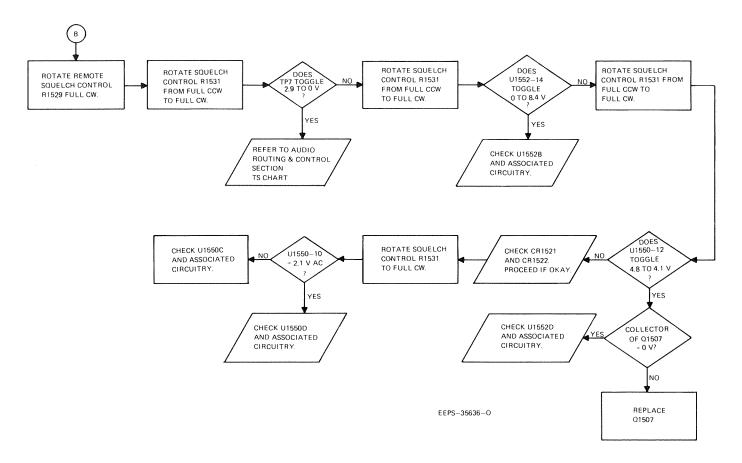

#### 4.4.3 Remote Squelch Control

Remote squelch switch Q1506 is remotely signaled to switch REM SQ control R1529 in parallel with R1531. This reduces the noise level input to the audio squelch circuit. It serves to provide a remotely controlled second squelch level that is lower than that of the primary audio squelch control setting.

#### 4.4.4 Squelch Adapt Control Switch

Squelch Adapt Control Switch Q1507 is turned off when the synthesizers are in the "adapt" mode. When off, the collector of Q1507 goes to 9.6 V, forcing U1552C low and U1552D high. This causes the squelch to be in a fast detect mode.

#### 4.4.5 Channel Activity Switch

The output of U1552D is used to control Q1508. This provides a fast responding open collector output signal to the processor section. This signal is used in channel-scan operation.

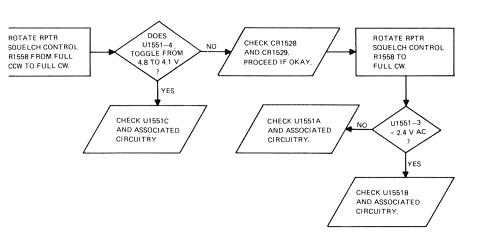

## 4.4.6 Repeater Squelch Detector and Switching Circuits

- 4.4.6.1 The repeater squelch circuits are very similar to the audio squelch circuits. They provide a separate adjustable squelch level for controlling the repeater function. The amplified noise output signal level is adjusted by RPTR SQ control R1558 and sent to noise detector U1551B via RPTR squelch buffer U1551A. The input network to the detector provides further attenuation of audio and any harmonics generated by audio limiting at the output of U1550B.

- 4.4.6.2 Noise detector U1551B is a half-wave rectifier amplifier that produces negative-going spikes at its output. The average dc value of these spikes is a function of received signal strength. The lowest average dc output voltage corresponds to a no-signal input (maximum noise) condition. As the received signal strength increases, the noise level decreases, and the average dc output voltage increases.

- 4.4.6.3 Active integrator U1551C provides squelch opening and slow squelch closing. Comparator U1551D compares the voltage to determine squelch opening and closing. The tight squelch level for the repeater squelch is typically 2 dB greater than the audio squelch. Squelch closing time is typically 200 ms.

### 5. AUDIO ROUTING/CONTROL SECTION THEORY OF OPERATION

#### 5.1 GENERAL

- 5.1.1 The major audio routing for proper base station/repeater operation is accomplished by the circuits in this section of the station control board. There are five audio control gates (refer to schematic diagram), as follows:

- RX1 Audio Gate (U832A)

- TX Audio Gate (U832B)

- Local Audio Gate (U832C)

- Repeater Audio Gate (U831A)

- Alarm Audio Gate (U831B)

The five gates control four major audio signals, as follows:

- Local audio

- Transmitter audio

- Receiver 1 audio

- Alarm tones

The gates route the various audio signals to the proper summing amplifiers as required to produce the desired audio outputs as determined by the PTT signal and the control program.

- 5.1.2 When more than one type of PTT command occurs simultaneously, then the station control module operating program chooses the PTT with the highest priority. The PTT priority is determined by the code plug programming and can be varied on a perchannel basis. For example, channel 1 may be programmed with line PTT having priority over repeater PTT, and channel 2 may be programmed oppositely, in the same station.

- 5.1.3 Unless specified to be different, the stations are normally programmed with line PTT having priority over repeater PTT and both having priority over local PTT. Only those control functions associated with the priority PTT will occur. For example: if a line PTT and local PTT occur together, and if line PTT has priority, then the TX audio gate will open, routing remote wire line audio to the transmitter; while the local audio gate will be closed, preventing local microphone audio from reaching the transmitter.

- 5.1.4 Any PTT command has priority over the XMIT position of S802 on the front panel of the station control module. However, the activation of S802 to the XMIT position will cause transmit PL or DPL to be stripped from any other PTT transmit signal. Additional details for gate timing and routing are included in the theory notes given on the schematic diagram for the audio routing/control section.

#### 5.2 SUMMING NETWORK/AMPLIFIERS

- 5.2.1 The three summing network/amplifiers (U834B, C, and D) combine and amplify the selected audio signals for output from the station control board.

- 5.2.1.1 The transmit audio summing amplifier (U834D) buffers:

- local audio (either from the microphone, via CON-TROL connector J812-4, or the local audio, from EXPANSION connector J800-33)

- transmit audio from remote control connector J804-5

- RX1 (receiver 1) audio via repeater audio gate U831A, from the audio control and squelch section of the station control board.

The buffered TX audio signal modulates the selected transmit frequency for the base station.

- 5.2.1.2 The select audio summing amplifier (U834B) buffers:

- transmit (TX) audio

- received (RX1) audio

- automatic station identification and alarm tones (AUTO ID/ALARM)

- RX2 audio (from a second receiver via J800-35).

The buffered select audio signals provide an output to the local speaker at J812-2, via the 1/2 watt audio circuits, or to other local speakers, via J800-32.

- 5.2.1.3 The line audio summing amplifier (U834C) buffers:

- local audio

- RX1 audio

- RX2 audio and

- AUTO ID/ALARM audio.

The buffered line audio signals provide an output to the remote control board, via J804-4, where it is amplified for outbound wireline transmission.

5.2.2 For dual receiver stations, second receiver audio is filtered for PL/DPL tones, then deemphasized and gated on the control board of the second receiver. The filtered and gated RX2 audio is then routed to the station control board via J800-35. When a second receiver is used, jumper JU11 is removed (see diode/jumper usage in Table 3).

#### 5.3 AUTO ID LOW-PASS FILTER

Under program control, the MPU generates a square wave signal at an 800 Hz rate (at U801-8) for the

automatic station identification code and at a 1600 Hz rate for alarms. The automatic ID low-pass filter circuit (U835C) removes most of the harmonics of the tones, attenuating the alarm tones relative to the automatic ID tones. The alarm tones produce about  $\pm 1.5$  kHz deviation upon transmission and the ID tones about  $\pm 2$  kHz deviation. The ID and alarm tones are routed through the splatter filter circuit to the IDC summing amplifier, bypassing the preemphasis circuit of C835 and R8132. Both types of tones are also routed to the local speaker amplifier and outbound wireline circuits.

#### 5.4 TRANSMIT AUDIO CIRCUIT

- 5.4.1 The buffered transmit audio signal is routed from the TX Audio Summing Amplifier (U8340) to amplifier circuit U838B, which provides preemphasis (via C835 and R8132) and serves as a limiter before the IDC summing amplifier. The preemphasis circuit, enhances the audio frequencies toward the high end of the transmit audio frequency range (300 to 3000 Hz). Limiter amplifier U838B clips the audio at about 5.8 volts, peak-to-peak (2.1 VRMS), to prevent excessive audio modulation of the transmitted signal (with low-voltage audio inputs, the amplifier acts as a linear gain stage).

- 5.4.2 The preemphasized, limited audio is resistance coupled to splatter filter U838A, a 3 kHz low-pass filter that removes the high order harmonics from the audio signal. Having a unity gain, the amplifier is used to attenuate the high-frequency harmonics that are present in the clipped audio signal from the preemphasis/limiter circuit. The splatter filter output, which contains voice audio and automatic ID/alarm tones, is then combined with the PL/DPL encode tones at IDC summing amplifier U835D. The audio level presented to the amplifier input is controlled by IDC/DEV control R889, which can be accessed from the front of the control tray.

#### 5.5 DEVIATION CONTROL CIRCUIT

- 5.5.1 The deviation bias gate (U831C) is used for applications where a temporary reduction in transmitter frequency deviation is required to optimize the system. When gate U831C is on, the audio from the splatter filter circuit is shunted by R884, which reduces the maximum deviation from ±4.6 kHz (the normal setting for deviation adjusted through IDC/DEV control R889) to ±3 kHz. The deviation bias gate can also be used as an audio boost circuit in paging or similar applications.

- 5.5.2 In paging or similar applications, deviation bias gate U831C is off when transmitting without PL/DPL tone encoding, allowing maximum deviation of ±4.6 kHz from voice alone. The gate is on when transmitting with PL/DPL, which reduces the voice audio level, and again allows ±4.6 kHz maximum deviation with both voice and PL/DPL. Shunt resistor

R884 must be changed for this application, and maximum deviation must be adjusted for transmission with or without PL/DPL, whichever is greater. Both changes are used only in custom applications.

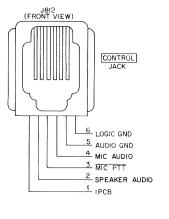

### 5.6 LOCAL SPEAKER AUDIO CIRCUIT DESCRIPTION

The buffered select audio from Select Audio Summing Amplifier U834B is applied directly to VOLUME control R876, which is accessible from the front of the control tray. The control adjusts the audio level for all local speakers connected to the base station. Select audio is also routed from the VOLUME control wiper to J800-32. The output from the VOLUME control wiper is coupled to 1/2 W Audio Buffer U834A for buffering and amplification, then to 1/2 W Speaker Audio Amplifier U836 for final amplification. A local speaker connection rated for 1/2 W into a 3.2 ohm impedance speaker is available, via tapped transformer T801, at CONTROL connector J812-2.

#### 6. EXPANSION CONNECTOR

#### 6.1 GENERAL

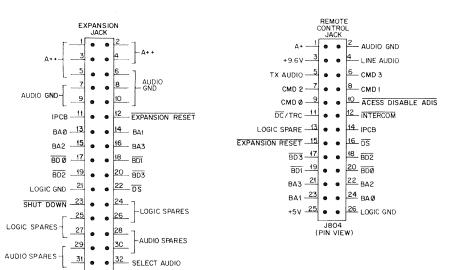

The station control tray EXPANSION connector, J800, provides interface lines which connect power, audio and digital signals between the station control board and other control modules within the station and external equipment. The connector is a 40 pin flat ribbon cable header and is accessed through the top of the control tray. There are five types of signal lines provided, as follows:

- audio lines

- dedicated logic lines

- multiplexed logic (MUX bus) lines

- power lines

- spares.

#### 6.2 AUDIO LINES

#### 6.2.1 Quad Audio (Pin 39)

The Quad Audio signal, originating on the station control module, is buffered, raw audio from the receiver quadrature detector. All receiver audio, coded squelch or other signaling tones, and receiver noise are available on this signal line. The signal is not muted by the receiver squelch circuitry. The signal line is driven by a low impedance op-amp, biased at 4.8 V dc, and the ac signal level is nominally 400 mVrms.

#### 6.2.2 RX1 Audio, (Pin 38)

The RX1 Audio signal, originating on the station control module, is receiver audio that has been deemphasized and filtered to remove coded squelch signaling tones. The audio signal is not muted by the receiver

squelch circuitry. The signal line is driven by a low impedance op-amp driver biased at 4.8 V dc, and the ac signal level is nominally 325 mVrms.

#### 6.2.3 Select Audio (Pin 32)

The Select Audio signal, originating on the station control module, is the audio input for the local speaker amplifier circuit in the Diagnostic Metering Panel option. Any of these audio signals will be present on the select audio line when it is gated on by the control circuits in the station: primary receiver audio, secondary receiver audio, transmit audio from the remote wire line, and automatic station I.D. and alarm tone audio. The signal line is connected to the wiper of the VOLUME control on the control tray front panel. The dc bias level and ac level are variable depending on the VOLUME control setting.

#### 6.2.4 Local Audio (Pin 33)

The local audio signal line is an alternate input for microphone audio to the station. It should not be used when a service microphone or handset is used for local keying. The audio on this signal line is gated to the transmit audio circuits and to the remote control module line driver circuits when a local PTT occurs. The signal line provides a signal pull-up to 9.6 V and a 560 ohm input impedance.

#### 6.2.5 TX Audio (Pin 36)

The TX audio signal, originating on the remote control module, is the inbound transmit audio from the remote control wire line. It is gated to the transmit audio circuits and the local speaker when a line PTT occurs. The signal line is driven by a low impedance opamp driver, biased at 4.8 V dc, and the ac signal level is nominally 200 mVrms.

#### 6.2.6 TX Data Audio (Pin 34)

The TX Data Audio signal is an input to the station control module which is used (in special applications) to modulate the transmitter, bypassing the control circuits, pre-emphasis, and IDC circuits. This input is dc coupled to the modulator and must be biased to 4.8 V dc. The level of the input signal must be adjusted at the signal source to assure proper transmitter deviation. When this input is used, a resistor must be added to the station control module at the circuit point labeled R898 on the schematic and overlay. When the input is not used, R898 should be omitted. Since this input bypasses the control and IDC circuits, a special FCC filing is required when it is used.

#### 6.2.7 RX2 Audio (Pin 35)

The RX2 Audio signal is an input to the station control module for audio from a second receiver. The

audio must be de-emphasized, filtered to remove coded squelch tones, and switched on and off by the second receiver squelch circuits, before being applied to the RX2 Audio line. The station control module input is ac coupled with an input impedance greater than 13k ohms. When a second receiver is used, JU11 is removed from the station control module. When the input is not used, JU11 is installed.

#### 6.3 DEDICATED LOGIC LINES

#### 6.3.1 Expansion Reset (Pin 12)

The Expansion Reset signal is a shared logic line which allows a clean, coordinated start up of the station control module and any other interconnected modules or external equipment. The Expansion Reset signal is active low at power-up, or S801 is put into the TEST position, or when activated, or when the watchdog timer resets the station control module's or when the remote control module receives a command to reset the station. Also, normal MUX bus (multiplex logic lines, described in subsequent paragraphs) operation is suspended while RESET is active low. The data strobe line, DS, is held inactive and the address and data lines do not follow their normal patterns.

#### **IMPORTANT**

While the Expansion Reset line is active low, no module except the station control module should write to the MUX bus data lines. Otherwise, the station control module may fail its self diagnostic tests, and remain reset indefinitely.

#### 6.3.2 IPCB (Pin 11)

The interprocessor communications bus (IPCB) signal line has the following characteristics:

- Single "party" line

- Half duplex

- 5 V

- Open collector

- Non-return to zero (NRZ) format

- 1200 baud serial port

Single "party" line means that only one module can transmit at a time. All modules will receive (including the one transmitting) unless the MPU "wake-up" serial port feature is used. Refer to the MC6801 8-Bit Single Chip Microcomputer Reference Manual MC6801RM(AD) for further details concerning the IPCB. Open collector drivers allow nondestructive contention.

#### 6.3.3 Shutdown (Pin 23)

The Shutdown signal line is an enable line for any auxiliary 5 V supplies connected to EXPANSION connector J800. Its purpose is to prevent the auxiliary 5 V supplies from turning on, and enabling any controlled expansion modules microprocessor to operate, unless the station control module 5 V supply comes on. This

prevention is done so that the station control module MPU is allowed to control the start-up sequence.

#### 6.4 MULTIPLEXED LOGIC (MUX bus) LINES

- 6.4.1 The multiplexed logic (MUX bus) lines consist of the following lines:

- 4 Address lines (BA0-BA3)

- 4 Data lines (BD0-BD3)

- Data strobe (DS).

All MUX bus lines are referenced to logic ground. The 4 address and 4 data lines define 16 words of 4 bits each, or 64 total bits as shown in Table 4. These bits form a multi-directional digital communications path. The bus is multiplexed to conserve interconnections (64 connections reduced to 9) and to increase future expansion capability. The data strobe and the 4 address lines are driven by the station control module. The data lines are inverted and open collector driven. This allows multiple hardware modules (and the optional diagnostic metering panel) to drive the same bit in a nondestructive, wired "OR" fashion.

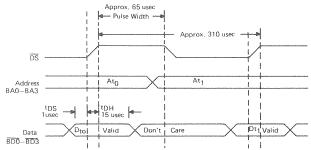

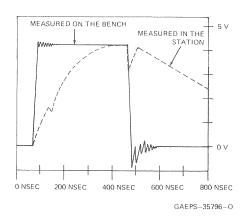

tDS is Data Set Up Time: Data must be valid at least 1 microsecond prior to  $\overline{DS}$  rising edge tDH is Data must be valid at least 15 microseconds after the rising edge of  $\overline{DS}$ . At  $_0$  is any address and  $\overline{At}_1$  is the next address  $\overline{Dt}_1$ , is the data corresponding to  $\overline{At}_1$ , etc.

AEPS-35788-0

Figure 8. MUX Bus Timing Diagram

6.4.2 The MUX bus timing diagram is shown in Figure 8. The address lines are incremented once, approximately every 310 microseconds. The address changes when data strobe is inactive ( $\overline{DS} = 1$ ). The data must be valid for 1 microsecond before the rising edge of  $\overline{DS}$ . The data must be valid for 15 microseconds after the rising edge of DS. At certain times, the MUX bus may be momentarily halted, for instance, during channel scan. The halt is in effect an extended period of inactive data strobe. The address lines will be driven, but will remain the address of the MUX bus cycle just prior to the halt. The data lines are in a "don't care" state during a halt and may be random. Any MUX bus bit which, when activated by any module other than the station control module, does not change the state of the station is called a "status only" bit. As an example of a "status only" bit, "Transmitter Activity" (TX ACT) is activated by the station control module whenever the transmitter has successfully keyed. But, if another module activates TX ACT, the transmitter will not key. Thus, TX ACT is a "status only" MUX bus bit. All "status only" MUX bus bits are signified in Table 4 by a double asterisk (\*\*).

| Table 4. MUX Bus Bit Map | Table 4. | MUX | Bus | Bit | Map |

|--------------------------|----------|-----|-----|-----|-----|

|--------------------------|----------|-----|-----|-----|-----|

| Address On<br>BAØ-BA3 | BD3       | BD2      | BD1                                     | BD0        |

|-----------------------|-----------|----------|-----------------------------------------|------------|

| 0                     | SP XMT    | SCAN     | T ALM DS                                | S ALM DS   |

| 13.13.40              | RPT PTT   | LINPTT   | LOC PTT                                 | INTCOM     |

| 2                     | TX PL DS  | TX ACT** | RX2 ACT                                 | RXI ACT    |

| 3                     | RX PL DS  | R1 PL DT | R1 SQ LV                                | R1 UN SQ** |

| 4                     | R2 MUTE   | R2 PL DT | R2 SQ LV                                | R2 UN SQ** |

| 5                     | GD TN DT  | AUX DET  | RPT KD                                  | RPT USQ**  |

| 6                     | ACC DIS** | EX DA DT | DVP SEL                                 | DVP C/C    |

| 7.00                  | *         | *        | *                                       |            |

| 8                     | TX RX C8  | TX RX C4 | RX C2                                   | TX RX C1   |

| 9                     | AUX C8    | AUX C4   | AUX C2                                  | AUX CI     |

| 10                    | *         |          | * * * * * * * * * * * * * * * * * * * * |            |

| -11                   |           |          |                                         | 1.00       |

| 12                    | RW4 OVG   | RW3 SYN  | RW2 PA                                  | RWI BAT    |

| 13                    | RWC8      | RWC7     | RWC6                                    | RWC5       |

| 14                    | FWC4      | FWC3     | FWC2                                    | FWC1       |

| 15                    | FWC8      | FWC7     | FWC6                                    | FWC5       |

<sup>\*</sup> currently unassigned

#### 7. MAINTENANCE AND TROUBLESHOOTING

#### 7.1 SELF DIAGNOSTIC ROUTINES

#### 7.1.1 General

The station control board features selfdiagnostic routines that make it possible to troubleshoot the digital circuits with standard bench test equipment (e.g., oscilloscope) in most cases. The board is equipped with a self-diagnostic routine that it performs when the station is first powered up, or whenever S801 (on the front panel) is put into the TEST position. The routine checks the integrity of MPU U801, program EPROM U804, Code Plug U803, the MUX bus read/ write circuits, and the serial port (IPCB) read/write circuits, in that order. If any of these basic blocks fail the self test, the MPU flashes the TEST LED repeatedly, as specified number of times (one, two, three, or four times), to indicate the failure that was discovered. It then waits about 1.5 seconds and resets the board by failing to tickle the watchdog circuits. Refer to the Watchdog Timer paragraphs in this section of the manual. When the watchdog circuit resets the board, the TEST LED flashes once, with a flash that is shorter than the failure indication flashes. After the watchdog circuit resets the board, the diagnostic routine is repeated. If the board fault remains unchanged, the routine locates it again, flashes the TEST LED, and resets the board again. The result is that the board sends a sequence of flashes, a short flash, another sequence of flashes, a short flash, etc. The interpretation of the TEST LED indications is given in the Self-Diagnosed Failures paragraphs in this section of the manual.

7.1.1.2 The station control board may fail in such a way that the program routines cannot be run,

including the power-up self diagnostic routine described previously. This indicates a major digital circuit failure. The watchdog circuits aid in determining these failures, yet keeps the station in a benign state until the program routines are again running correctly. When this type of failure occurs, the TEST LED is on steadily, or else flashing at a rapid rate (many times per second). Troubleshooting this type of failure is described in the Watchdog Reset Failure paragraph in this section of the manual.

7.1.1.3 Another possible failure is associated with EX-PANSION connector J800, termed Expansion Reset failure. The expansion drive circuits on the station control board work with a limited total length of flat cable and a limited number of external modules (including any remote control board). If a capacitive load in excess of 288 picofarads, including the capacitance of the flat cable and all integrated circuit loads, is attached to the Expansion Reset line, the board may reset at the end of the power-up self-diagnostic routine. At the end of the routine, the MPU (U801-16) Expansion Test signal switches from low to high and the Expansion Reset line also switches from low to high. The low-to-high transition of the Expansion Reset line is slowed down by excessive capacitance on the line, allowing C879 in the Reset Arbiter circuit to charge up and reset the MPU U801. If the MPU is reset in this manner, then the power-up self-diagnostic routine is repeated and the Expansion Reset failure is also repeated. Indication of this failure is a series of short flashes on the TEST LED, spaced about 2 seconds apart. Excessive loading of the EXPANSION connector J800 should be carefully avoided when adding expansion modules to the control circuits.

#### 7.1.2 Watchdog Reset Failure

This type of board failure is indicated when the TEST LED is on steadily, or else flashing at a rapid rate (many times per second). When this major digital circuit failure indication is seen, the following procedure should aid in finding the failed circuit.

Step 1. Use an oscilloscope in the dc coupled mode of operation, to look at the signal at the reset (RES) pin of the MPU, U801-6. The normal signal at this pin is always high. A series of low pulses, of 2 milliseconds duration, approximately, occurring every 10 milliseconds to 250 milliseconds, indicates a type of reset caused by the MPU watchdog circuit when it finds a fault in the series of MPU tickle pulses. If this type of signal is present at U801-6, proceed to Step 2. If the signal at U801-6 is always low, the fault is probably in the reset arbiter circuits, proceed to the Reset Arbiter paragraphs in this section of the manual.

Step 2. Look at the signal at the watchdog tickle (WDT Tickle) pin of the MPU, U801-17. The signal should be high during the short reset pulse. The signal should switch low within 10 seconds of the time that

<sup>\*\*</sup> status only bits

reset pin (U801-6) switches high. After this point, a high pulse should occur approximately every 53 milliseconds. If the WDT Tickle signal does not switch low after the reset pulse, this indicates that the board is failing at the beginning of the self-diagnostic routine. The board fault is probably in one of four areas: either MPU U801 is faulty, program EPROM U804 is faulty, Address Latch U802 is faulty, or there is a short circuit on one of the MPU address or data lines. Proceed to Step 6. If the WDT Tickle signal does go low after the reset signal, then either the WDT Tickle signal pulses are not spaced properly (approximately 53 milliseconds apart), or there is a failure in the watchdog timer circuitry. To troubleshoot this type of failure, proceed to Step 3.

Step 3. When WDT Tickle pin U801-17 goes low, U814-13 should switch high, making U824-10, -8, and U814-9 all high. Look for these signals to occur before proceeding. If they do not, look for some fault causing this malfunction.

Step 4. Check the signal at U806-5. It should go high when WDT Tickle pin U801-17 goes low, and stay high for approximately 9 to 21 milliseconds, and then switch low until the WDT Tickle signal switches from high to low again. If the WDT Tickle signal goes high sometime before U806-5 goes low, then both pins U823-13 and U823-12 are high making U823-11 low. This will reset the MPU via U814A and U814B. This action indicates that the self-diagnostic routines are not running properly. Proceed to Step 7.

Step 5. Check U814-13 again. If this pin is staying high for more than 80 milliseconds before switching low, this indicates that the self-diagnostic routines are not running properly. Proceed to Step 7.

Step 6. Look at the E (Enable) pin U801-40. The signal on this pin should be a square wave that is low for 408 nanoseconds and high for 408 nanoseconds. If this signal is not present, or has the wrong duty-cycle, check the supply lines to the MPU and the connections to crystal Y801 and capacitors C801 and C802. If all these connections are correct and the proper signal is not present, replace MPU U801.

Step 7. Look at Address Stobe (AS) pin U801-39. The signal on this pin should be a square wave that is high for 200 nanoseconds and low for 600 nanoseconds. If this pin is not changing, or has the wrong duty-cycle look for a short circuit on the line. If there is no short, either MPU U801 or Address Latch U802 is defective.

Step 8. Look at: the High-Order Address pins U801-22 through -29; the Low-Order Address pins U802-2, -5, -6, -9, -12, -15, -16, and -19; and the data pins at U801-30 through -37. If any of these pins are not changing state (are either always high or always low) look for a short circuit on that line.

Step 9. Look at MPU programming pins U801-8 and U801-10. When U801-6 goes low, these pins should also

be low. When U801-6 switches high, the pins also switch high, momentarily. If these pins do not go low, check programming diodes CR801 and CR803. MPU U801-6 can be forced low by putting S801 to the TEST position on the front panel.

Step 10. If none of the previous steps reveals a fault, then probably either Program EPROM U804 or MPU U801 is damaged and should be replaced. Return to Step 1.

#### 7.1.3 Self-Diagnosed Failures

Certain station control board faults are indicated by a series of 1, 2, 3, or 4 flashes of TEST LED DS807, followed in about 1.5 seconds by a short flash (the MPU resetting itself), followed about 4 seconds later by another series of 1 through 4 flashes, etc. This recurring pattern indicates that the self-diagnostic routine is running and is detecting a fault in the station control board circuits. The meaning of the different sets of flashes is as follows:

#### One Flash —

This indicates that either MPU U801 or Program EPROM U804 is defective and should be replaced.

#### Two Flashes —

This indicates that Code Plug U803 is defective and should be replaced.

#### • Three Flashes —

This indicates that the MUX bus is not operating properly. The self-diagnostic routine determines this by writing a certain address anr data pattern to the MUX bus and reading the same data back. If the read or write circuits on the station control board fail, the routine indicates the failure. If one of the MUX bus lines on J800 is shorted, or if another module connected to the MUX bus lines fails and shorts one of these lines, then the routine indicates this fault also. Note that during the self-diagnostic routine, MPU Expansion Test pin U801-16 is low, which causes the Expansion Reset signal on J800-12 to be low. This low should disable all modules that are connected to J800 from writing outputs to the MUX bus lines, since writing to the lines would cause a fault condition during the self-diagnostic routine.

The self-diagnostic routine has an added feature to aid in troubleshooting the MUX bus lines when a MUX bus fault is indicated. If the collector of Q803 is shorted to ground with a jumper, the watchdog timer is disabled, preventing a watchdog reset to the MPU. When this is done, the self-diagnostic routine writes a fixed pattern of data to the address and data lines of the MUX bus via MUX bus Write Latch U811. The BAØ output at U811-2 should be a square wave that is

low for 45 microseconds then high for 45 microseconds, then low again. Address line BA1 at U811-5 is also a square wave signal changing at half the rate of BAØ (i.e., high for 90 microseconds then low for 90 microseconds). Each subsequent address or data line on U811 is a square wave at half the rate of the previous line (i.e., BA2 is 180 microseconds; BA3 is 360 microseconds; WDØ is 720 microseconds; etc.). With this fixed pattern, the MUX bus read and write circuits and the MUX bus lines on J800 can be checked with an oscilloscope.

#### Four Flashes —

This indicates that interprocessor communication bus (IPCB) J800-11, J804-14, or J812-1 is not operating properly. The self-diagnostic routine determines this by writing a string of high and low levels to the IPCB and reading the string back. If the read and write circuits fail or if the IPCB line on J800-11 is shorted, the self-diagnostic routine indicates a failure.

The self-diagnostic routine has another added feature to aid in troubleshooting the IPCB circuits when a fault is indicated. If the collector of Q803 is shorted to ground with a jumper, as described previously, the self-diagnostic routine writes a series of alternating high and low levels to the IPCB line via IPCB Out pin of the MPU, U801-12. The line continues to switch from high to low indefinitely until the MPU is again reset. With this continuous signal coming from the MPU, the IPCB read and write circuits can be checked with an oscilloscope.

#### 7.1.4 Reset Arbiter

The following procedure describes and examines faults that are indicated when reset pin U801-6 of the MPU is always low.

Step 1. Look at the Expansion Reset signal on U826B-4 or J800-12. If this signal is always low, disconnect any external connection to J800, and remote control connector J804. If this removes the fault, and the station control board comes out of reset, then check for a short on the disconnected items.

Step 2. If Step 1 does not solve the problem, or no short is found, check the Expansion Test signal at U801-16. This signal should always be high if the MPU is always reset. Also check that U826C-6 is low, and that pull-up resistor R882C (by Q705 collector) on the Expansion Reset line is connected.

Step 3. If the Expansion Reset signal is high, but the MPU Reset pin U801-6 is low, then look for a fault in the logic circuitry between those points: U822D, U823B, U826C, U822E, U823C, and Q802.

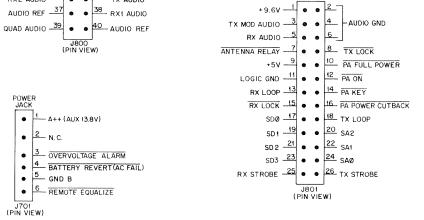

### 7.2 STATION CONTROL INPUT/OUTPUT (RADIO INTERFACE J801) SIGNALS

#### 7.2.1 General

7.2.1.1 The MPU communicates with the RF Tray via radio interface connector J801, to the remote control board via remote control connector J804, and to any expansion modules via EXPANSION connector J800. The MUX bus address and data lines, the IPCB line, and the EXPANSION RESET line are located on J800 and J804. Troubleshooting procedures for these lines are explained in the preceeding paragraphs. Signals for the INTERCOM and ACCESS DISABLE function and the remote control Command lines are located on J804.

7.2.1.2 The radio interface connector J801 routes signals used for loading the transmit and receive synthesizers, the PA Key command, the Antenna Relay, and command, and the PA Power cutback command. Troubleshooting procedures for these signals are explained in the following paragraphs. There are also signals on J801 that indicate that the synthesizers are locked and that the PA is on and at full power. These functions are displayed on the LED's located on the front panel of the Control Tray. Although these function displays are located on the control tray, the actual circuits represented are located on the Uniboard in the RF Tray. If a failure of one of these functions is indicated by the LED's, consult the troubleshooting procedure for the Uniboard. For example, if the RX LOCK LED is off, this indicates that the receiver synthesizer, located on the Uniboard, is out of lock.

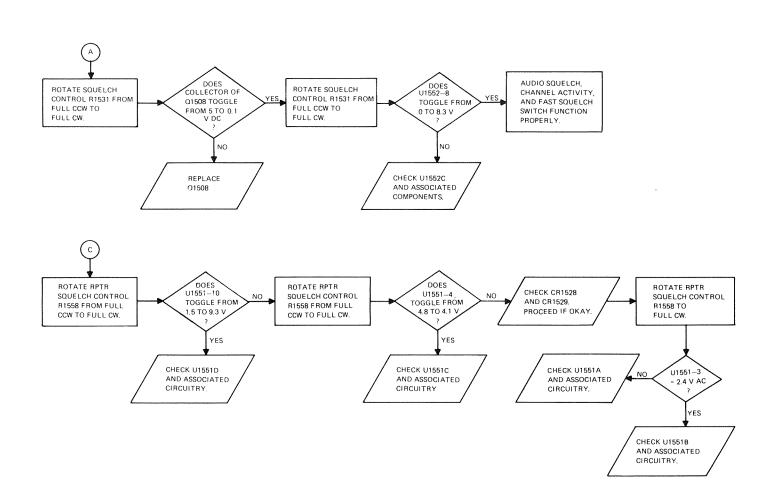

#### 7.2.2 Synthesizer Loading Lines

7.2.2.1 The synthesizers are loaded with data sent from the station control board via J801. The data is sent in packets, of approximately 2 milliseconds duration, with the packets spaced from 5 to 10 milliseconds apart on the SAØ, SA1, SA2, SDØ, SD1, SD2, and SD3 pins. While the packets are being sent, each line exhibits a number of transitions between high and low logic levels. Between the packets, the lines hold one state (either high or low). Figures 9a and 9b are representative of the type of signals to expect.

7.2.2.2 The synthesizer data is actually loaded when the transmit and receive strobe pulses, TX Strobe and RX Strobe, are sent by the station control board, via J801, to the appropriate synthesizer. Seven pulses occur on each strobe line during each packet of synthesizer data. The strobe pulse duration is very short, from about 450 nanoseconds to 1 microsecond long. Figures 10a and 10b are representative of the packets of strobe pulses and of one strobe pulse on an expanded scale.

b. Normally High

Figure 9.

Typical Waveforms for Synthesizer Loading Lines

a. Strobe Pulses

b. One Strobe Pulse

Figure 10.

Typical Waveforms for Synthesizer Strobe Lines

7.2.2.3 To assure that the station control board is loading the synthesizers properly, it is only necessary to assure that the synthesizer address and data lines are changing state and that the synthesizer strobe pulses are occurring. It is not necessary to check that the data itself is correct. The data is located in the code plug and the validity of code plug data is assured by the self-diagnostic routine that the station control board performs when the station is powered up or when S801 is put into the TEST position.

#### 7.2.3 PA Key Signal

The PA Key Control signal is generated by the MPU at pin U801-15, and is controlled by two failsafe circuits. The first failsafe circuit is U824B. If the MPU watchdog circuit detects a failure, the Delayed Reset

signal from U806A-4 prevents a PA Key signal by applying a low signal to U824B-5. The second failsafe circuit is Synthesizer Failsafe U818A. If the transmit synthesizer comes out-of-lock anytime during a PA key operation (TX Lock line switches high), the Synthesizer Failsafe circuit prevents a PA Key signal until the end of all current push-to-talk commands, and until the synthesizer locks again. When the TX Lock line is high, U818A-4 is low, which causes U818A-5 to switch high. This causes U826D-8 to switch low and turns Q804 off, ending the PA Key signal. Pin U826D-8 remains low until the next time the MPU issues a new PA Key Control command, which causes U818A-3 to switch from a low to a high state.

#### 7.2.4 Antenna Relay Signal